1

Изобретение относится к области вычислительной техники и может быть использовано при проектировании операционных автоматов цифровых вычислительных устройств.

Известные суммирующие устройства, содержащие в каждом разряде матрицу суммы и переноса из магнитных элементов с прямоугольной петлей гистерезиса, прощитых щинами записи по строкам, парами щин считывания по столбцам, шинами суммы-переноса «единицы и «нуля, шиной опроса, схемы разделения тока, ключи, формирователи тока, усилители, логические схемы «И и схемы «ИЛИ, имеют выделенные по отношению к суммирующим схемы образования переноса.

Для уменьшения оборудования и увеличения надежности в предложенном суммирующем устройстве выход первого формирователя тока соединен с шиной записи первого, второго и пятого магнитных элементов матрицы, а другим концом эта шина связана с выходом первой схемы разделения тока, с первой шиной считывания первого, третьего и пятого магнитных элементов матрицы, а другим концом эта шина связана с выходом второй схемы разделения тока, со второй щиной считывания второго и четвертого магнитных элементов матрицы, а другим концом эта шина связана с выходом третьей схемы разделения тока. Выход второго формирователя тока соединен с шиной записи третьего, четвертого и шестого магнитных элементов матрицы, а другим концом эта шина связана со вторым выходом первой схемы разделения

тока, с первой шиной считывания второго и четвертого магнитных элементов матрицы, а другим концом эта шина связана со вторым выходом второй схемы разделения тока, со второй шиной считывания первого,

третьего и шестого магнитных элементов матрицы, а другим концом эта шина связана со вторым выходом третьей схемы разделения тока. Шина суммы-переноса «единицы, проходящая через первый, четвертый и шестой

магнитные элементы матрицы, соединена со входом первого усилителя, шина суммы-переноса «нуля, проходяшая через второй, третий и пятый магнитные элементы матрицы, соединена со входом второго усилителя. Выход первого усилителя, являющийся выходом устройства, соединен с первыми входами первой и второй схем «И, выход второго усилителя, являющийся выходом устройства, соединен с первыми входами третьей и четвертой

схем «И. Выход первого ключа соединен со входом первой схемы разделения тока, выход второго ключа соединен со входом второй схемы разделения тока и со вторыми входами первой и третьей схем «И, выход третьего

ключа соединеп со входом третьей схемы разделения тока и со вторыми входами второй и четвертой схем «И. Вход первого формирователя тока, являющийся входом устройства, соединен с третьим входом третьей схемы «И, вход второго формирователя тока, являющийся входом устройства, соединен с третьим входом второй схемы «И. Выходы первой и второй схем «И соединены со входами первой схемы «ИЛИ, выходы третьей и четвертой схем «И соединены со входами второй схемы «ИЛИ. Это позволяет совместить схемы образования суммы и переноса.

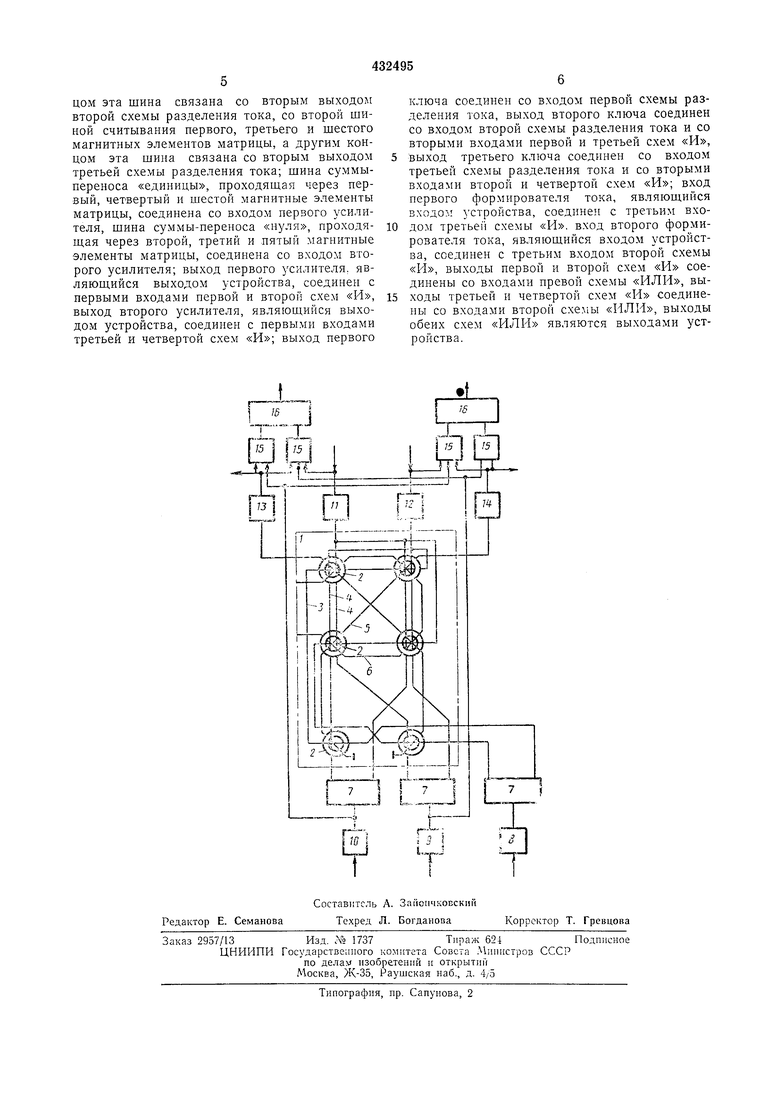

Схема устройства изображена на чертеже.

Устройство в каждом разряде содержит матрицу 1 суммы и переноса, включающую в себя магнитные элементы 2 с прямоугольной петлей гистерезиса, щины 3 записи, шины 4 считывания, щины 5 суммы-переноса, шину опроса 6, схемы разделения тока 7, ключ 8 записи, ключ 9 считывания позиции «единицы, ключ 10 считывания позиции «нуля, формирователь тока 11 позиции «единицы, формирователь тока 12 позиции «нуля, усилитель 13 позиции «единицы, усилитель 14 позиции «нуля, логические схемы «И 15 и схемы «ИЛИ 16.

Работает суммирующее устройство следующим образом.

В исходном состоянии все магнитные элементы 2 матриц 1 находятся в состоянии «О.

Для занесения в устройство параллельным кодом первого слагаемого одновременно с ноступлением позиционного сигнала цифры на вход одного из разрядных формирователей тока 12 открывается ключ 8, и два магнитных элемента 2 строки суммы, соответствующей значению аргумента, под воздействием имцульса тока записи, иротекающего по выбранной щине 3, переключаются в состояние «1.

Цифра второго слагаемого, осуществляющего последовательное считывание на выходы устройства результирующих сигналов переноса, поступает на вход тех же формирователей тока 11 или 12. На входе одного из ключей 9 считывания появляется позиционный сигнал переноса, и по шине 4, связывающей через схему разделения тока 7 выходы данного формирователя тока и ключа 9, протекает импульс тока считывания, который стремится переключить в исходное состояние элементы 2 столбца матрицы. В результате в одной из щин 5 возникает сигнал, который через усилитель 13 (14) передается на выход устройства, и один из четырех элементов 2 разрядной суммы хранит ее результирующее значение.

При правильной кодовой структуре цифры переноса на входе и соответствии веса позиции результирующего сигнала на выходе матрицы комбинации аргументов срабатывает одна из двух схем «И 15 и посредством схемы «ИЛИ 16 устанавливает на входе ключа 9 (10), к которому согласно веса позиции она подключена, разрешающий сигнал. Процесс распространения перепосов и образования

сумм продолжается в сторону мг:триц clapщих разрядов.

Наличие сигнала переноса из матрицы старшего разряда свидетельствует о правильности функционироваипя устройства.

Присутствие или oicyiciBHe позиционных сигналов любого нз аргу.мелтов одновременно на двух соответствующнх входах разрядной матрицы суммы и переноса приводит к нарущению кодовой структуры результирующего нереноса. Поступлепие двух разрещающих спгналов на входы 9 и 0 запрещает срабатыванию любой нз схем «li 15 - распространению переноса, что влечет за собой грекращение суммирования.

При совпадении разрядных значений трех аргументов результирующий сигнал переноса считывается с одного из двух дополнительных элс.ментов 2 матрицы 1, которые устанавливаются в состояние «Ь импульсом тока записи соответствующей строки суммы. Сигналы возникают на обеих шинах 5 (один из них является следствием образования суммы, другой - с дополнительного элемента). Истинг.ый сигнал переноса выделяется одной из выходных двухвходовых схем «И 15.

Импульс тока считывания в щиие опроса 6, последовательно нрошитой через четыре первые элементы разрядных матриц суммы и переноса, перемагничивает их в исходное состояние и вызывает значение суммы на разрядные выходы устройства.

Предмет изобретения

Су.ммирующее устройство, содержащее в каждом разряде матрицу сум.мы и переноса из щести магнитных элементов с нрямоугольной петлей гистерезиса, прошитых шинами

записи по строкам, парами шин считывания по столбцам, шинами суммы-перепоса «единицы и , шиной онроса, три схемы разделения тока, ключи, формирователи тока, усилители, логические схе.чы «И и схемы

«ИЛИ, отличающееся тем, что, с целью уменьшения оборудования и увеличения надежностн, выход первого формирователя тока соединен с тиной записи первого, второго и пятого магнитных элементов матрицы, а Другим концом эта щина связана с выходом первой схемы разделения тока, с первой щиной считывания первого, третьего и пятого магнитных элементов матрицы, а другим концом эта шина связана с выходом второй схемы

разделения тока, со, второй шиной считывания второго и четвертого магнитных элементов матрицы, а другим концо.м эта шииа связана с выходом третьей схемы разделения тока; выход второго фор.мирователя тока соединей с шиной записи третьего, четвертого и шестого магнитных элементов матрицы, а другим концом эта шина связана со вторы.м выходом первой схе.мы разделения тока, с первой шиной считывания второго и четвертого

магнитных элементов матрицы, а другим кон

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО для ПАРАЛЛЕЛЬНОГО СУММИРОВАНИЯДВУХ ЧИСЕЛ | 1970 |

|

SU268498A1 |

| О ПЛТЕНТИО--<^TE]'liH4^C"Ai] | 1973 |

|

SU374604A1 |

| ЦИФРОВОЕ ВЫЧИСЛИТЕЛЬНО-ЛОГИЧЕСКОЕ УСТРОЙСТВО | 1970 |

|

SU273523A1 |

| ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО | 1969 |

|

SU255993A1 |

| УСТРОЙСТВО ПАМЯТИ и РЕГИСТРАЦИИ | 1968 |

|

SU217463A1 |

| Параллельный матричный сумматор- вычитатель | 1977 |

|

SU737950A1 |

| ЛОГИЧЕСКОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1973 |

|

SU386444A1 |

| Счетчик импульсов | 1981 |

|

SU978358A1 |

| Запоминающее устройство | 1975 |

|

SU604032A1 |

| Счетчик импульсов | 1983 |

|

SU1112576A1 |

Даты

1974-06-15—Публикация

1972-04-21—Подача