1

Изобретение относится к импульсной технике и может быть использовано в схемах управления устройствами дискретной автоматики, системах кодового радиоуправления и в импульсных системах передачи цифровой информации.

Известно устройство для синхронизации импульсов асинхронного кода, содержащее входной блок, шины подачи командного кода и тактовых импульсов, каскады сравнения, триггеры команд, каскады «И, «ИЛИ, «НЕ, элементы задержки и триггер синхронизации. Однако с помощью известного устройства невозможно решать задачу синхронизации выходного импульса со многими приходящими одновременно асинхронными сигналами.

Цель изобретения - увеличение числа одновременно синхронизируемых сигналов, изменяющихся с частотой, меньшей тактовой частоты.

Для этого входы каскада сравнения соединены с кодовыми шинами и с выходами триггеров команд, а его выход соединен через схему «НЕ с одним входом каскада «И, другой вход которого через два последовательно включенных элемента задержки соединен с шиной подачи тактовых импульсов, а выход каскада «И соединен со входом каскада «ИЛИ, выход которого соединен со входом установки в «нуль триггера синхронизации, а другой вход через элемент задержки соединен с выходом каскада «И, один вход которого соединен с единичным выходом триггера синхронизации, а другой вход через три элемента задержки соединен с шиной подачи тактовых импульсов; «единичные выходы триггеров команд соединены со входами каскада «ИЛИ, выход которого соединен со входом каскада «И, другой вход которого через элемент задержки соединен с шиной подачи тактовых импульсов, а выход - со входом установки в «единицу триггера синхронизации; «нулевой вход каждого триггера команд соединен с выходом соответствующего каскада «И, один вход которого соединен с шиной подачи тактовых импульсов, а другой - через каскад «НЕ - с соответствующей шиной подачи командного кода, причем «единичный вход каждого триггера команд соединен с выходом соответствующего каскада «И, один вход которого соединен с шиной подачи тактовых импульсов, а другой - с соответствующей шиной подачи командного кода.

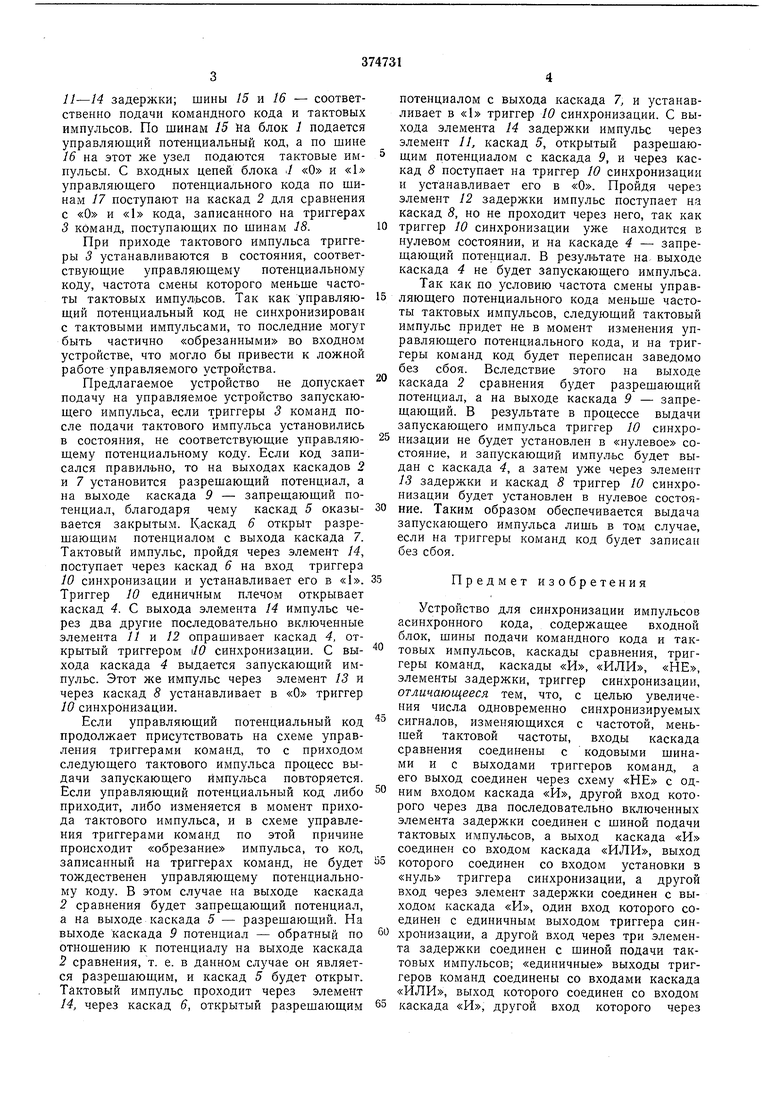

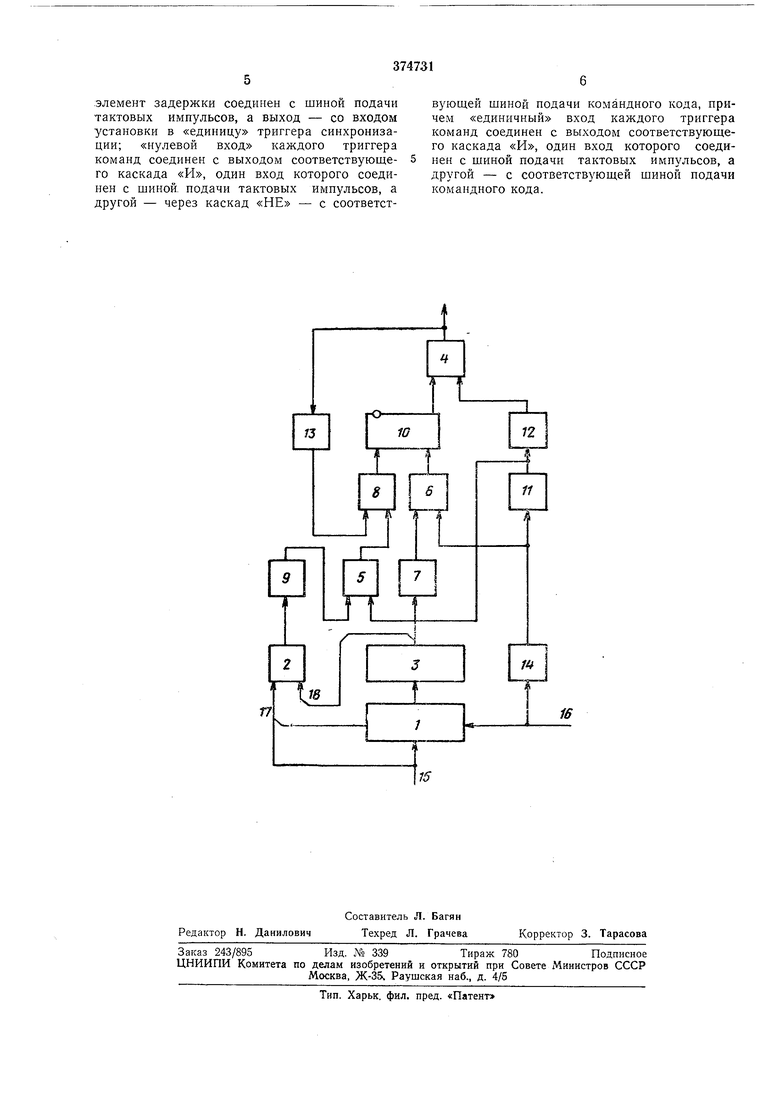

На чертеже представлена функциональная блок-схема предлагаемого устройства.

Устройство содержит входной блок /; каскад 2 сравнения; триггеры 5 команд; каскады 4-6 каскады 7, 8 каскад 9 триггер 10 синхронизации; элементы

11-14 задержки; шины 15 -л 16 - соответственно подачи командного кода и тактовых импульсов. По шинам 15 На блок 1 подается управляющий потенциальный код, а по шине 16 на этот же узел подаются тактовые импульсы. С входных цепей блока ./ «О и «1 управляюш,его потенциального кода по шинам 17 поступают на каскад 2 для сравнения с «О и «1 кода, записанного на триггерах 5 команд, поступающих по шинам 18.

При приходе тактового импульса триггеры 3 устанавливаются в состояния, соответствующие управляюшему потенциальному коду, частота смены которого меньше частоты тактовых импульсов. Так как управляющий потенциальный код не синхронизирован с тактовыми импульсами, то последние могут быть частично «обрезанными во входном устройстве, что могло бы привести к ложной работе управляемого устройства.

Предлагаемое устройство не допускает подачу на управляедюе устройство запускающего импульса, если триггеры 3 команд после подачи тактового импульса установились в состояния, не соответствующие управляющему потенциальному коду. Если код записался правильно, то на выходах каскадов 2 и 7 установится разрешающий потенциал, а на выходе каскада 9 - запрещающий потенциал, благодаря чему каскад 5 оказывается закрытым. Каскад 6 открыт разрещающим потенциалом с выхода каскада 7. Тактовый импульс, пройдя через элемент 14, поступает через каскад 6 на вход триггера 10 синхронизации и устанавливает его в «1. Триггер 10 единичным плечом открывает каскад 4. С выхода элемента 14 импульс через два другие последовательно включенные элемента 11 и 12 опрашивает каскад 4, открытый триггером 10 синхронизации. С выхода каскада 4 выдается запускающий импульс. Этот же импульс через элемент 13 и через каскад 8 устанавливает в «О триггер 10 синхронизации.

Если управляющий потенциальный код продолжает присутствовать на схеме управления триггерами команд, то с приходом следующего тактового импульса процесс выдачи запускающего импульса повторяется. Если управляющий потенциальный код либо приходит, либо изменяется в момент прихода тактового импульса, и в схеме управления триггерами команд по этой причине происходит «обрезание импульса, то код, записанный на триггерах команд, не будет тождественен управляющему потенциальному коду. В этом случае на выходе каскада 2 сравнения будет запрещающий потенциал, а на выходе каскада 5 - разрещающий. На выходе каскада 9 потенциал - обратный по отношению к потенциалу на выходе каскада 2 сравнения, т. е. в данном случае он является разрешающим, и каскад 5 будет открыт. Тактовый импульс проходит через элемент 14, через каскад 6, открытый разрешающим

потенциалом с выхода каскада 7, и устанавливает в «1 триггер 10 синхронизации. С выхода элемента 14 задержки импульс через элемент 11, каскад 5, открытый разрешающим потенциалом с каскада 9, и через каскад 8 поступает на триггер 10 синхронизации и устанавливает его в «О. Пройдя через элемент 12 задержки импульс поступает на каскад 8, но не проходит через него, так как

0 триггер 10 синхронизации уже находится в нулевом состоянии, и на каскаде 4 - запрещающий потенциал. В результате на выходе каскада 4 не будет запускающего импульса. Так как по условию частота смены управляющего потенциального кода меньше частоты тактовых импульсов, следующий тактовый импульс придет не в момент изменения управляющего потенциального кода, и на триггеры команд код будет переписан заведомо без сбоя. Вследствие этого на выходе каскада 2 сравнения будет разрешающий потенциал, а на выходе каскада 9 - запрещающий. В результате в процессе выдачи запускающего импульса триггер 10 синхронизации не будет установлен в «нулевое состояние, и запускающий импульс будет выдан с каскада 4, а затем уже через элемент 13 задержки и каскад 8 триггер 10 синхронизации будет установлен в нулевое состояние. Таким образом обеспечивается выдача запускающего импульса лишь в том случае, если на триггеры команд код будет записан без сбоя.

Предмет изобретения

Устройство для синхронизации импульсов асинхронного кода, содержащее входной блок, щины подачи командного кода и тактовых импульсов, каскады сравнения, триггеры команд, каскады «И, «ИЛИ, «НЕ, элементы задержки, триггер синхронизации, отличающееся тем, что, с целью увеличения числ,а одновременно синхронизируемых

3 сигналов, изменяющихся с частотой, меньшей тактовой частоты, входы каскада сравнения соединены с кодовыми шинами и с выходами триггеров команд, а его выход соединен через схему «НЕ с одним входом каскада «И, другой вход которого через два последовательно включенных элемента задержки соединен с шиной подачи тактовых импульсов, а выход каскада «И соединен со входом каскада «ИЛИ, выход

5 которого соединен со входом установки в «нуль триггера синхронизации, а другой вход через элемент задержки соединен с выходом каскада «И, один вход которого соединен с единичным выходом триггера синхронизации, а другой вход через три элемента задержки соединен с шиной подачи тактовых импульсов; «единичные выходы триггеров команд соединены со входами каскада «ИЛИ, выход которого соединен со входом

5 каскада «И, другой вход которого через

элемент задержки соедиЕшн с шиной подачи тактовых импульсов, а выход - со входом установки Б «единицу триггера синхронизации; «нулевой вход каждого триггера команд соединен с выходом соответствующего каскада «И, один вход которого соединен с шиной, подачи тактовых импульсов, а другой - через каскад «НЕ - с соответствующей шиной подачи командного кода, причем «единичный вход каждого триггера команд соединен с выходом соответствующего каскада «И, один вход которого соединен с шиной подачи тактовых импульсов, а другой - с соответствующей шиной подачи командного кода.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для электрического программирования блоков постоянной памяти | 1981 |

|

SU955205A1 |

| Устройство для сопряжения датчика информации с электронной вычислительной машиной | 1983 |

|

SU1133590A1 |

| Программное временное устройство | 1990 |

|

SU1762298A1 |

| Устройство для регистрации временных и информационных процессов | 1986 |

|

SU1363258A1 |

| Блок управления для запоминающего устройства | 1977 |

|

SU723679A1 |

| Дискретное фазосдвигающее устройство | 1979 |

|

SU855925A1 |

| Устройство для сопряжения вычислительной машины с магистралью обмена | 1986 |

|

SU1381519A1 |

| Устройство для контроля функционирования логических блоков | 1986 |

|

SU1327107A1 |

| Тренажер радиотелеграфиста | 1988 |

|

SU1552218A1 |

| Процессор цифровой вычислительной машины | 1979 |

|

SU1164723A1 |

15

Авторы

Даты

1973-01-01—Публикация