1

Изобретение относнтся к области вычислительной техйИкн и мюжет быть использовано для построения быстродействующих сумматоров.

Известны устройства переноса сумматора, содержащие в каждом разряде схему неравнозначности и схему «И-ИЛИ-НЕ, состоящую из двух схем «И, входы первой из которых соединены со Входами схемы неравнозначности, входы второй схемы «И соединены соответственно с выходом схемы неравнозначности и выходом переноса более младщего разряда, выходы схем «И соединены со Входами схемы «ИЛИ-НЕ, каждый (t + -|-т)-й разряд дополнительно содержит элемент «И, входы которого соединены с выходами схем неравнозначности (г-М)-го, {i-{+2)-го,... (f-|-m)-ro разрядов и с выходом переноса t-ro раз|ряда.

Схема «И должна быть составной частью схемы «И-ИЛИ-НЕ, .выдающей выходной сигнал (t + m) разряда. Но при этом сигнал 1-го разряда может оказывать влияние на работу (i-)-m) разряда только при определенной полярности («I). Ноэтому этот сигнал передается, если он соответствует, например, наличию переноса в этом разряде, .и не передается, когда он соответствует отсутствию переноса. Но этой причине любая известная схема ускорения уменьшает, например, максимально возможное время распространения сигнала переноса, но не уменьшает макснмально возможное время расирострапения снгиала отсутствия переиоса, в результате чего для каждого интервала ускорения вводят две схемы или устанавливают день переноса перед началом распространения сигналов в состояние, соответствующее, например, отсутствию переноса, после чего возможно появление новых сигналов, соответствующих только наличию переноса.

Однако использование сигнала начальной установки может вносить некоторую задержку, так как неренос распространяется только при

отсутствии этого сигнала.

Схема «И-ИЛИ-НЕ (i+m) разряда, на входы которой подаются сигналы переноса /-го и (i + m-1) разрядов полярностью «I, вырабатывает сигнал переноса на выходе нолярностью «О. Ноэтому для выработки следующего ускоренного сигнала переноса требуется введение до полнительного иивертора или исиользование выходного сигнала (I+m+l) разряда. В обоих случаях это эквивалентно тому, что

задержка, вносимая каждой схемой ускорения, равна задержке двух последовательно соединенных схем «И-ИЛИ-НЕ.

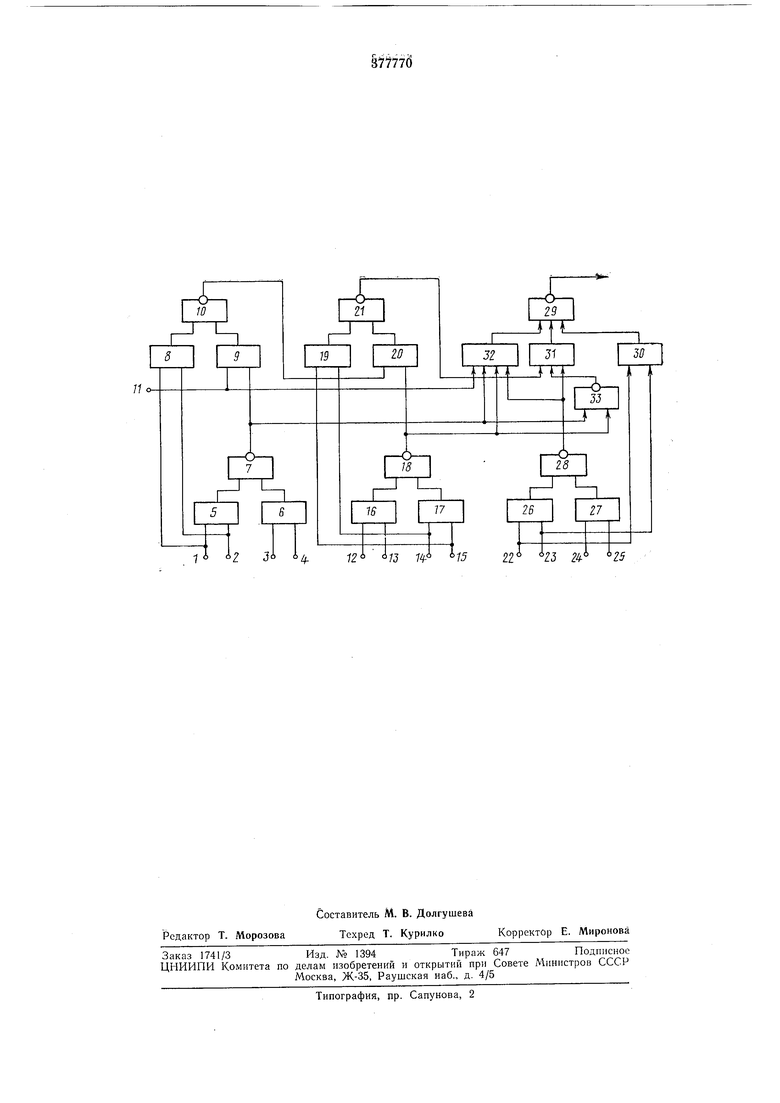

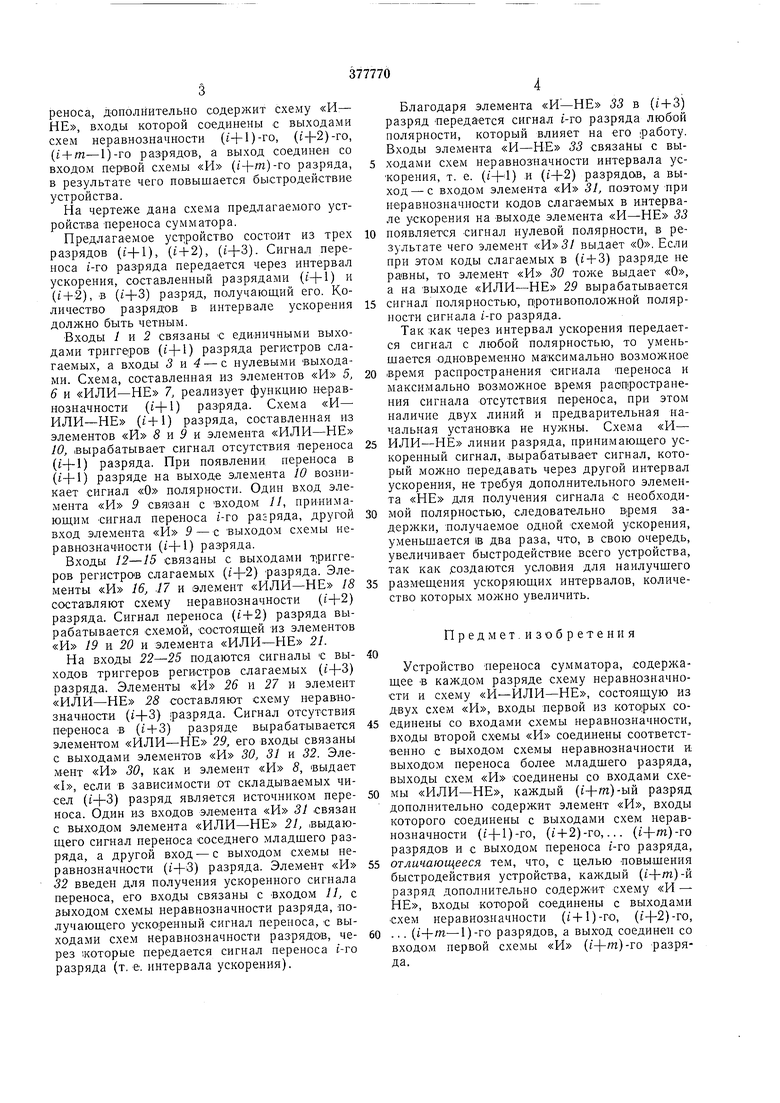

Нредлагаемое устройство переноса сумматора отличается от известного тем, что ;каждый (i + m)-fi разряд, получающий сигнал переноса, дополнительно содержит схему «И:- НЕ, входы которой соединены с выходами схем неравнозначности (t+l)-ro, (t-|-2)-ro, (i + tn-1)-го разрядов, а выход соединен со входом первой схемы «И (i-|-m)-ro разряда, в результате чего повышается быстродействие устройства. На чертеже дана схема предлагаемого устройства Переноса сумматора. Предлагаемое уст ройство состоит из трех разрядов (f-|-l), (i + 2), (i-{-3). Сигнал переноса t-ro разряда передается через интервал ускорения, составленный разрядами (t+l) и (i+2), в (i+3) разряд, получающий его. Количество разрядов в интервале ускорения должно быть четным. Входы 1 и 2 связаны -с единичными выходами тригге;ров (i+l) разряда регистров слагаемых, а входы 3 т 4 - с нулевыми выходами. Схема, составленная из элементов «И 5, 6 и «ИЛИ-НЕ 7, реализует функцию неравнозначности (i+1) разряда. Схема «И- ИЛИ-НЕ (i-fl) разряда, составленная из элементов «И 5 и 5 и элемента «ИЛИ-НЕ 10, вырабатывает сигнал отсутствия переноса (t+l) разряда. При появлении переноса в (t-j-1) разряде на выходе элемента 10 возникает сигнал «О полярности. Один вход элемента «И 9 свяваи с входом 11, принимающим сигнал переноса i-ro разряда, другой вход элемента «И 9-с выходом схемы неравнозначности (i+1) разряда. Входы 12-15 связаны с выходами триггеров регистров слагаемых (i+2) разряда. Элементы «И 16, .17 и элемент «ИЛИ-НЕ 18 составляют схему неравнозначности (i+2) разряда. Сигнал переноса (i+2) разряда вырабатывается схемой, состоящей ИЗ элементов «И /9 и 20 и элемента «ИЛИ-НЕ 21. На входы 22--25 подаются сигналы с выходов триггеров регистров слагаемых (t-f3) разряда. Элементы «И 26 и 27 и элемент «ИЛИ-НЕ 28 составляют схему неравнозначности (1+3) разряда. Сигнал отсутствия переноса в (i + 3) разряде вырабатывается элементом «ИЛИ-НЕ 29, его входы связаны с выходами элементов «И 30, 31 и 32. Элемент «И 30, как и элемент «И 8, выдает «Ь, если в зависимости от складываемых чисел (t+3) разряд является источником переноса. Один из входов элемента «И 31 связан с выходом элемента «ИЛИ-НЕ 21, (Выдающего сигнал переноса соседнего младшего разряда, а другой вход - с выходом схемы неравнозначности (i+3) разряда. Элемент «И 32 введен для получения ускоренного сигнала переноса, его входы связаны с входом //, с зыходом схемы неравнозначности разряда, -получающего ускоренный сигнал переноса, с выходами схем неравнозначности разрядов, через которые передается сигнал переноса 1-го разряда (т. е. интервала ускорения). Благодаря элемента «И-НЕ 33 в (t + 3) разряд нередается сигнал i-ro разряда любой полярности, который влияет на его ;работу. Входы элемента «И-НЕ 33 связайы с выходами схем неравнозначности интервала ускорения, т. е. (i+l) и (1+2) разрядов, а выход- с входом элемента «И 31, поэтому при неравнозначности кодов слагвемых в интервале ускорения на выходе элемента «И-НЕ 33 появляется сигнал нулевой полярности, в результате чего элемент «И 5/ выдает «О. Если при этом коды слагаемых в (i + 3) разряде не равны, то элемент «И 30 тоже выдает «О, а на выходе «ИЛИ-НЕ 29 вырабатывается сигнал нолярностью, цротивоположной полярности сигнала i-ro разряда. Так :как через интервал ускорения передается сигнал с любой полярностью, то уменьшается одновременно максимально возможное время распространения сигнала переноса и максимально возможное время раопространения сигнала отсутствия переноса, при этом наличие двух линий и предварительная начальная установка не нужны. Схема «И- ИЛИ-НЕ линии разряда, принимающего ускоренный сигнал, вырабатывает сигнал, который можно передавать через другой интервал ускорения, не требуя дополнительного элемента «НЕ для получения сигнала с необходимой полярностью, следовательно время задержки, получаемое одной схемой ускорения, уменьшается IB два раза, что, в свою очередь. увеличивает быстродействие всего устройства, так как создаются условия для наилучшего размещения ускоряющих интервалов, количество которых можно увеличить, Предмет.изобретения Устройство переноса сумматора, содержащее в каждом разряде схему неравнозначности и схему «И-ИЛИ-НЕ, состоящую из двух схем «И, входы первой из которых соединены со входами схемы неравнозначности, входы второй схемы «И соединены соответственно с выходом схемы неравнозначности н выходом переноса более младшего разряда, выходы схем «И соединены со входами схемы «ИЛИ-НЕ, каждый (1+т)-ът разряд дополнительно содержит элемент «И, входы которого соединены с выходами схем неравнозначности (i-|-l)-ro, (i+2)-ro,... (t-(-m)-ro разрядов и с выходом переноса t-ro разряда, отличающееся тем, что, с целью -повышения быстродействия устройства, (1+т)-й разряд дополнительно содерж-ит схему «И - НЕ, входы которой соединены с выходами схем неравнозначности (t+l)-ro, (t-}-2)-ro, ...()-го разрядов, а выход соединен со входом первой схемы «И (i-|-m)-ro разряда. 1 { &2 Ji 44.12 15 IV 15 2.1 VJ 24 25

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО для ПЕРЕНОСА | 1971 |

|

SU296107A1 |

| Устройство для суммирования | 1977 |

|

SU734678A1 |

| АСИНХРОННЫЙ СУММАТОР | 1965 |

|

SU173033A1 |

| Устройство для умножения с накоплением | 1986 |

|

SU1310810A1 |

| Накапливающий сумматор | 1988 |

|

SU1532916A1 |

| Устройство для умножения с накоплением | 1982 |

|

SU1108087A1 |

| Параллельный накапливающий сумматор | 1986 |

|

SU1399726A1 |

| М-разрядный комбинационный сумматор | 1988 |

|

SU1580349A1 |

| Трехвходовой параллельный сумматор | 1983 |

|

SU1136150A1 |

| Устройство для формирования группового переноса в сумматоре | 1974 |

|

SU535571A1 |

Даты

1973-01-01—Публикация