1

Изобретение относится к области устройств для обработки цифровых данных и может быть использовано, в частности, в системах подготовки программ для станков с числовым программным управлением - интерполяторах.

Известно устройство ввода информации интерполятора, содержащее входной регистр числа, подключенный к одним входам накопительного блока, другие входы которого подсоединены к регистру адреса и блоку управления, а выходы - к вычислительному блоку.

В известном устройстве в накопительный блок (НБ) вначале вводят часть программы, а затем считывают из него по одному кадру (кадр - совокупность нескольких команд) до полного освобождения НБ, после чего вновь заполняют его и т. д. При таком режиме работы на выходе устройства получается задержка в формировании сигналов следующего кадра на время ввода информации в НБ, что снижает быстродействие устройства.

Описываемое устройство отличается от известного тем, что оно содержит два счетчика, разрядные выходы которых подключены к информационным входам введенных в устройство схем «И, выходы которых через схемы «ИЛИ подсоединены к регистру адреса, два дешифратора, входы которых подключены к разрядным выходам соответствующих счетчиков, а выходы - ко входам введенного в устройство блока местного управления, соответствующие выходы которого подключены к управляющим входам схем «И, входам дешифраторов и блоку управлениня.

Это позволяет повысить быстродействие устройства.

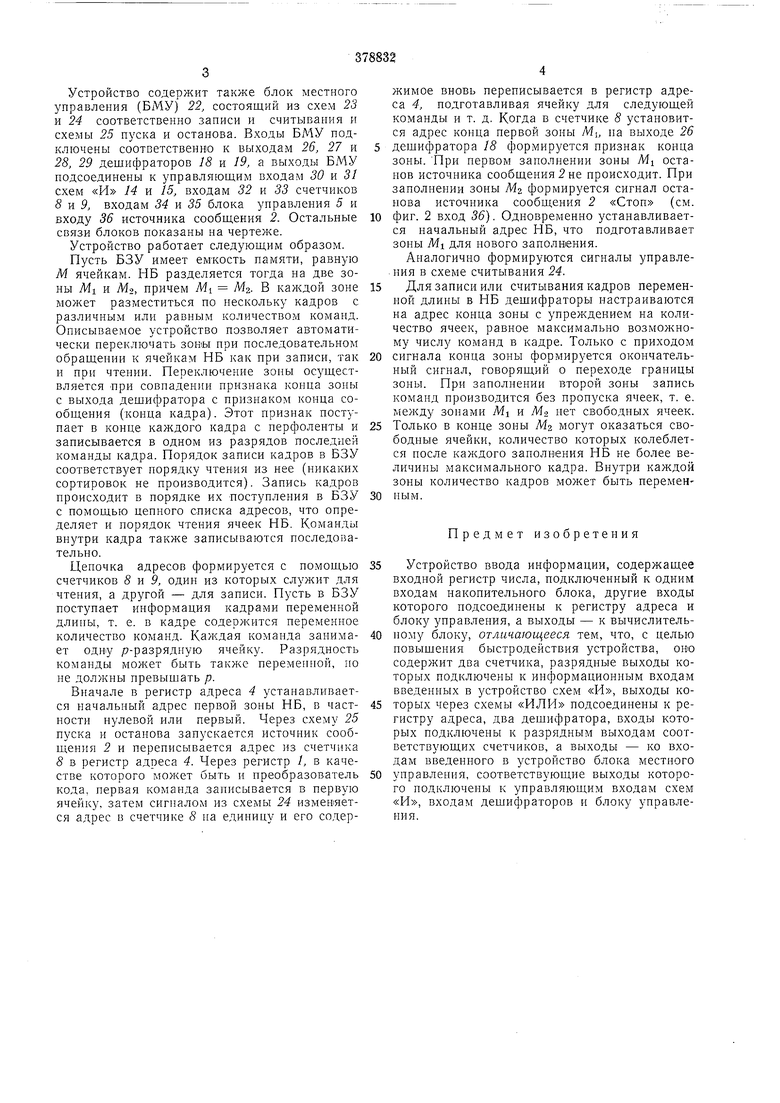

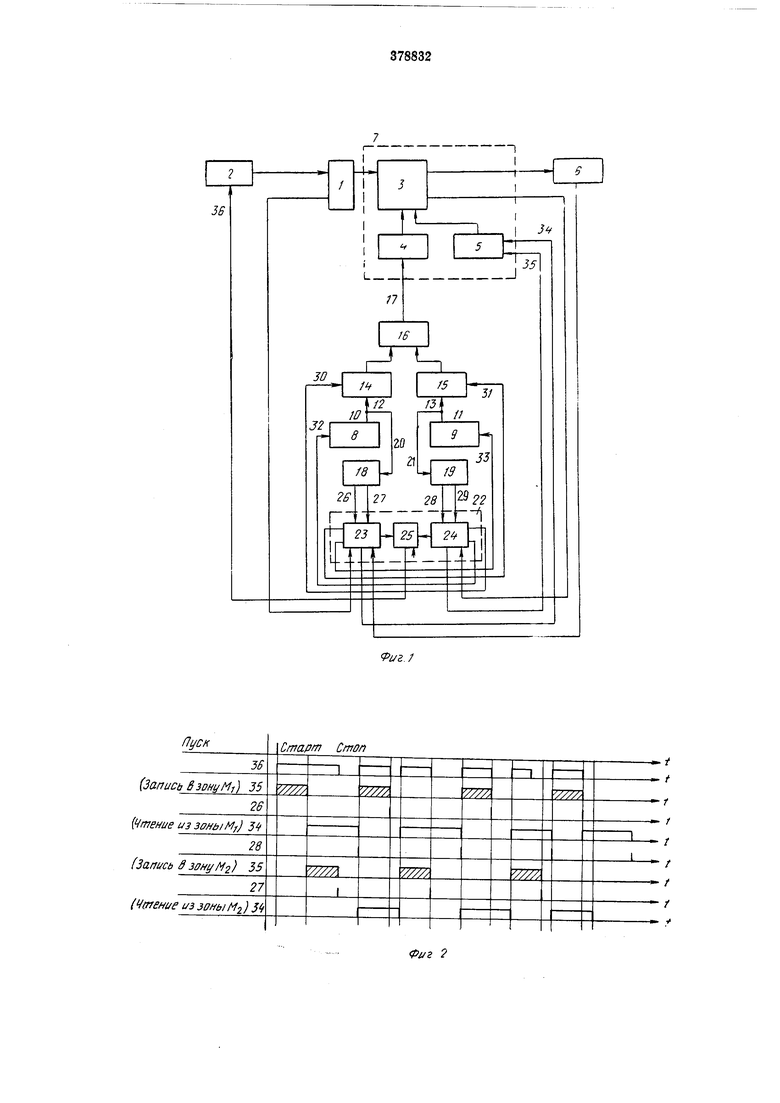

На фиг. 1 изображена блок-схема предлагаемого устройства; на фиг. 2 - временная диаграмма работы устройства.

Устройство содержит входной регистр /, входы которого подключены к источнику сообщения 2, а выходы - к одним входам НБ 3, другие входы которого подключены к регистру адреса 4, блоку управления 5, а выходы - к

вычислительному блоку 6. Блоки 3, 4 и 5 образуют буферное запоминающее устройство (БЗУ) 7. Кроме того, устройство содержит счетчики 8 и 9, разрядные выходы 10 и 11 которых подключены к информационным входам

12 и 13 схем «И 14 и 15 (показано по одной схеме «И для каждого счетчика), выходы которых через схемы «ИЛИ 16 (показана одна схема «ИЛИ) подсоединены к кодовым шинам 17 адреса регистра 4, дешифраторы 18 и

19, входы 20 и 21 которых подключены соответственно к разрядным выходам 10 и 11 счетчиков S и 9. Счетчик 8, схема «И 14 и дешифратор 18 используются при записи, а счетчик 9, схема «И 15 и дешифратор 19 - при считыв а НИИ.

Устройство содержит также блок местного управления (БМУ) 22, состоящий из схем 23 и 24 соответственно записи и считывания и схемы 25 пуска и останова. Входы БМУ подключены соответственно к выходам 26, 27 и 28, 29 дешифраторов 18 и 19, а выходы БМУ подсоединены к управляющим входам 30 и 31 схем «И 14 и 15, входам 32 и 33 счетчиков 8 -я 9, входам 34 и 35 блока управления 5 и входу 36 источника сообщения 2. Остальные связи блоков показаны на чертеже.

Устройство работает следующим образом.

Пусть БЗУ имеет емкость памяти, равную М ячейкам. НБ разделяется тогда на две зоны MI и М-2, причем MI MZ. В каладой зоне может разместиться по нескольку кадров с различным или равным количеством команд. Описываемое устройство позволяет автоматически переключать зовы при последовательном обращении к ячейкам НБ как при записи, так и при чтении. Переключение зоиы осуществляется -при совпадении признака конпа зоны с выхода дещифратора с признаком конца сообщения (конца кадра). Этот признак пост-упает в конце каждого кадра с перфоленты и записывается в одном из разрядов последней команды кадра. Порядок записи кадров в БЗУ соответствует порядку чтения из нее (никаких сортировок не производится). Запись кадров происходит в порядке их поступления в БЗУ с помощью цепного списка адресов, что определяет и порядок чтения ячеек НБ. Команды внутри кадра также записываются последовательно.

Цепочка адресов формируется с помощью счетчиков S и Я один из которых служит для чтения, а другой - для записи. Пусть в БЗУ поступает информация кадрами переменной длины, т. е. в кадре содержится переменное количество команд. Каждая команда занимает одну р-разрядную ячейку. Разрядность команды может быть также переменной, по не должны превыщать р.

Вначале в регистр адреса 4 устанавливается начальный адрес первой зоны НБ, в частности нулевой или первый. Через схему 25 пуска и останова запускается источник сообщения 2 и переписывается адрес из счетчика 8 в регистр адреса 4. Через регистр /, в качестве которого может быть и преобразователь кода, первая команда записывается в первую ячейку, затем сигналом из схемы 24 изменяется адрес в счетчике 8 на единицу и его содержимое вновь переписывается в регистр адреса 4, подготавливая ячейку для следующей команды и т. д. Когда в счетчике 8 установится адрес конца первой зоны MI, па выходе 26 дешифратора 18 формируется признак конца зоны. При первом заполнении зоны MI останов источника сообщения 2 не происходит. При заполнении зоны Мг формируется сигнал останова источника сообщения 2 «Стоп (см.

фиг. 2 вход 36). Одновременно устанавливается начальный адрес НБ, что подготавливает зопы MI для нового заполнения.

Аналогично формируются сигналы управления в схеме считывания 24.

Для записи или считывания кадров переменной длины в НБ дешифраторы настраиваются на адрес конца зоны с упреждением на количество ячеек, равное максимально возможному числу команд в кадре. Только с приходом

сигнала конца зоны формируется окончательный сигнал, говорящий о переходе границы зоны. При заполнении второй зоны запись команд производится без пропуска ячеек, т. е. между зопами MI и Мо нет свободных ячеек.

Только в конце зоны MZ могут оказаться свободные ячейки, количество которых колеблется после каждого заполнения НБ не более величины максимального кадра. Внутри каждой зоны количество кадров может быть переменным.

Предмет изобретения

Устройство ввода информации, содержащее входной регистр числа, подключенный к одним входам иакопительиого блока, другие входы которого подсоединены к регистру адреса и блоку управления, а выходы - к вычислительному блоку, отличающееся тем, что, с целью повышения быстродействия устройства, оно содержит два счетчика, разрядные выходы которых подключены к информационным входам введенных в устройство схем «П, выходы которых через схемы «ИЛИ подсоединены к регистру адреса, два дешифратора, входы которых подключены к разрядныд выходам соответствующих счетчиков, а выходы - ко входам введенного в устройство блока местного

управления, соответствующие выходы которого подключены к управляющим входам схем «И, входам дешифраторов и блоку управления.

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство сопряжения | 1989 |

|

SU1700560A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1973 |

|

SU368647A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО ИЗОБРАЖЕНИЙ | 1990 |

|

RU2047921C1 |

| Буферное запоминающее устройство | 1977 |

|

SU705517A1 |

| Устройство для вывода информации | 1983 |

|

SU1094040A1 |

| Устройство для сопряжения центрального процессора с группой арифметических процессоров | 1989 |

|

SU1702377A1 |

| Буферное запоминающее устройство | 1977 |

|

SU733017A1 |

| Устройство предварительной выборки команд | 1987 |

|

SU1561073A1 |

| 8-Битный микропроцессор | 1982 |

|

SU1161950A1 |

| Буферное запоминающее устройство | 1990 |

|

SU1783581A1 |

Авторы

Даты

1973-01-01—Публикация