1

Предлагаемое изобретение С1тносит;ся к области вычислительной техники и ,, быть использовано при построении буферных запоминающих устройств (БЗУ) каналов и устройств обмена.

Известны БЗУ, в которых используется метод перекрестно-последовательного обращения, позволяющий осуществлять двухсторонний обмен информацией и совмещать процессы ввода информации в БЗУ и вывода её из БЗУ I.

Наиболее близким к предложенному является БЗУ, содержащее накопитель, регистр числа, счетчики адресов записи и чтения, дешифратор, счетчик объема буферной зоны, регистр объема буферной зоны, блок анализа состояния буферной зоны и блок управления. Для формирования адресов буферной зоны переменного объема, задаваемого двоичным кодом, содержащим единицы, начиная с младщего разряда регистра объема буферной зоны, сигналы на единичных выводах этого регистра разрешают прохождение переносов из одноименных разрядов счетчиков aдpecoвC2J,

Недостатком известного устройства является большое количество оборудования счетчиков адресов и блока анализа состояния буферной зоны из-за необходимости управления межразрядными переносами и сравнения кодов регистра объема буферной зоны и счетчика объема при анализе состояния буферной зоны.

Цель изобретения - упрощение устройства.

Поставленная цель достигается тем, что одни, выходы регистра объема буферной зоны соединены с одноименными входами счетчика объема буферной зоны, а другие выходы этого регистра - с одноименными входами дешифратора; а также и тем, что блок анализа состояний буферной зоны содержит два элемента И, выходы которых подключены к одним выходам блока анализа состояний буферной зоны, элементы И-НЕ, входы которых подключены к входам одного

элемента И и другим входам блока анализа состояний буферной зоны, а выходы элементов И-НЕ подключены к входам другого элемента И.

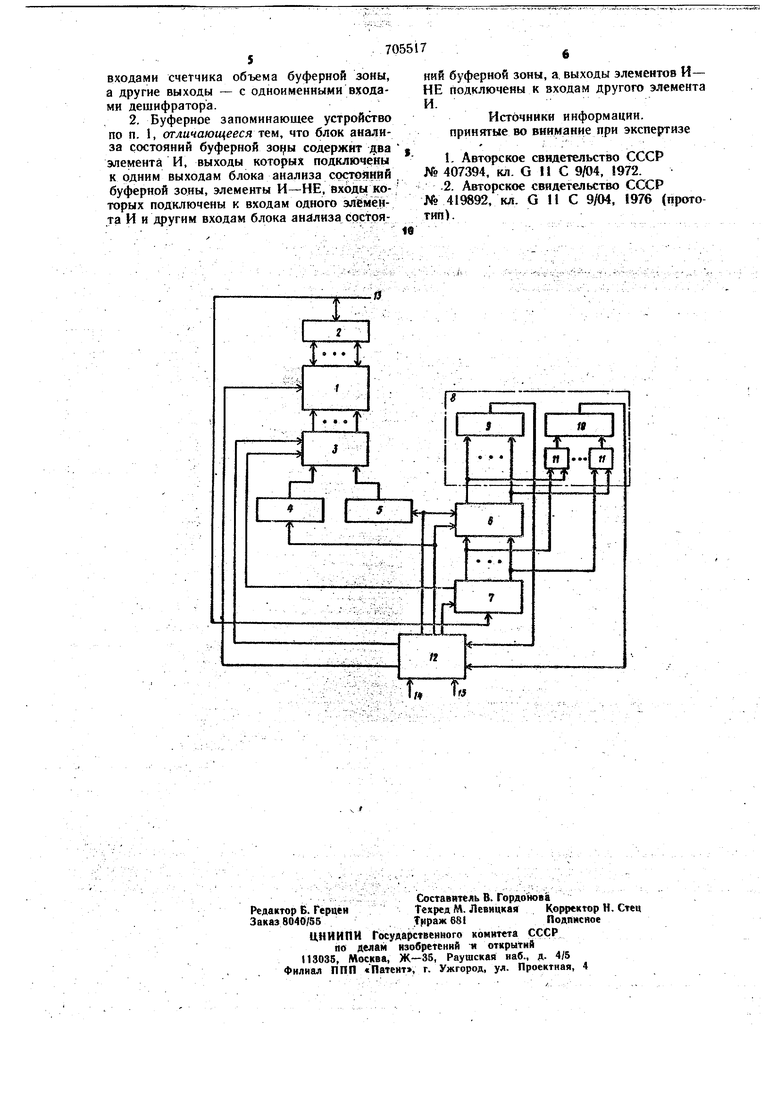

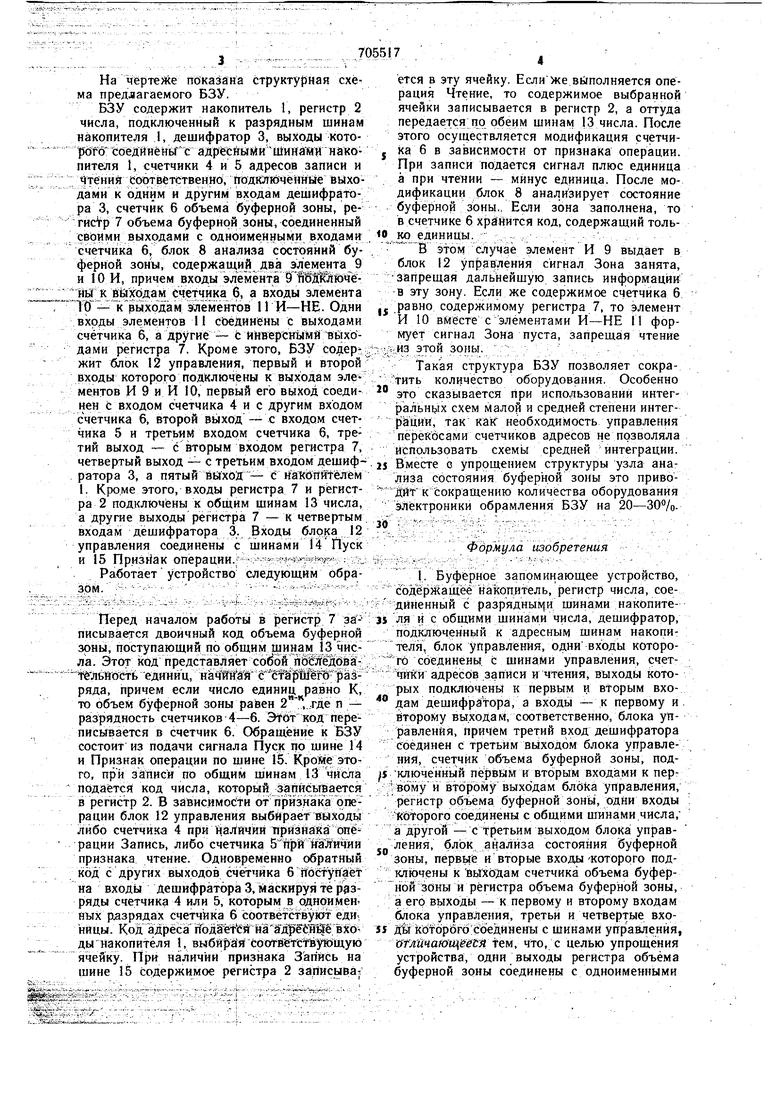

На чертейе показана структурная схема предлагаемого БЗУ.

БЗУ содержит накопитель 1, регистр 2 числа, подключенный к разрядным шинам акопителя 1, дешифратор 3, выходы котоtffo бедййёньГг аД(есйымиШин 5

пителя 1, счетчики 4 и 5 адресов записи и чтения с:рответственно7ПОД йючё 1н1 € выхоами к одним и другим в}(одам дешифратора 3, счетчик 6 объема буферной зоны, регистр 7 объема буферной зоны, соединенный сВ(ЭИми выходами с одноименными входами о счетчика 6, блок 8 анализа состояний буферной зоны, содержащий два элемента 9 и 10 И, причем входы элемента ЭИВДШЮч ёйы к ййходам счетчи а входы элемента О i- к рыходам з лементов ПИ-НЕ. Одни , ходы элементов 11 сЬеДинены с выходами чётчика 6, а другие - fc инверсными выхоами регистра 7. Кроме этого, БЗУ содержит блок 12 управления, первый и второй входы которого подключены к выходам элементов И 9 и И 10, первый его выход соеди- 10 нен с входом счетчика 4 и с другим входом счетчика 6, второй выход- с входом счетчика 5 и третьим входом счетчика 6, тре тий выход - с вторым входом регистра 7, четвертый выход - с третьим входом дешиф- jj ратора 3, а пятый вйхоЖ- с накбпйтелем 1. Кроме этого, входы регистра 7 и рёгист- ра 2 подключены к общим шинам 13 числа, а другие выходы регистра 7 - к четвертым входам дешифратора 3. Входы блока 12 управления соединены с щинами 14 Пуск и 15 Призйак операции. -лРаботает устройство следующим образом.

Ь --, , J. .г;

Перед началом работы в регистр 7 за- л писывается двоичный код объема буферной зоны, поступающий по общим шинам 13 чиса. Этот код представляет codoA поргёдовагельйбШ единиц, начШай с ctlptuerb разряда, причем если число единиц, равно К, то объем буферной зоны равен , где п - разрядность счетчиков 4-6. 3tOT код переписывается в счетчик 6. Обращение к БЗУ состоит из подачи сигнала Пуск по шине 14 и Признак операции по шине 15, Кроме этого, при записи по общим шинам 13 числа ;5 подаётся код числа, который записывается в регистр 2. В зависимоС-ги от признака операции блок 12 управления выбирает выходы ибо счетчика 4 при йаЛйчйи признака операции Запись, либо счетчика 5 при признака чтение. Одновременно обратный код с других выходов счетчика 6 поступает На входы дешифратора 3,1М1аскируя те разряды счетчика 4 или 5, которым в одноименных разрядах счетчика 6 соответствуют еди нйцы. Код адреса пода%(ейнаад { ё Шё 55 ды накопителя 1, выбйрйЖ соотвёТЬТвроЩую ячейку. При наличии признака Запйсь на шине 15 содержимое регистра 2 записыва

ется в эту ячейку. Если Же выполняется операция Чтение, то содержимое выбранной ячейки записывается в регистр 2, а оттуда передается по обеим шинам 13 числа. После этого осуществляется модификация счетчика 6 в зависимости от признака операции. При записи подается сигнал плюс единица а при чтении - минус единица. После модификации блок 8 анализирует состояние буферной зоны., Если зона заполнена, то в счетчике б хрг(йится код, содержащий только единицы. .

В этом случае элемент И 9 выдает в блок 12 управления сигнал Зона занята, запрещая дальнейшую запись информации в эту зону. Если же содержимое счетчика 6 равно содержимому регистра 7, то элемент И 10 вместе с элементами И-НЕ II формует сигнал Зона пуста, запрещая чтение из этой зоны.

Такая структура БЗУ позволяет сократить количество оборудования. Особенно это сказывается йри использовании интегральнух схем малой и средней степени интеграции, так Kaic необходимость управления перекосами счетчиков адресов не позволяла использовать схемы средней интеграции. Вместе с упрощением структуры узла анализа состояния буферной зоны это приводит к сокращению количества оборудования электроники обрамления БЗУ на 20-30%.

Фдрмула изобретения

. Буферное запоминающее устройство, содержащее йако питель, регистр числа, соединенный с разрядныл и шинами накопителя и с общими шинами числа, дешифратор, подключенный к адресным шинам накопителя, блок управления, однивходы которого соединены, с шинами управления, счетчики адресов записи и чтения, выходы которых подключен к первым и вторым входам дещифратора, а входь - к первому и. второму выходам, соответственно, блока управления, причем третий вход дешифратора соединен с третьим выходом блока управления, счетчик объема буферной зоны, подключеннУй первым и вторым входами к первому и второму выходам блока управления, регистр объема буферной зоны, одни входы Которого соединены с общими шинами числа, а другой- с третьим выходом блока управления, блок анализа состояния буферной зоны, первые и вторые входыКоторого подключены к вьГХбДам счетчика объема буферной зоны и регистра объема буферной зоны, а его выходы - к первому и второму входам блока управления, третьи и четвертые входЬ которого соединены с Шинами упрайленйя, тличающёёЪП &ы, что, с целью упрошения устройства, одни выходы регистра объёма буферной зоны соединены с одноименными

входами счетчика объема буферной зоны, а другие выходы - с одноименнымн входами дешифратора.

2. Буферное запоминающее устройство по п. 1, отличающееся тем, что блок анализа состояний буферной содержит два элемента И, выходы которых подключены к одним выходам блока анализа срстрйнйй буферной зоны, элементы И-НЕ, входы которых подключены к входам одного элемента И и другим входам блока анализа сортряний буферной зоны, а выходы элементов И- НЕ подключены к входам другого элемента

И.

Источники информации, принятые во внимание при экспертизе

i - - 1. Авторское свидетельство СССР № 407394, кл. G 11 С 9/04, 1972.

.2. Авторское свидетельство СССР МЬ 419892, кл. G II С 9/04, 1976 (прототип).

1в

| название | год | авторы | номер документа |

|---|---|---|---|

| Буферное запоминающее устройство | 1987 |

|

SU1444893A1 |

| Буферное запоминающее устройство | 1983 |

|

SU1124379A1 |

| МНОГОКАНАЛЬНАЯ СИСТЕМА ДЛЯ РЕГИСТРАЦИИ ФИЗИЧЕСКИХ ВЕЛИЧИН | 1991 |

|

RU2037190C1 |

| Буферное запоминающее устройство | 1990 |

|

SU1783581A1 |

| Буферное запоминающее устройство | 1985 |

|

SU1297115A1 |

| Буферное запоминающее устройство | 1978 |

|

SU750567A1 |

| Буферное запоминающее устройство | 1991 |

|

SU1824651A1 |

| Буферное запоминающее устройство | 1990 |

|

SU1711233A1 |

| Буферное запоминающее устройство | 1989 |

|

SU1672527A1 |

| Буферное запоминающее устройство | 1989 |

|

SU1654875A1 |

Авторы

Даты

1979-12-25—Публикация

1977-04-19—Подача