1

Изобретение относится к области вычислительной техники и может быть использовано в устройствах цифровой обработки информации.

Известен однофазный триггер по авт. св. № 348162, содержащий многоэмиттерпый транзистор, двухвходовые схемы «И и выходной усилитель.

Цель изобретения - повышение надежности работы однофазного триггера.

Для этого выход триггера соединен с базой транзистора схемы «И, эмиттер тра}1зистора которой подключен к шине тактового входа триггера и к базе транзистора другой схемы «И, эмиттер транзистора которой подсоединен к шине информационного входа триггера.

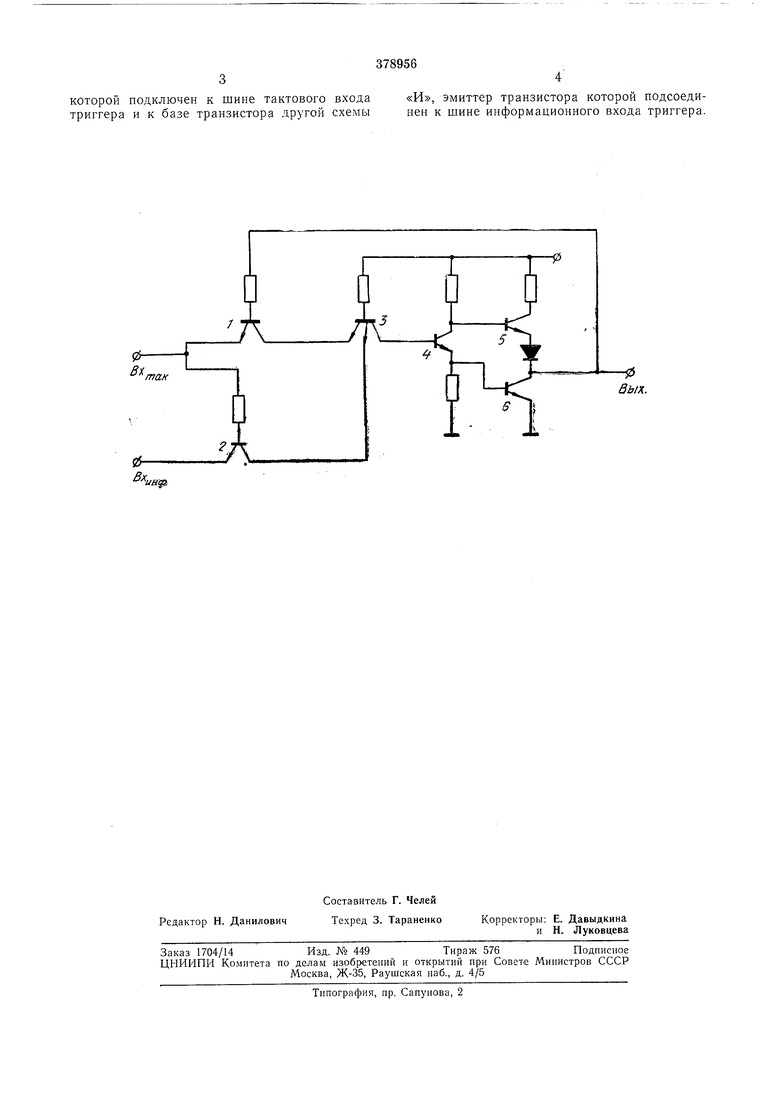

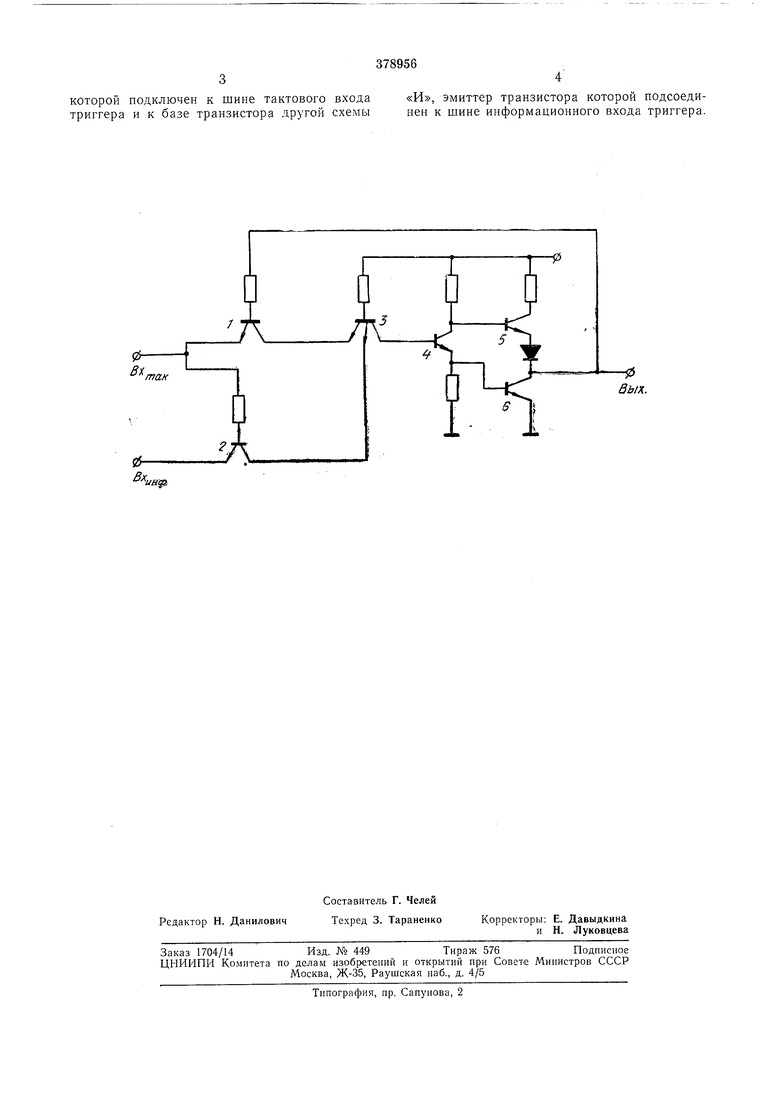

На чертеже изображена принципиальная схема однофазного триггера.

Триггер содержит схемы «И, выполненные на транзисторах 1 и 2, многоэмиттерпый транзистор 3 и выходной усилитель, выполненный на транзисторах 4, 5, 6. Выход триггера соединен с базой транзистора 1, эмиттер которого подключен к шине тактового входа триггера и к базе транзистора 2, а эмиттер транзистора 2 подсоединен к шине информационного входа триггера.

Если на тактовый и информационный входы триггера подать уровни логического нуля, транзистор / открывается, а транзисторы 2, 4,

6 закрываются, и на выходе триггера устанавливается уровень логической единицы.

Если на тактовый вход триггера подать уровень логической единицы, а на информационный вход - уровень логического нуля, то открывается транзистор 2, а транзисторы /, 4 и 6 закрываются, а на выходе триггера сохраняется уровень логической единицы. По окончании импульса на информационном входе

триггера транзистор 2 закрывается, а транзистор / открывается. При этом состояние триггера не изменяется.

Если на тактовый и информационный входы триггера подать уровни логической единицы, то транзисторы / и 2 закрываются, транзистор 4 открывается, на выходе триггера устанавливается уровень логического нуля. В момент окончания имп льса на информационном входе триггера транзистор 2

закрывается, а транзистор 1 не открывается вследствие низкого уровня напряжения на его базе, поступающего с выхода триггера, и, таким образом, триггер остается в состоянии логического нуля.

Предмет изобретения

Однофазный триггер по авт. св. № 348162,

отличающийся тем, что, с целью повышения

надежности, выход триггера соединен с базой

транзистора схемы «И, эмиттер транзистора

которой подключен к шине тактового входа триггера и к базе транзистора другой схемы

«И, эмиттер транзистора которой подсоединен к шине информационного входа триггера.

| название | год | авторы | номер документа |

|---|---|---|---|

| Интегральный динамический элемент | 1980 |

|

SU906005A2 |

| ОДНОФАЗНЫЙ ТРИГГЕР | 1973 |

|

SU399012A1 |

| Т-триггер (его варианты) | 1984 |

|

SU1226615A1 |

| Транзисторный ключ | 1985 |

|

SU1336223A2 |

| Инжекционный динамический элемент | 1981 |

|

SU1005314A2 |

| Однофазный D-триггер | 1988 |

|

SU1647855A1 |

| Формирователь центра тяжести импульсов | 1986 |

|

SU1374173A2 |

| Оптоэлектронный модуль | 1987 |

|

SU1444940A1 |

| Устройство для синхронизации воспроизведения цифровой магнитной записи | 1986 |

|

SU1337918A1 |

| Способ поиска дефектов в цифровых блоках и устройство для его осуществления | 1985 |

|

SU1260884A1 |

Авторы

Даты

1973-01-01—Публикация