1

Изобретение относится к области электросвязи и может использоваться в системах связи с асипхроппым вводом информации методами одностороннего и двустороннего стаффинга.

Известны устройства цикловой сипхронизащш, обеспечивающие последовательный поиск синхронизирующей последовательности (СК) и содержащие последовательно соединенные дещифратор СК, ключ с тактовым входом и счетчик цикла синхронизации, который управляет ключом по одному его вхОхДу непосредственно, а по другому через накопитель, причем между выходом дешифратора СК и третьим выходом счетчика цикла синхронизации включена схема «И.

Недостатком известных устройств синхронизации является большое время фиксации сбоя синхронизма, когда сбой уже произошел (3-10 циклов синхропизации). Это увеличивает время перерывов в связи, что снижает достоверность передаваемых сообщений.

В предлагаемом устройстве с целью повышения достоверности передаваемых сообщений путем уменьшения времени фиксации сбоя синхронизма меладу входом дещифратора СК и дополиительвым входом накопителя включены последовательно соединенные блок фиксации сбоев командных посылок (КП) и схема «ИЛИ, ко второму входу которой подключей выход схемы «И, а к двум другим входам блока фиксации сбоев КП подключены соответственно дополнительный выход счетчика цикла синхронизации и выход накопителя.

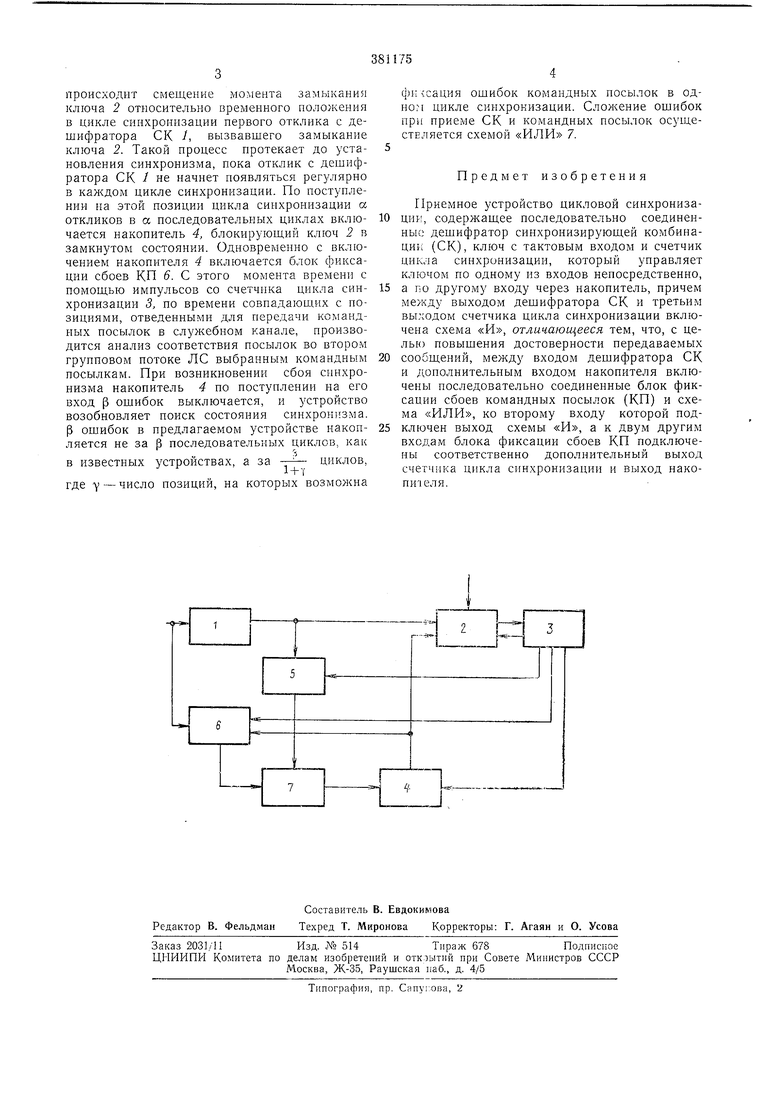

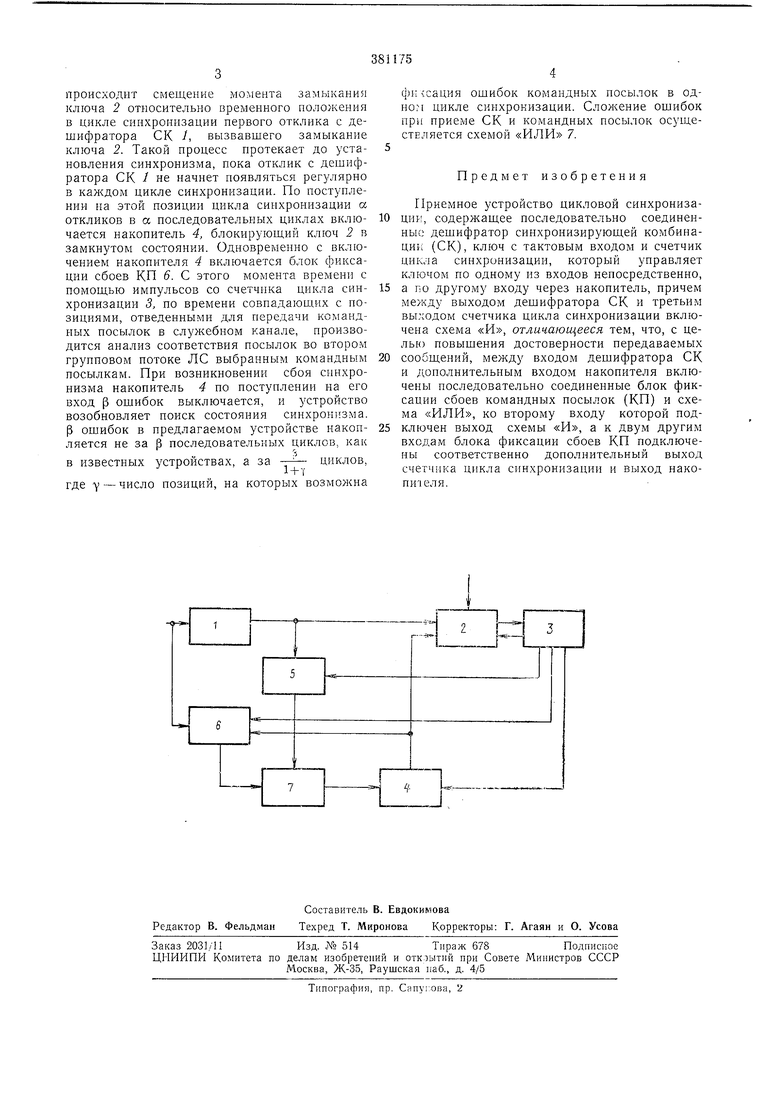

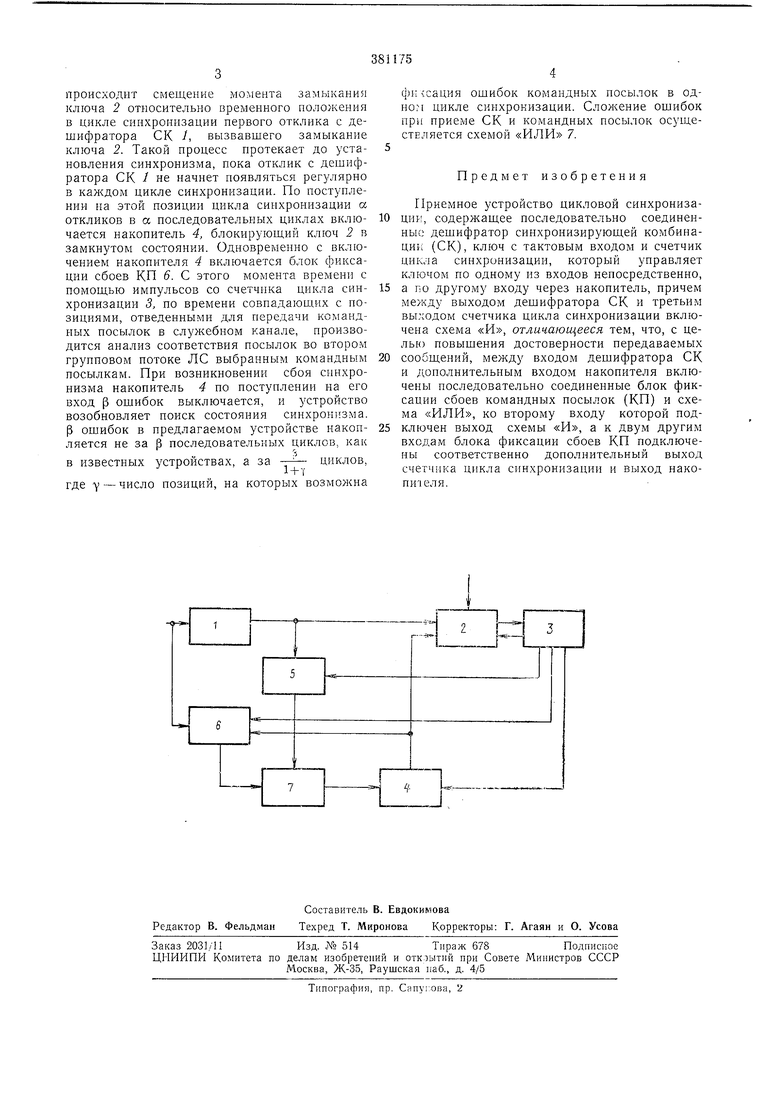

На чертеже приведена функциональная схема предлагаемого устройства.

Устройство содержит дешифратор СК , ключ 2, счетчик цикла синхронизации 3, накопитель 4, схему «И 5, блок фиксации сбоев КП 6 и схему «ИЛИ 7.

Принцип работы устройства состоит в следующем. Принятый групповой линейный сигнал (ЛС) поступает на дешифратор СК Л на выходе которого появляется отклик всякий раз, когда на его входе появляется комбинация типа СК. В режиме поиска первый же отклик дешифратора СК 1 замыкает ключ 2, который с этого момента начинает нропускать последовательность тактовых импульсов (ТИ) на вход счетчика 3, отсчитывающего интервал времени, равный циклу синхронизации. По окончании этого интервала времени импульсом со счетчика 5 ключ 2 размыкается и, если в этот момент времени с дешифратора СК 1 отклика не появляется, то ключ 2 остается разомкнутым до иоявлеиня последующих откликов. При этом тактовые импульсы в течение этого промежутка времени иа счетчик цикла синхропизации 5 не поступают, т. е.

происходит смещение момента замыкания ключа 2 относительно временного положения в цикле синхронизации нервого отклика с дешифратора СК 1, вызвавшего замыкание ключа 2. Такой процесс протекает до установления синхронизма, пока отклик с дешифратора СК 1 не начнет появляться регулярно в каждом цикле синхронизации. По поступлении на этой позиции цикла синхронизации ос откликов в а последовательных циклах включается накопитель 4, блокирующий ключ 2 в замкнутом состоянии. Одновременно с включением накопителя 4 включается блок фиксации сбоев КП 6. С этого момента времени с помощью импульсов со счетчика цикла синхронизации 3, по времени совпадающих с позициями, отведенными для передачи ксмаидиых посылок в слулсебном каиале, производится анализ соответствия посылок во второ.м грунповом потоке ЛС выбранным командным посылкам. При возникновении сбоя синхронизма накопитель 4 по поступлении на его вход р ошибок выключается, н устройство возобновляет поиск состояния синхронизма. Р ошибок в предлагаемом устройстве накопляется не за |3 последовательных циклов, как

в известных устройствах, а за циклов, где Y - число позиций, на которых возможна

фк {садия ошибок командных посылок в одно цикле синхронизации. Сложение ошибок при приеме СК и командных посылок осуществляется схемой «ИЛИ 7.

Предмет изобретения

Приемное устройство цикловой синхронизации, содержащее последовательно соединенные дещифратор синхронизирующей комбинации (СК), ключ с тактовым входом и счетчик цикла синхронизации, который управляет ключом по одному из входов непосредственно,

а по другому входу через накопитель, причем между выходом дещифратора СК и третьим выходом счетчика цикла синхронизации включена схема «И, отличающееся тем, что, с целью повышения достоверности передаваемых

сообщений, между входом дешифратора СК и дополнительным входом накопителя включены последовательно соединенные блок фиксации сбоев командных посылок (КП) и схема «ИЛИ, ко второму входу которой подключен выход схемы «И, а к двум другим входам блока фиксации сбоев КП подключены соответственно дополнительный выход счетчика цикла синхронизации и выход накопителя .

| название | год | авторы | номер документа |

|---|---|---|---|

| ПРИЕМНОЕ УСТРОЙСТВО ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 1973 |

|

SU400045A1 |

| Устройство синхронизации по циклам | 1973 |

|

SU498752A1 |

| Устройство для цикловой синхронизации | 1989 |

|

SU1778913A1 |

| УСТРОЙСТВО ДЛЯ СИНХРОНИЗАЦИИ | 2005 |

|

RU2302084C2 |

| Устройство цикловой синхронизации | 1980 |

|

SU944136A1 |

| Устройство для измерения коэффициента ошибок в цифровых трактах передачи информации | 1989 |

|

SU1674394A1 |

| Устройство для синхронизации по циклам | 1991 |

|

SU1811019A1 |

| УСТРОЙСТВО ДЛЯ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2005 |

|

RU2284665C1 |

| Адаптивный приемник относительного биимпульсного сигнала | 1988 |

|

SU1601768A1 |

| Устройство цикловой синхронизации | 1979 |

|

SU843273A1 |

Авторы

Даты

1973-01-01—Публикация