(54) УСТРОЙСТВО ЦИКЛОВОЙ СИНХРОНИЗАЦИИ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство формирования сигнала кадровойСиНХРОНизАции | 1979 |

|

SU843301A1 |

| Многоканальное устройство синхронизации и выравнивания потоков информации | 1979 |

|

SU886018A1 |

| Формирователь управляющих сигналов | 1980 |

|

SU896774A1 |

| Приемное устройство циклового фазирования | 1983 |

|

SU1085006A1 |

| Устройство для синхронизации по циклам | 1979 |

|

SU873445A1 |

| УСТРОЙСТВО ДЛЯ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2007 |

|

RU2348117C1 |

| УСТРОЙСТВО ДЛЯ СИНХРОНИЗАЦИИ ПО ЦИКЛАМ | 2002 |

|

RU2239953C2 |

| УСТРОЙСТВО ДЛЯ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2005 |

|

RU2284665C1 |

| УСТРОЙСТВО ДЛЯ СИНХРОНИЗАЦИИ ПО ЦИКЛАМ | 2003 |

|

RU2231228C1 |

| СПОСОБ СИНХРОНИЗАЦИИ КОДОВЫХ КОМБИНАЦИЙ | 2023 |

|

RU2812335C1 |

1

Изобретение относится к электросвязи и может использоваться в системах передачи и обработки цифровой информации.

Известно устройство цикловой синхронизации, содержащее первый дешифратор, выходы которого подключены к соответствуюц1им входам первого и второго элементов ИЛИ и через формирователь сигналов управления к одним из входов коммутатора, другой вход которого соединен с выходом счетчика длины цикла, вход которого соединен с тактовым входом устройства 1.

Однако устройство имеет низкую помехоустойчивость в режиме поиска синхронизма.

Цель изобретения - повышение помехоустойчивости.

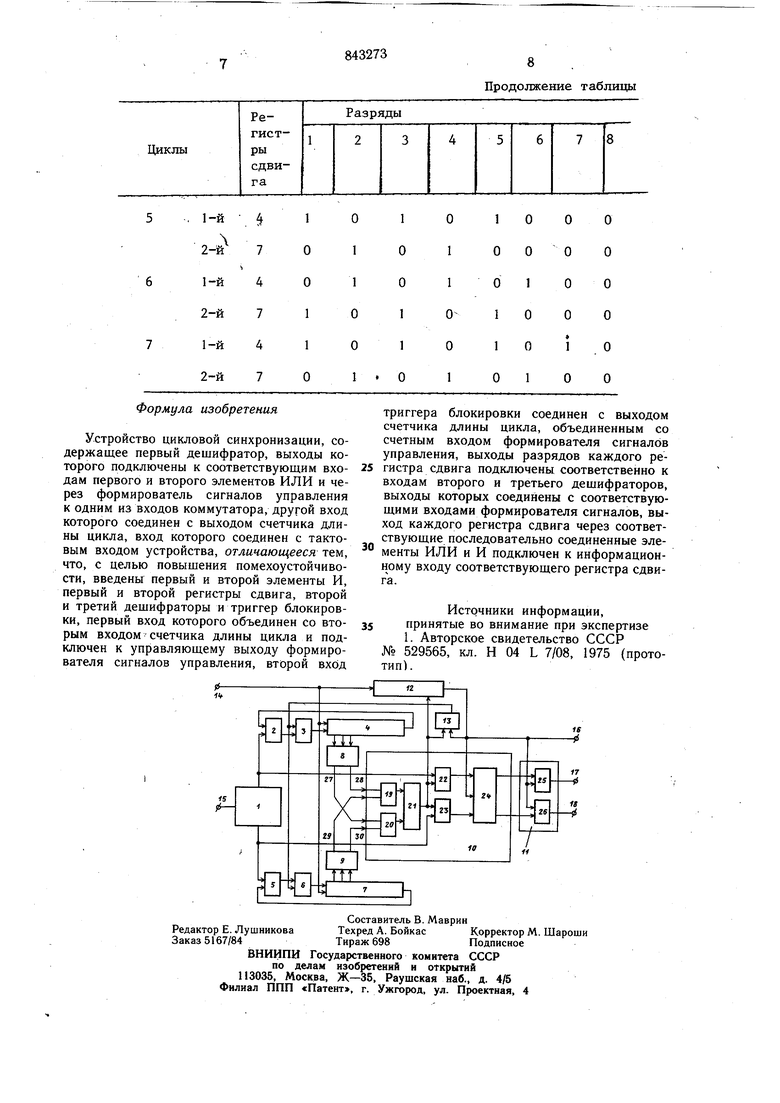

Для достижения цели в устройство цикловой синхронизации, содержаш,ее первый дешифратор, выходы которого подключены к соответствующим входам первого и второго элементов ИЛИ и через формирователь сигналов управления к одним из входов коммутатора, другой вход которого соединен с выходом счетчика длины цикла, вход которого соединен с тактовым входом устройства, введены первый и второй элементы И,

первый и второй регистры сдвига, второй и третий дешифраторы и триггер блокировки, первый вход которого объединен со вторым входом, счетчика длины цикла и подключен к управляющему выходу формирователя сигналов управления, второй вход триггера

блокировки соединен с выходом счетчика длины цикла, объединенным со счетным входом формирователя сигналов управления, выходы разрядов каждого регистра сдвига подключены соответственно к входам второго и третьего дешифраторов, выходы которых соединены с соответствующими входами формирователя сигналов управления, выход каждого регистра сдвига через соответствующие последовательно соединенные элементы ИЛИ и И подключен к информационному входу соответствую щего регистра сдвига.

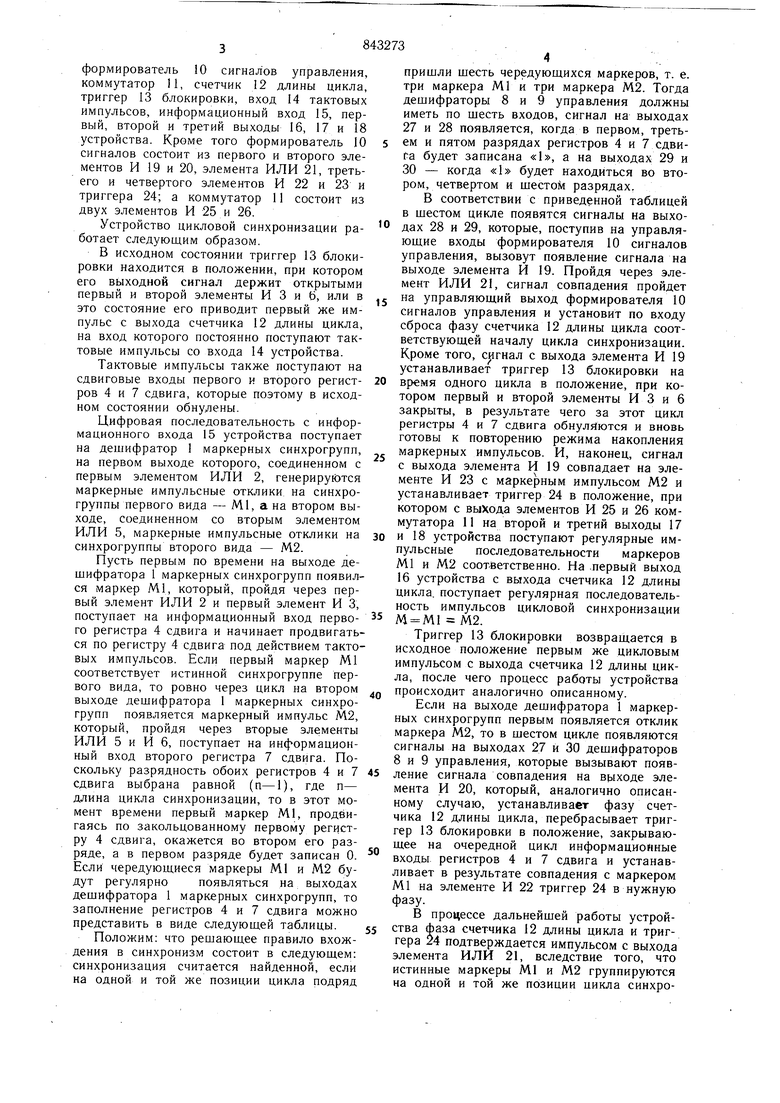

На чертеже приведена структурная электрическая схема устройства.

Устройство цикловой синхронизации содержит первый дешифратор 1, первый элемент ИЛИ 2, первый элемент И 3, первый регистр 4 сдвига, второй элемент ИЛИ 5, второй элемент И 6, второй регистр 7 сдвига, второй и третий дешифраторы 8 и 9,

формирователь 10 сигналов управления, коммутатор 11, счетчик 12 длины цикла, триггер 13 блокировки, вход 14 тактовых импульсов, информационный вход 15, первый, второй и третий выходы 16, 17 и 18 устройства. Кроме того формирователь 10 сигналов состоит из первого и второго элементов И 19 и 20, элемента ИЛИ 21, третьего и четвертого элементов И 22 к 23 и триггера 24; а коммутатор 11 состоит из двух элементов И 25 и 26.

Устройство цикловой синхронизации работает следующим образом.

В исходном состоянии триггер 13 блокировки находится в положении, при котором его выходной сигнал держит открытыми первый и второй элементы И 3 и Ь, или в это состояние его приводит первый же импульс с выхода счетчика 12 длины цикла, на вход которого постоянно поступают тактовые импульсы со входа 14 устройства.

Тактовые импульсы также поступают на сдвиговые входы первого и второго регистров 4 и 7 сдвига, которые поэтому в исходном состоянии обнулены.

Цифровая последовательность с информационного входа 15 устройства поступает на дешифратор 1 маркерных синхрогрупп, на первом выходе которого, соединенном с первым элементом ИЛИ 2, генерируются маркерные импульсные отклики на синхрогруппы первого вида - Ml, а на втором выходе, соединенном со вторым элементом ИЛИ 5, маркерные импульсные отклики на синхрогруппы второго вида - М2.

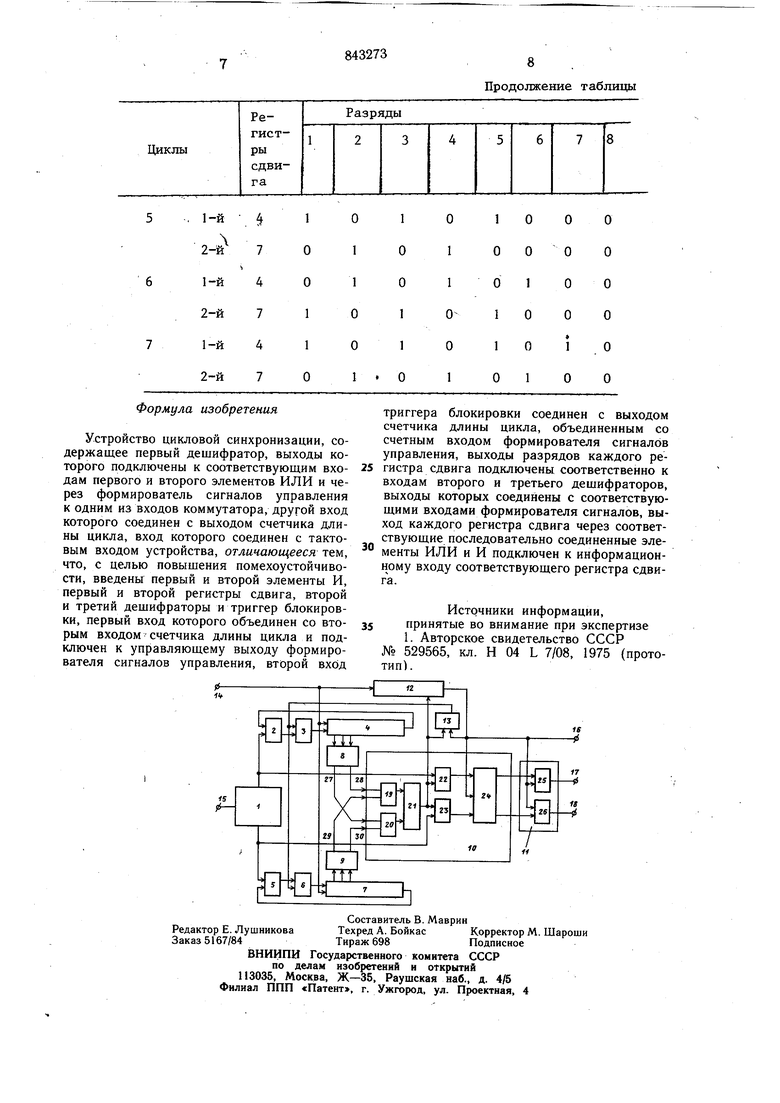

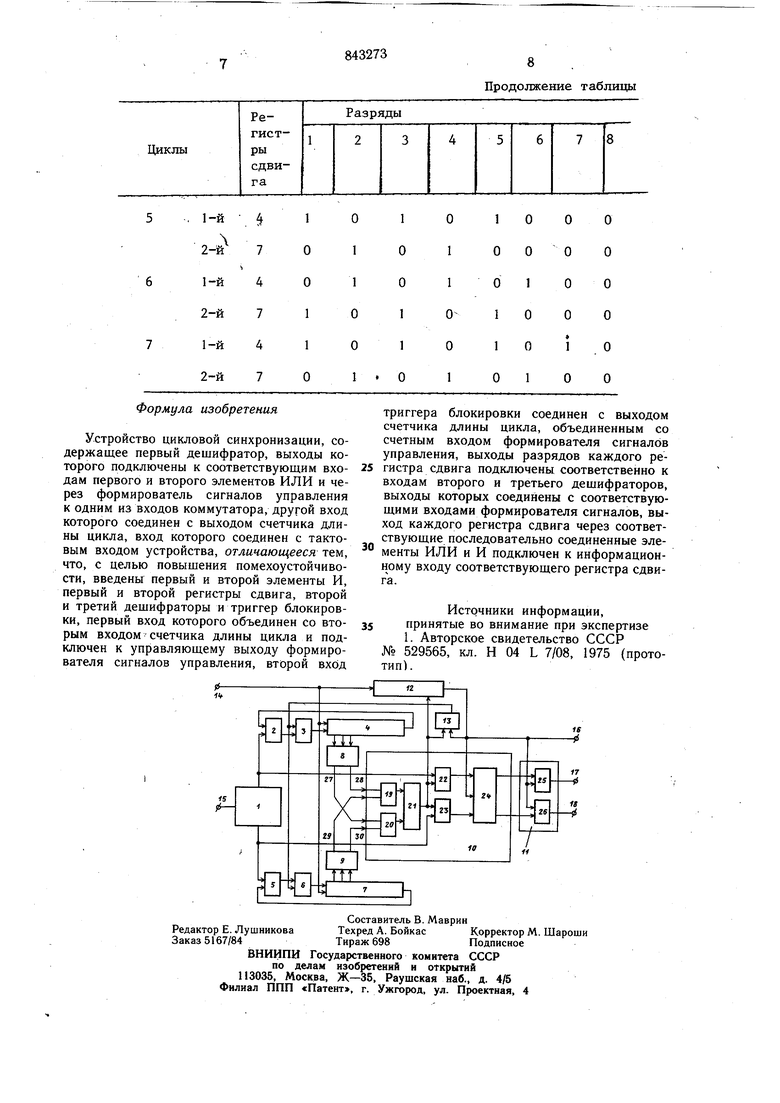

Пусть первым по времени на выходе дешифратора 1 маркерных синхрогрупп появился маркер Ml, который, пройдя через первый элемент ИЛИ 2 и первый элемент И 3, поступает на информационный вход первого регистра 4 сдвига и начинает продвигаться по регистру 4 сдвига под действием тактовых импульсов. Если первый маркер Ml соответствует истинной синхрогруппе первого вида, то ровно через цикл на втором выходе дешифратора 1 маркерных синхрогрупп появляется маркерный импульс М2, который, пройдя через вторые элементы ИЛИ 5 и И 6, поступает на информационный вход второго регистра 7 сдвига. Поскольку разрядность обоих регистров 4 и 7 сдвига выбрана равной (п-1), где п- длина цикла синхронизации, то в этот момент времени первый маркер Ml, продвигаясь по закольцованному первому регистру 4 сдвига, окажется во втором его разряде, а в первом разряде будет записан 0. Если чередующиеся маркеры Ml и М2 будут регулярно появляться на выходах дешифратора 1 маркерных синхрогрупп, то заполнение регистров 4 и 7 сдвига можно представить в виде следующей таблицы.

Положим: что решающее правило вхождения в синхронизм состоит в следующем: синхронизация считается найденной, если на одной и той же позиции цикла подряд

пришли шесть чередующихся маркеров, т. е. три маркера Ml и три маркера М2. Тогда дешифраторы 8 и 9 управления должны иметь по шесть входов, сигнал на выходах 27 и 28 появляется, когда в первом, третьем и пятом разрядах регистров 4 и 7 сдвиta будет записана «1, а на выходах 29 и 30 - когда «1 будет находиться во втором, четвертом и шестом разрядах.

В соответствии с приведенной таблицей в шестом цикле появятся сигналы на выходах 28 и 29, которые, поступив на управляющие входы формирователя 10 сигналов управления, вызовут появление сигнала на выходе элемента И 19. Пройдя через элемент ИЛИ 21, сигнал совпадения пройдет на управляющий выход формирователя 10 сигналов управления и установит по входу сброса фазу счетчика 12 длины цикла соответствующей началу цикла синхронизации. Кроме того, сигнал с выхода элемента И 19 устанавливает триггер 13 блокировки на время одного цикла в положение, при котором первый и второй элементы И 3 и 6 закрыты, в результате чего за этот цикл регистры 4 и 7 сдвига обнуляются и вновь готовы к повторению режима накопления маркерных импульсов. И, наконец, сигнал с выхода элемента И 19 совпадает на элементе И 23 с маркерным импульсом М2 и устанавливает триггер 24 в положение, при котором с выхода элементов И 25 и 26 коммутатора 11 на второй и третий выходы 17 и 18 устройства поступают регулярные импульсные последовательности маркеров Ml и М2 соответственно. На первый выход 16 устройства с выхода счетчика 12 длины цикла, поступает регулярная последовательность импульсов цикловой синхронизации М М1 М2.

Триггер 13 блокировки возвращается в исходное положение первым же цикловым импульсом с выхода счетчика 12 длины цикла, после чего процесс работы устройства происходит аналогично описанному.

Если на выходе дешифратора 1 маркерных синхрогрупп первым появляется отклик маркера М2, то в шестом цикле появляются сигналы на выходах 27 и 30 дешифраторов 8 и 9 управления, которые вызывают появление сигнала совпадения на вуходе элемента И 20, который, аналогично описанному случаю, устанавливает фазу счетчика 12 длины цикла, перебрасывает триггер 13 блокировки в положение, закрывающее на очередной цикл информационные входы регистров 4 и 7 сдвига и устанавливает в результате совпадения с маркером Ml на элементе И 22 триггер 24 в нужную фазу.

В процессе дальнейщей работы устройства фаза счетчика 12 длины цикла и триггера 24 подтверждается импульсом с выхода элемента ИЛИ 21, вследствие того, что истинные маркеры Ml и М2 группируются на одной и той же позиции цикла синхронизации., а ложные отклики на синхрогруппы типа маркерных распределены случайно по длине цикла и поэтому не вызывают срабатывания элементов И 19 и 20 в формирователе 10 сигналов управления. Так же и ложная кодовая комбинация, совпадающая с синхрогруппой первого или второго вида и регулярно повторяющаяся на одной и той же позиции в каждом цикле синхронизации (так называемый «молчащий канал), не вызывает изменения фазы счетчика 12 длины цикла, поскольку отклики на нее накапливаются только в одном, из регистров 4 или 7 сдвига, поэтому совпадения выходных сигналов дешифраторов 8 и 9 управления на элементах И 19 и 20 не происходит. Использование в устройстве цикловой синхронизации,вновь введенных элементов триггера блокировки, двух элементов И, двух дещифраторов управления и двух п 1 разрядных регистров сдвига и предложен-, ное соединение элементов устройства между собой выгодно отличают данное устройство от известного, так как оно имеет существенно более высокую помехоустойчивость и в общем случае требует значительно меньще времени для входа в синхронизм. Например, при цифровой подаче сигналов изображения при стандартной длине строки 128 бит и б-ом разрядном маркере в каждом строчном цикле возможно образование в среднем 400ОО Исход- 1-и ное состо- 2-й 7ООО0 яние IMrA 2 ложных синхрогрупп, распределенных по длине строки случайным образом. Поскольку в предложенном устройстве как истинные, так и ложные отклики накапливаются в регистрах сдвига, то оно войдет в синхронизм через число строк, заданное рещающим правилом, в то время, как известному устройству для этого потребуется в среднем в 3 раза больще времени. В предельном случае известному устройству может понадобиться для входа в синхронизм ( j) циклов гдец -длина цикла синхронизации; Кп -длина маркерной синхрогруппы;R- число циклов проверки вхождения в синхронизм, определяемое рещающим правилом (бычно R 2-6, в рассмотренном описании устройства R было выбрано равным шести). Поскольку предложенное устройство входит в синхронизм за R циклов, то для рассматриваемого примера строчной синхронизации сигналов изображения выигрыщ во времени вхождения в синхронизм составляет 3-11 раз. 0000 0000

Продолжение таблицы

Авторы

Даты

1981-06-30—Публикация

1979-10-04—Подача