Изобретение относится к области электроизмерительной техники и может быть использовано для повышения точности измерений в тестерной аппаратуре, предназначенной для исследования динамики автоматных навигационных систем движущихся объектов, в исиытателя.х больши.х интегральных схелг, в коррелометрах, в системах опознавания образов, в регистраторах редких сигналов, в статистических анализаторах и в контрольно- 1змерительных приборах.

Известные устройства для цифровой записи используют сдвигающие регистры.

Для решения ряда распространенных на практике задач, требующих записи на интервале 7 серии из /7 сигнальных импульсов с относительной погрешностью дискретности Т

при осуществлении этого

устройства требуется сложное оборудование. Эго обстоятельс1во серьезно тормозит применение устройств цифровой записи сигналов в измерительной аппаратуре, в радиолокационных и связных системах и т. д.

Для повыщения точности записи сигналов гри ограниченном объеме обор дования предлагаемое устройство снабжено коммутатором, а каждый разряд блока записи - счетчиком к дополнительным триггером с раздельными

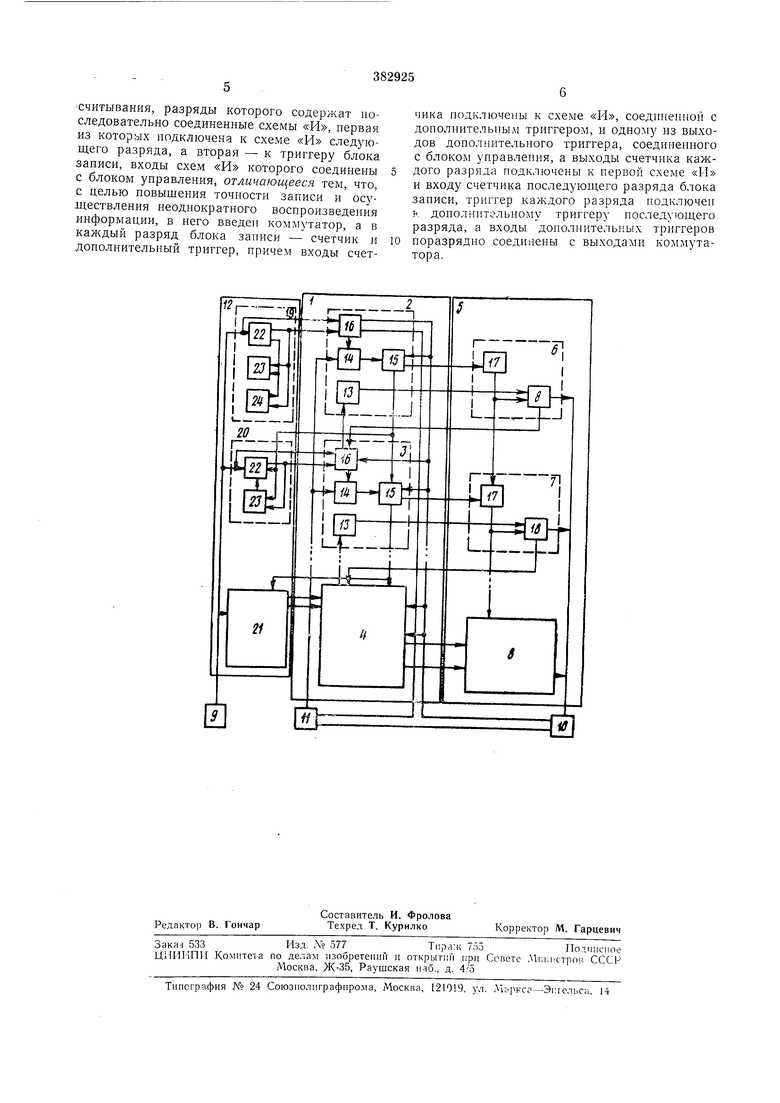

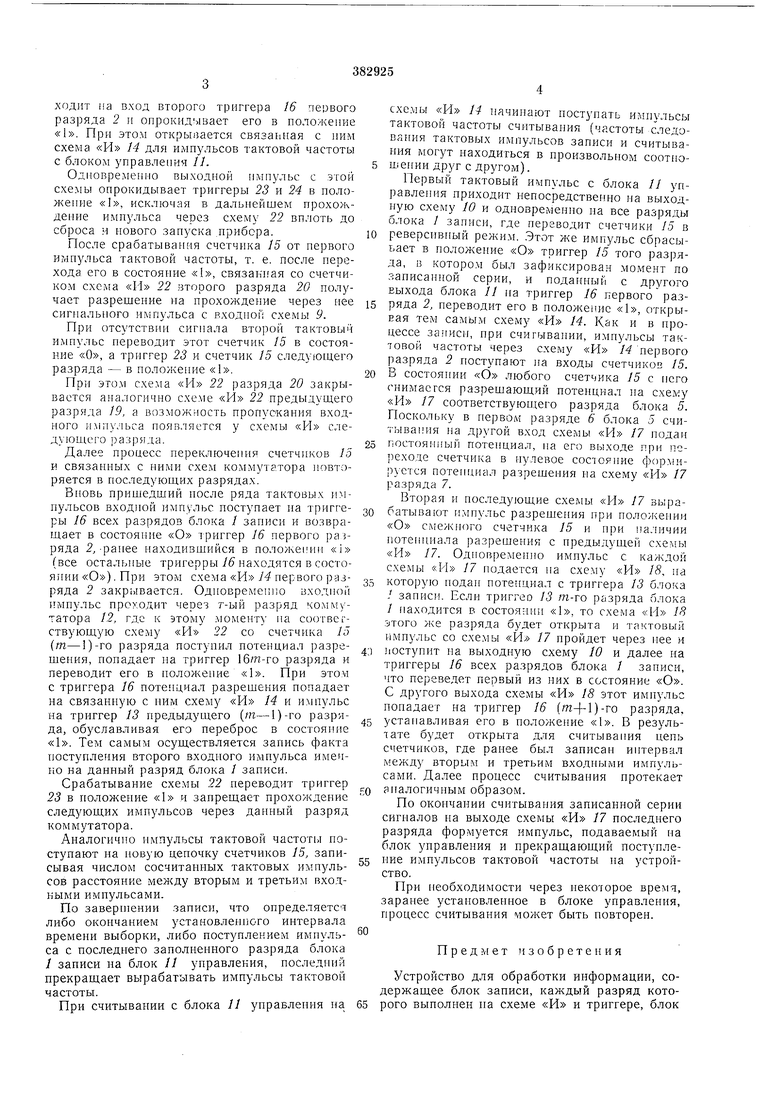

входами, а оло1 считывання, предназначенный для 1еоднократного зоснроизведения заннсп, выполнен в виде связанных между собой разрядов, каждый из которых снабм-:ен двумя последовательно соединенными схемами «И. На чертеже дана блок-схема устройства. Устройство содержит блок / записи с разрядами 2, 3 и 4, блок 5 считывания и разрядами 6, 7 и 8, входную с.хе.му 9, выходную схему 10, блок управления 11 и ко.ммутатор 12. Каждый разряда 2, 3 и 4 блока / записи состоит из первого триггера 13, схемы «И 14, счетчика 15 и второго триггера 16. Каждый разряд 6, 7 и S блока 5 считывания содержит

две пос.чедовательно соединенные с.хемы «II 17 и 18.

Разряды 19, 20 и 21 коммутатора 12 содержат схему «И 22 и триггеры 23 и 24.

Устройство работает следующим образом.

В исходном положении счетчики и триггеры установлены в нулевое ноложенне. При этом схемы «И всего устройства закрыты, исключая схемы 22 и 17 первого разряда. Для поддержания схе.мы 22 первого разряда коммутатора 12 в открытом состоянии введен триггер 24. Схема 17 устанавливается в открытом состоянии с помощью поданного на него постоянного потенциала.

Первый импульс с входной схемой 9 через

открытую схему «И 22 коммутатора 12 проходит на вход второго триггера 16 первого разряда 2 и опрокидмвает его в положение «1. При этом открывается связанная с ним схема «И 14 для импульсов тактовой частоты с блоком управления 11. Одновременно выходной нмнульс с этой схемы опрокидывает триггеры 23 w. 24 в ноложение «1, исключая в дальнейшем прохождение импульса через схему 22 вплоть до сброса и нового запуска.прибора. После срабатывания счетчрн а 15 от нервого имнульса тактовой частоты, т. е. после перехода его в состояние «1, связаньая со счетчиком схема «И 22 второго разряда 2G получает разрешение на прохождение через нее сигнального импульса с входной схемы 9. При отсутствнн сигнала второй тактовый импульс переводит этот счетчик 15 в состояние «О, а триггер 23 и счетчик 15 следующего разряда - в положение «1. При этом схема «И 22 разряда 20 закрывается аналогично схеме «И 22 предыдущего разряда 19, а возможность пропускания входного импульса ноявляется у схемы «PI следующего 5азряда. Далее процесс переключения счетч1П ов 15 и связанных с ними схем коммутатора повторяется в последующих разрядах. Вновь пришедший после ряда тактовых y пульсов входной импульс поступает на триггеры 16 всех разрядов блока / записи и возвращает в состояние «О григгер 16 первого ра iряда 2,-ранее находившийся в положении «i (все остальные трнгерры У6| находятся в состоянии «О). При этом схема «И 74 нервого разряда 2 закрывается. Одновременно входной импульс проходит через г-ый разряд коммутатора 12, где к этому моменту на соответствующую схему «И 22 со счетчика 15 (т-)-го разряда поступил потенциал разрешения, попадает на триггер 16/п-го разряда и переводит его в положение «1. При этом с триггера 16 потенциал разрешения попадает на связанную с ним схему «И 14 и импульс на триггер 13 предыдущего (т-1)-го разряда, обуславливая его переброс в состояние «1. Тем самым осуществляется запись факта поступления второго входного импульса именно на данный разряд блока / записи. Срабатывание схемы 22 переводит триггер 23 в положение «1 и запрещает прохождение следующих импульсов через данный разряд коммутатора. Аналогично импульсы тактовой частоты иоступают на новую цепочку счетчиков 15, записывая числом сосчитанных тактовых импульсов расстояние между вторым и третьим входными импульеами. По заверншнии записи, что определяется либо окончанием установленного интервала времени выборки, либо поступлением импульса с последнего заполненного разряда блока / записи на блок // управления, последний прекращает вырабатывать импульсы тактовой частоты. При считывании с блока 11 управлення на схемы «И 14 начинают поступать импульсы тактовой частоты считывания (частоты следования тактовых импульсов записи и считывания могут ПаХОДИТЬСЯ в произвольном COOTilOIIIе1гии друг с другом). Первый тактовый импульс с блока 11 управления приходит непосредственно на выходную схему 10 и одновременно на все разряды блока / записи, где переводит счетчики 15 в реверсивный режим. .Этот же импульс сбрасыьает в положение «О триггер 15 того разряда, в котором был зафиксирован момент по записанной серии, и поданный с другого выхода блока // на триггер 16 первого раз-на,I---. ряда 2, переводит его в положение «1, открывая тем самым схему «И 14. Как и в процессе заиисн, нри счигывании, имнульсы тактовой частоты через схему «И 14 первого разряда 2 поступают на входы счетчиков 15. В состоянии «О любого счетчика 15 с него снимаегся разрешающий потенциал на схему «И /7 соответствующего разряда блока 5. Поскольку в первом разряде 6 блока 5 считывания на другой вход схемы «И 17 нодан Г|ОСтоя1Н ый потенциал, на его выходе прн пе)еходе счетчика в нулевое состояние формируется поте1ншал разрешения на схему «И 17 разряда 7. Вторая и последующие схемы «И /7 вырабатывают мпульс разрешепия при положепии «О смежного счетчика 15 и нри наличии потенциала разрешения с предыдущей схемы «И 17. Одновременно импульс с каждой схемы «И 17 подается на схе.му «И 18, на которую нодан потенциал с триггера 13 блока , записи. Если триггер 13 т-го разряда блока / находится в состоянии «1, то схема «И 18 этого же разряда будет открыта и тактовый импульс со схемы «И /7 пройдет через нее и ностунит иа выходную схему 10 и далее на триггеры 16 всех разрядов блока / записи, что переведет первый из них в состояние «О. С другого выхода схемы «И 18 этот импульс попадает на триггер 16 (т4-1)-го разряда, уста11авливая его в положение «1. В результате будет открыта для считывания цепь четчиков, где ранее был записан интервал между вторым и третьим входными импульами. Далее процесс считывания протекает аналогичным образом. По окончании считывания записанной серии игналов на выходе схемы «И 17 последнего азряда формуется импульс, подаваемый на лок управления и прекращающий поступлеие импульсов тактовой частоты па устройтво. При необходимости через некоторое время, аранее установленное в блоке управления, роцесс считывания может быть повторен. Предмет изобретения Устройство для обработки информации, соержащее блок записи, каждый разряд котоого выполнен на схеме «И и триггере, блок

считывания, разряды которого содержат последовательно соединенные схемы «И, первая из которых подключена к схеме «И следующего разряда, а вторая - к триггеру блока записи, входы схем «И которого соединены с блоком управления, отличающееся тем, что, с целью повышения точности записи и осуществления неоднократного воспроизведения информации, в него введен коммутатор, а в каждый разряд блока записи - счетчик и дополнительный триггер, причем входы счетчика подключены к схеме «И, соединенной с дополнительным триггером, и одному из выходов дополнительного триггера, соединенного с блоком управления, а выходы счетчика каждого разряда подключены к первой схеме «И и входу счетчика последующего разряда блока записи, триггер каждого разряда подключен к дополнительному триггеру последующего разряда, а входы дополнительных триггеров

поразрядно соединены с выходами коммутатора.

| название | год | авторы | номер документа |

|---|---|---|---|

| еС?СОгО?НЛЯ | 1973 |

|

SU369716A1 |

| ЦИФРОВОЙ РЕГИСТРАТОР ПЕРЕХОДНЫХ ПРОЦЕССОВ | 1990 |

|

RU2029310C1 |

| Цифровой фильтр | 1990 |

|

SU1730718A1 |

| Устройство для вычисления временных интервалов микропроцессорных систем | 1980 |

|

SU960781A1 |

| Преобразователь двоичного кода в двоично-десятичный код | 1989 |

|

SU1662005A1 |

| Устройство для спектрального анализа с постоянным относительным разрешением | 1982 |

|

SU1109760A1 |

| Устройство для контроля и диагностики состояний объекта | 1989 |

|

SU1679468A1 |

| Устройство для сортировки чисел | 1985 |

|

SU1277092A1 |

| Устройство контроля состояния объектов | 1985 |

|

SU1366993A1 |

| Устройство для сопряжения цифровой вычислительной машины с магнитофоном | 1984 |

|

SU1188745A1 |

Авторы

Даты

1973-01-01—Публикация