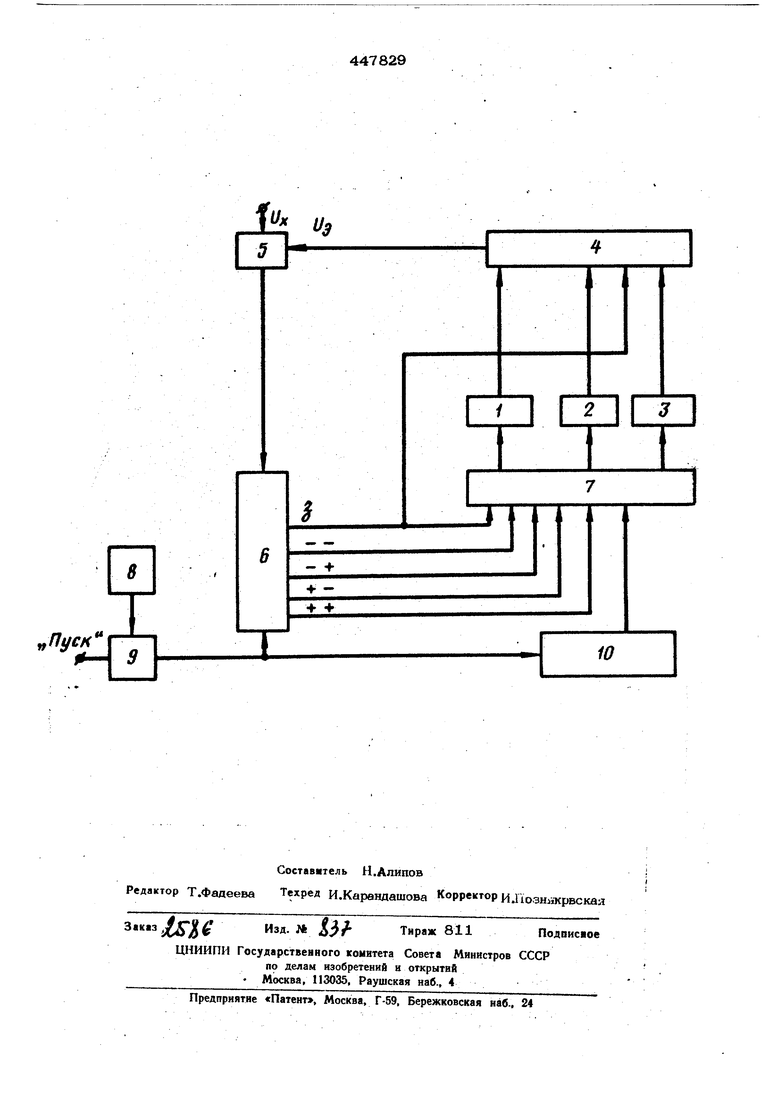

Изобретение относится к аналого-цифро вым преобразователям и может быть исполь зовано в различных устройствах вычислительной техники и измерительных приборах. Известны преобразователи напряжение в код (ПИК) поразрядного уравновешивания, состоящие из регистра кода, регистра сдвига, разнопол1фного линейного декодирующего преобразователя, г-онерагора тактов, компаратора и схемы пуска. Целью изобре1ения является повышение помехоустойчивости ПИК при работе в усло ВИЯХ действия периодических помех. Это достигается тем, что в схему ПНК дополнительно введены регистры верхнего и нижнего уровней эталонных напряжений и блок формирования эталонных напряжений, причем первый вход блока формирования эталонных напряжений соединен с выходом компаратора, второй вход- с выходом схемы пуска, а выходы его соединены со входами линейно-декодирующего преобразовател и со входами логической схемы, выходы которой через регистры верхнего и нижнего уровня эталонных напряжений подключены к линейно-декодирующему преобразователю. На чертеже изображена структурная схема предлагаемого преобразователя. Он содержит регистр кода (РК) 1, регистры верхнего (РВ) 2. и нижнего (РИ) 3 уровней эталонной напряжений, линейнодекодирующий преобразователь (ЛДП) 4, юмпаратор (К) 5, блок формирования эталонных напр$1жений (БФЭ) 6, логическую схему 7, генератор тактов (ГТ) 8, схему пуска 9 и регистр сдвига 10. Преобразователь работает следующим образом. Тактовая частота ГТ 8 устанавливается такой, чтобы длительность такта д была больше максньвльно возможного периода помехи. Значение j -го разряда 01 i на -ом такте преобразования ( j 1, 2П , где П, - число разрядов результата кодирования N.. ) Определяется за один такт аналогично алгоритму известного ПНК поразрядного уравновешивания , если на данном j -ом и на всех предшествующих (1, 2, р -ом. j ) тактах эталонное напряжение у , формируемое на выходе ДДП 4, не попадало в зону действия периодической помехи. Зоной действия периодической по мехи является интервал напряжений . -, . - истинное значение преобра зуемого сигнала; - амплитуда помехи. Признаком того, что (jn находится вне зоны действия периодической помехи явдяется выполнение на каждом такте только одного из следующих двух услови (полагая, что компаратор 5 производит непрерывное сравнение U С Up ) f .Э (;;(/; При этом в конце каждого такта появляется разрешающий потенциал на шине ++ БФЭ 6, если имеет место условие (1), ; или на шине -, если имеет место усл вие (2), который через логическую схем 7 поступает на входы РК 1, РВ 2, РН и в соответствующих разрядах указанных регистров производится запись значения разряда кода Qj , соответствующего данному ( j -му) такту алгоритма, так .2-; .-2а на выходе ЛДП 4 формируется эталонное напряжение для определения следующего j +1-го разряда: 4 где rtftKC диапазон преобразуемых напряжений;П - число разрядов результирующего кода. Если на некотором j -ом такте в течение Д t произошло изменение зна II I Э м ., ка разности U j U (или с + на -), то можно полагать, что Uj оказалось в зоне действия периодической помехи, .. (3) в этом случае разрешающие потейциалы в конце j -го такта появляются -+ (или. +-) БФЭ на выходах з и и для определения значений 0(j , c/|m bi J разрядов кодов N: . NH; N8j производят два дополнительных I такта, на первом из которых с помощью Н 3 (РВ 2) формируют эталонное напряжение нижнего и..- (верхнего U.,- ) 1oj ровня, а на втором с помои1ью РВ 2 (РН 3) - эталонное напряжение верхнего Ээ , (нижнего ) уровня, равные: У«/(//-Г; - -.(У«акс, ijlrUj 2 - U,c (путем вычитания РН 3 и прибавления РВ 2 единицы j -1-го разряда, так WWjf W/./ /- -4 , В результате дополнительных тактов поучаем один из двух возможных исходов a),0; u;-U j,0; в)y;-u:,.,o. в случае а) в j -ом разряде РК 1 остается единичное значение ( Z ) а в РН 3 и РВ 2 1фибавляют единицу -го разрядаMH.,,.MHj,Z , и на следующих двух тактах формируют эталонные напряжения , ,- 2-1/ акс в случае б) в j -ом разряде РК 1 записывают нулевое значение и Nj Nj-, , в РН 3 прибавляют единицу j -гЬ разPHflaNHj NHj -2 . а в РВ 2 вычитают единицу j -го разряда и на следующих двух тактах формируют эталонные напряжения -г (л + макс t. ПЛКС В результате сравнения иЛ и u с ЭАА в конце второго такта получают следующие исходы ,5 л ..ff a) «5) . В случае а) в РК 1 прибавля цу j го разряда, а в РН 3 и ницу j +1-ГО разряда Nj3-- jZ МВуз . В случае б) в РК 1 и РН 3 ют единицу j +1НГО разряда, в вычитают единицу j t l. разря -( Ni,Nj2-2 . , NBi NBj2-2 . i Ha следующих двух тактах фор Эталонные напряжения ЭЭ 1 JHi NH sUMaKc 1 Бjз % ;и получают следующие исходы эIf э «).о, и.-и, -Bi3 Hj-s и;-и ,0. и;-и/ Jx-UJi5 0i г г) ,o, в случае а) РК 1 прибавляют j + 1-го разряда, а в РВ 2 и РН единицу j +2-ГР разряда -0+11 Ni , , NHj., -() NBj4: I в случае б) в РК 1 и РН 3 ют, а в РВ 2 вычитают единицу разряда , , ,,-Ci.) , NHi.b NHi, ,, в случае в) в РК 1 и РВ 2 прибавляют, а в РН 3 вычитают единицу J + разряда-{U2. м. M. 4- J . 1 NHj4 NHj5-2 NBj -NBi54-2 -, в случае г) в РВ 2, РН 3 вычитают единицу j -f 2-го разряда i NHj4, NHj,-2 NBj4: N6j,-2.J , На следующих двух тактах формируют эталонные напряжения ээ ийКС , MO-W Аналогично рассмотренному происходит работа преобразователя на всех последую-, щих тактах. Общее число тактов равно (i-j + i), где j - номер такта (начиная с первого) на котором обнаружена помеха. Предмет изобретения Преобразователь напряжения в код, со держащий ;разнополярный линейно-декодирующий преобразователь, компаратор, регистр кода, регистр сдвига, логическую схему, генератор тактов и схему пуска, причем выход генератора тактов через схему пуска, регистр сдвига, логическую схему, регистр кода и линейно-декодирую щнй преобразователь подключен к первому входу компаратора, второй вход которого соединен с источником преобразуемого напряжения, отличающийся тем, что, с целью повышения помехоустойчивости, в него введены регистр верхнего уровня и регистр нижнего уровня эталон- ных напряжений, причем;, первый вход блока формирования эталонных напряжений соединен с выходом компаратора, второй вход - с выходом схемы пуска, а его выходы -со входами линейно-декодирующего преобразователя и входами логической схемы, выходы которой через регистрверхнего уровня и регистр нижнего уровня подклю- ; чены ц линейно-декодирующему преобразо- вателю./

Us

| название | год | авторы | номер документа |

|---|---|---|---|

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬU..БИ&--^-- | 1973 |

|

SU385392A1 |

| Аналого-цифровой преобразователь в кодах с естественной избыточностью | 1986 |

|

SU1381698A1 |

| Цифровой фазометр | 1985 |

|

SU1298687A2 |

| Преобразователь амплитуды импульсов в код | 1984 |

|

SU1211883A1 |

| Устройство для определения координат объекта | 1990 |

|

SU1814196A1 |

| Аналого-цифровой преобразователь | 1978 |

|

SU750727A1 |

| Аналого-цифровой преобразователь | 1976 |

|

SU563713A1 |

| Устройство аналого-цифрового преобразования | 1982 |

|

SU1045378A1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 1971 |

|

SU310270A1 |

| ПРЕОБРАЗОВАТЕЛЬ АНАЛОГОВЫХ ВЕЛИЧИ В ЦИФРОВОЙ КОД | 1971 |

|

SU318963A1 |

- -f

s

„Пуск

LZJ LlJ

10

Авторы

Даты

1974-10-25—Публикация

1972-07-19—Подача