1

Изобретение относится к электроипо-измер.ительной технике и предназначено для счета числа импульсов с представлением чисел в десятичном коде и может быть использовано, о частности, в электронных цифровых измерительных системах и электронносчетных частотомерах.

Известны различные лересчетные устройства повышенного быстродействия. Все они характеризуются общ.им признаком - повышение частоты счета достигается посредством многократного деления частоты двоичными ячейками (счетчиками по модулю 2), не охваченными обратными связями с последующим восстановлением коэффициента деления на 10, 100 ,и т. д. Устройство содержит схему собирания, делители частоты с коэффициентами 2 и 5, схему совпадения, триггер управления, декады обратного счета, дешифраторы. Выход схемы совпадения, пропускаюш,ей импульсы «досчета, подключен ко входу декад обратного счета и через схему собирания - непосредственно ко входу делителя частоты с коэффициентом деления 2, выход которого через делитель частоты с коэффициентом деления 5 подключен ко входу выходной схемы совпадения и к одному входу триггера, управляюш,его схемами совпадения и управляемого по второму входу «импульсами начала досчета.

При;веденное устройство обладает рядом недостатков. К ним относятся существенное усложнение функционирования устройства, связанное с Преобразованием кода чисел, записанных в устройстве, в десятичный код и вызванное этим усложнение схемы, увеличение времени измерения на время «досчета, а также невозможность реализации режима «непрерывного счета, т. е. режима, требующего в любой момент времени соответствия между состояниями устройства и индикацией этих состояний.

Таким образом, целью изобретения является создание устройства повыщенного быстродействия, позволяющего осуществлять счет числа импульсов с представлением чисел в десятичном коде без увеличения времени измерения, обеспечивающего нормальное функционпрование в режиме «непрерывный счет, а более простого в работе. Для этого в счетчике установлено (п-1) преобразователей кодов 2 --5 в код где и 1,2, ..., (п-1), причем входы первого преобразователя соединены с выходами (п-1) делителей на 2 и с выходом первого делителя на 5, а пятиричный выход этого преобразователя и выход первого делителя на 2 подключены к первому дещифратору двоично-десятичного кода к десятичной, а входы каждого из последующих преобразователей кодов 2 --5 в код соединены с выходом последующего делителя «а 5 .и с двоичными выходами, кроме первого, предыдущего преобразователя, первый двоичный выход которого и пятиричный выход последующего преобразователя подключены к соответствующему дещифратору.

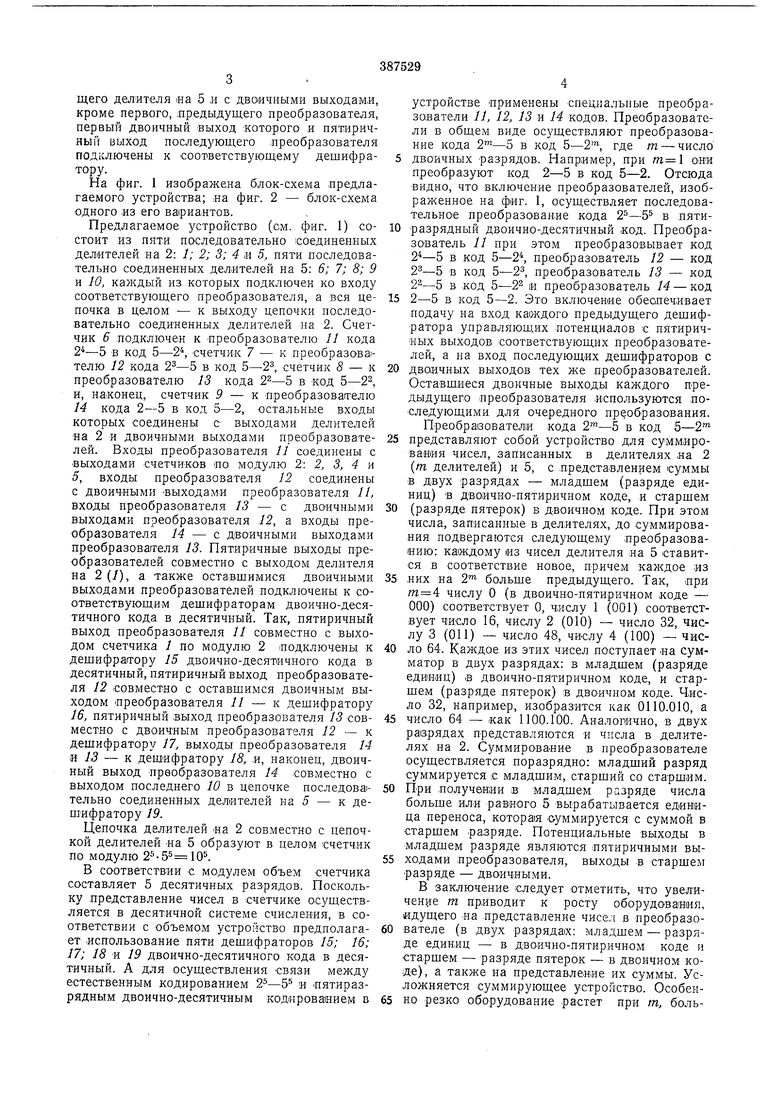

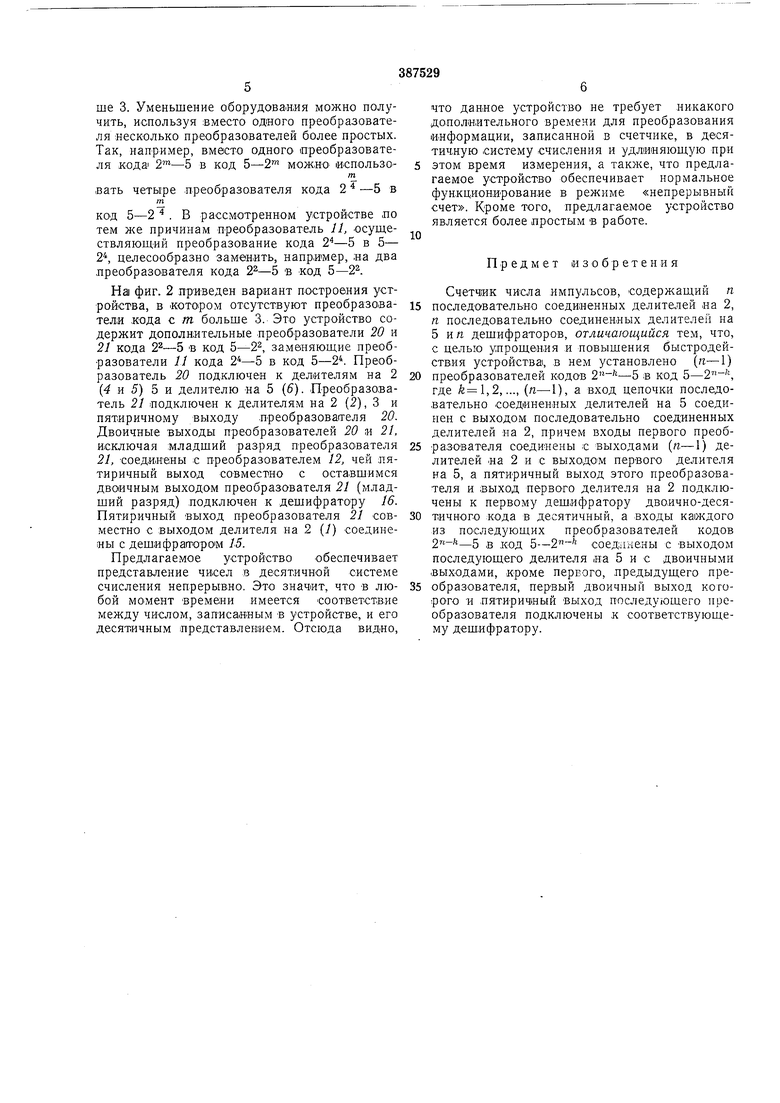

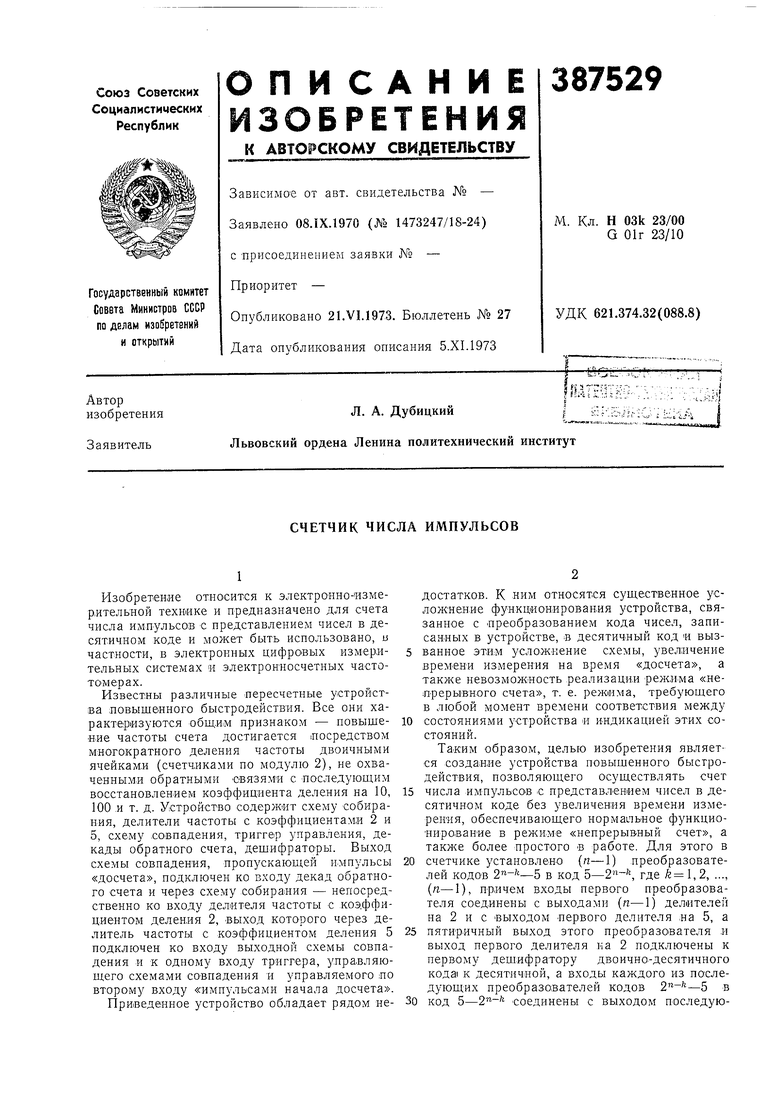

На фиг. 1 изображена блок-схема .предлагаемого устройства; на фиг. 2 - блок-схема одного из его вариантов.

Предлагаемое устройство (см. фиг. 1) состоит из пяти последовательно 1соединен:Ных делителей на 2: /; 2; 3; 4 и 5, пяти последовательно соединенных делителей на 5: 6; 7; 8; 9 и 10, каждый из которых подключен ко входу соответствующего преобразователя, а вся цепо чка в целом - к выходу цепочки по.следовательно соединенных делителей на 2. Счетчик 6 подключен к преобразователю 11 кода в код 5-2, счетчик 7 - к ореобразоеа телю 12 кода в код 5-2, счетчик 8 - к преобразователю 13 кода в код 5-2 и, наконец, счетчик 9 - к преобразователю 14 кода 2-5 в код 5-2, остальные входы которых соединены с выходами делителей на 2 и двоичными выходами преобразователей. Входы преобразователя 11 соединены с выходами счетчиков по модулю 2: 2, 3, 4 п 5, входы преобразователя 12 соединены с двоичными выходами преобразователя II, входы преобразователя 13 - с двоичными выходами преобразователя 12, а входы преобразователя 14 - с двоичными выходами преобразователя 13. Пятиричные выходы преобразователей совместно с выходом делителя на 2 (/), а также оставшимися двоичными выходами преобразователей подключены к соответствующим дешифраторам двоично-десятичного кода в десятичный. Так, пятиричный выход преобразователя 11 совместно с выходом счетчика 1 по модулю 2 -подключены к дешифратору 15 двоично-десятичного кода в десятичный, пятиричный выход преобразователя 12 совместно с оставщимся двоичным выходом преобразователя // - к дешифратору 16, пятиричный выход преобразователя /5 совместно с двоичным преобразователя 12 - к дешифратору 17, выходы преобразователя 14 и 13 - к дешифратору 18, и, наконец, двоичный выход преобразователя 14 совместно с выходом последнего 10 в цепочке последова;тельно соединенных делителей на 5 - к дешифратору 19.

Цепочка делителей на 2 совместно с цепочкой делителей на 5 образуют в целом счетчик по модулю 10

В соответствии с модулем объем счетчика составляет 5 десятичных разрядов. Поскольку представление чисел в счетчике осуществляется в десятичной системе счисления, в соответствии с объемом устройство предполагает использование пяти дешифраторов 15; 16; 17; 18 и 19 двоично-десятичного кода в десятичный. А для осуществления связи между естественным кодированием и пятиразрядным двоично-десятичным кодированием в

устройстве применены специальные преобразователи 11, 12, 13 и 14 кодов. Преобразователи в общем виде осуществляют преобразование кода 2™-5 в код 5-2™, где т - число двоичных разрядов. Например, при оии преобразуют код 2-5 в код 5-2. Отсюда видно, что включение преобразователей, изображенное на фиг. 1, осуществляет последовательное преобразование кода в пятиразрядный двоично-десятичный код. Преобразователь 11 при этом преобразовывает код в код 5-2 преобразователь 12 - код в код 5-2, преобразователь 13 - код 22-5 в код и преобразователь 14 - код

2-5 в код 5-2. Это включение обеспечивает подачу на вход ка1ждого предыдущего дещифратора управляющих потенциалов с пятиричных выходов соответствующих преобразователей, а на вход последующих дешифраторов с

двоичных выходов тех же преобразователей. Оставшиеся двоичные выходы каждого предыдущего преобразователя используются последующими для очередного преобразования. Преобравователи кода 2™-5 в код 5-2™

представляют собой устройство для суммирования чисел, записанных в делителях на 2 (т делителей) и 5, с представлением суммы в двух разрядах - младшем (разряде единиц) в двоично-пятиричном коде, и старшем

(разряде пятерок) в двоичном коде. При этом числа, записанные в делителях, до суммирования подвергаются следующему преобразованию: каждому из чисел делителя на 5 ставится в соответствие новое, причем каждое из

них на 2™ больше предыдущего. Так, при числу О (в двоично-пятиричном коде - 000) соответствует О, числу 1 (001) соответствует число 16, числу 2 (010) - число 32, числу 3 (011) - число 48, числу 4 (100) - число 64. Каждое из этих чисел поступает на сумматор в двух разрядах: в младшем (разряде единиц) ,в двоично-пятиричном коде, и старшем (разряде пятерок) в двоичном коде. Число 32, например, изобразится как 0110.010, а

число 64 - как 1100.100. Аналогично, в двух разрядах представляются и числа в делителях на 2. Суммирование в преобразователе осуществляется поразрядно: младщий разряд суммируется с младшим, старший со старшим.

При получении в младшем разряде числа больше или равного 5 вырабатывается единица переноса, которая суммируется с суммой в старшем разряде. Потенциальные выходы в младшем разряде являются пятиричными выходами преобразователя, выходы в старшем разряде - двоичными.

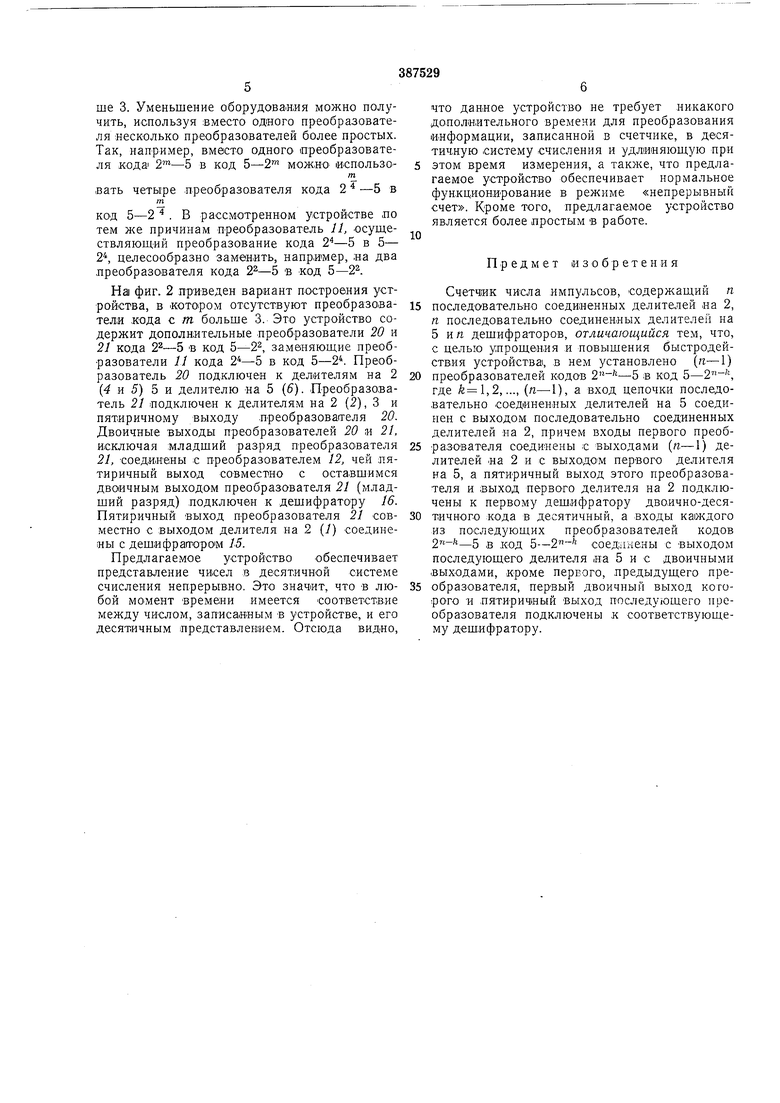

В заключение следует отметить, что увеличенуе т приводит к росту оборудования, идущего на представление чисел в преобразователе (в двух разрядак: младшем-разряде единиц - в двоично-пятиричном коде и старшем - разряде пятерок - в двоичном коде), а также на представление их суммы. Усложняется суммирующее устройство. Особенно резко оборудование растет при т, больше 3. Уменьшение оборудоваиия можно получить, используя вместо одиого преобразователя яесколько преобразователей более простых. Так, например, вместо одного преобразователя кода 2™-5 в код 5-2 можно использо,вать четыре преобразователя кода 2 -5 в

т

КОД 5-2 . в рассмотренном устройстве ,по тем же причинам п-реобразователь //, осуществляюЩИЙ преобразование кода в 5- 2, целесообразно заменить, например, на два преобразователя кода в код 5-2.

На фиг. 2 .приведен вариант построения устройства, в котором отсутствуют преобразователи кода с т больше 3. Это устройство содержит дополнительные преобразователи 20 и 21 кода в код 5-2, заменяющие преобразователи // кода в код 5-2. Преобразователь 20 подключен к делителям на 2 (4 и 5) 5 и делителю на 5 (5). Преобразователь 21 подключен к делителям на 2 (2), 3 и пятиричному выходу .преобразователя 20. Двоичные выходы преобразователей 20 и 21, исключая младший разряд преобразователя 21, соединены с преобразователем 12, чей ;пятиричный выход совместно с оставшимся двоичным выходом преобразователя 21 (младший разря.д) .подключен к дешифратору 16. Пятиричный выход преобразователя 21 совместно с выходом делителя на 2 (1) соединены с дешифраггором 15.

Предлагаемое устройство обеспечивает представление чисел в десятичной системе счисления непрерывно. Это значит, что в любой момент времени имеется соответствие между числом, записанным в устройстве, и его десятичным представлением. Отсюда видно.

что данное устройство не требует никакого до.полнительного времени для преобразования информации, записанной в счетчике, в десятичную систему счисления и удл иняюш,ую прн этом время измерения, а также, что предлагаемое устройство обеспечивает нормальное функционирование в режиме «непрерывный счет. Кроме того, предлагаемое устройство является более простым в работе.

Предмет изобретения

Счетчик числа .импульсов, содержащий п

последовательно соединенных делителей на 2, п последовательно соединенных делителей на 5 ия дешифраторов, отличающийся тем, что, с целью упрошения и повышения быстродействия устройства, в нем уста.новлено (п-1)

преобразователей кодов в код где k-,2,..., (), а вход цепочки последовательно соединенных делителей на 5 соединен с выходом последовательно соединенных делителей на 2, причем входы первого преобра.зователя соединены с выходами (п-i) делителей «а 2 и с выходом первого делителя на 5, а пятиричный выход этого преобразователя и выход первого делителя на 2 подключены к первому дешифратору двоично-десятичного кода в десятичный, а входы каждого из последующих преобразователей кодов 2 --5 в .код соединены с выходом последующего делителя на бис дво.ичными выходами, кроме первого, .предыдущего преобразователя, первый двоичный выход которого и пятиричный выход последующего преобразователя подключены к соответствующему дешифратору.

И

Фиг.1

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь п-разрядного десятичного кода в пятиричный | 1976 |

|

SU645150A1 |

| Преобразователь десятичной дробиВ пяТиРичНую | 1979 |

|

SU796837A1 |

| Устройство для измерения температуры | 1982 |

|

SU1081438A1 |

| Преобразователь двоичного кода угла в двоично-десятично-шестидесятиричный код градусов,минут,секунд | 1980 |

|

SU960791A1 |

| Преобразователь двоичного кода в двоично-десятичный код угловых единиц | 1985 |

|

SU1396280A2 |

| ЭЛЕКТРОННОСЧЕТНЫЙ ЧАСТОТОМЕР | 1972 |

|

SU340979A1 |

| Преобразователь двоичных чисел в двоично-десятичные числа | 1980 |

|

SU941990A1 |

| ПРЕОБРАЗОВАТЕЛЬ ДВОИЧНО-ДЕСЯТИЧНОЙ ДРОБИ В ДВОИЧНУЮ ДРОБЬ | 1979 |

|

SU826335A1 |

| Преобразователь двоичного кода в код с произвольным весом младшего разряда | 1985 |

|

SU1325708A1 |

| Устройство для преобразования двоичного кода в десятичный и обратно для чисел с плавающей запятой | 1977 |

|

SU717755A1 |

Авторы

Даты

1973-01-01—Публикация