1

Изобретение относится к области вычислительной техники и может быть использовано при построении цифровых вычислительных машин лоследователъного действия с высоким уровнем структурной интеграции элементов входного языка.

Известны устройства для определения старшинства выполняемых операций в вычислительных машинах, содержащие регистр знака, соединенный со стеком операционных знаков.

Цель изобретения - упрощение структуры и снижение аппаратурных затрат на построение устройства.

Цель достигается благодаря применению в предлагаемом устройстве специальной схемы, допускающей последовательную поразрядную обработку кодов операционных знаков.

Чтобы обеспечить последовательную обработку кодов операционных знаков при определении очередности выполнения каждой операции, вводится информационная избыточность при представлении кодов операционных знаков. Информационная избыточность позволяет представить код операционного знака состоящим из двух частей: -собственно кода операциолного знака, несущего информацию о коде операции, и кода старшинства этого операционного знака. При этом для выражения кода старшинства операционного знака используют унитарный код. При использовании

предлагаемого устройства только часть кода операционного знака передается на расшифровку в устройство управления машины, а именно, собственно код операционного знака. КоЕСТруктивно цель достигается тем, что предлагаемое устройство содержит два элемента «ИЛИ, элемент «И, линию задержки, формирователь и триггер, причем регистр знака и стек операционных знаков подключены

через элемент «И, линию задержки и формирователь к одному из входов первого элемента «ИЛИ, второй вход которого соединен со стеком операционных знаков, а выход - с единичным входом триггера, нулевой вход которого через второй элемент «ИЛИ подключен к выходу регистра знака.

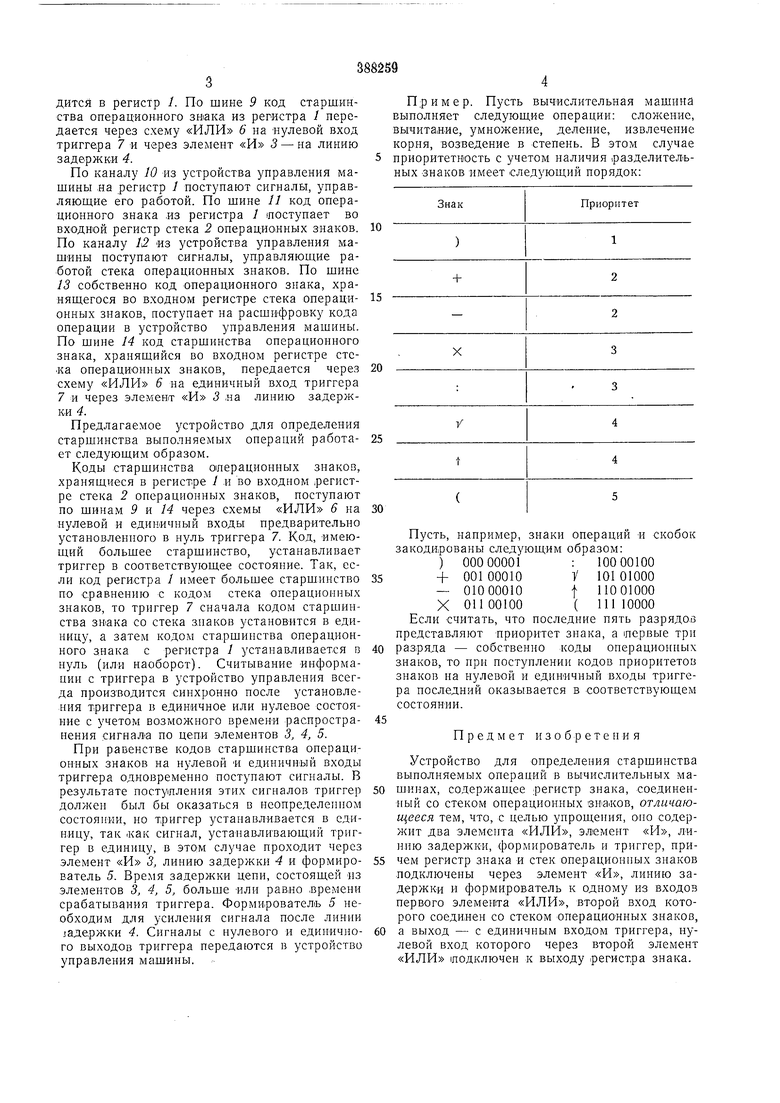

Функциональная схема предлагаемого устройства представлена на чертел е. Устройство состоит из регистра / знака,

предназначенного для хранения каждого последнего введенного в машину кода операционного знака; стека 2 операционных знаков запоминающего устройства, .в котором хранятся коды невыполненных операционных

знаков; логического элемента 3, реализующего функцию линии задержки 4; формирователя 5; логических элементов 6, реализующих функцию триггера 7 с раздельными входами.

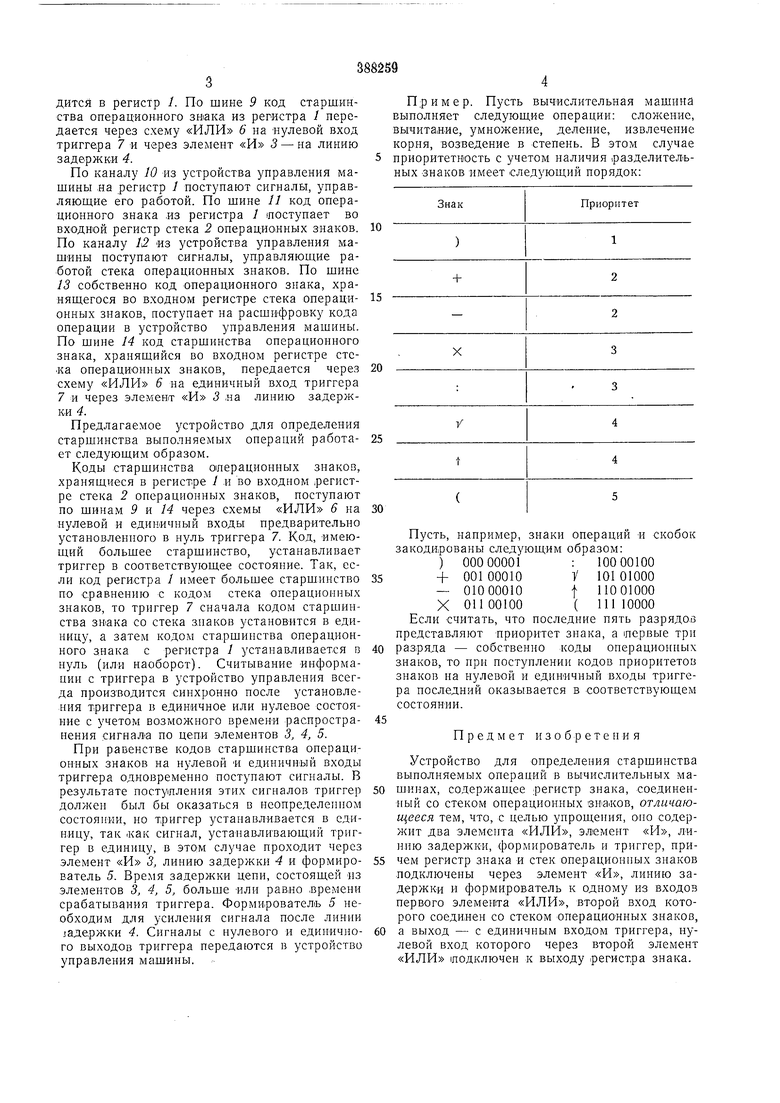

По каналу 8 код операционного знака вводится в регистр 1. По шине 9 код старш.инства операционного знака из регистра / передается через схему «ИЛИ 6 на нулевой вход триггера 7 и через элемент «И 3 - на линию задержки 4.5 По каналу 10 из устройства управления машины на регистр 1 поступают сигналы, управляющие его работой. По шине // код операционного знака -ИЗ регистра / поступает во входной регистр стека 2 операционных знаков. 10 По каналу 13 «з устройства управления машины поступают сигналы, управляющие работой стека операционных знаков. По шине 13 собственно код онерационного знака, хранящегося во входном регистре стека операци- 15 онных знаков, поступает на расшифровку кода операции в устройство управления машины. По шине 14 код старшинства операционного знака, хранящийся во входном регистре стека операционных знаков, передается через 20 схему «ИЛИ 6 на единичный вход триггера 7 и через элемент «И 3 на линию задержки 4. Предлагаемое устройство для определения старшинства выполняемых онераций работа- 25 ет следующим образом. Коды старшинства операционных знаков, хранящиеся в регистре / и во входном ;регистре стека 2 операцнонных знаков, поступают по шинам 9 к 14 через схемы «ИЛИ 6 на 30 нулевой и единичный входы предварительно установленного в нуль триггера 7. Код, имеющий большее старшинство, устанавливает триггер в соответствуюшее состояние. Так, если код регистра / имеет большее старшинство 35 по сравнению с кодом стека операционных знаков, то триггер 7 сначала кодом старшинства знака со стека злаков установится в единицу, а затем кодом старшинства оиерационного знака с регистра / устанавливается D 40 нуль (или наоборот). Считывание информации с триггера в устройство управления всегда производится синхронно после установления триггера в единичное или нулевое состояние с учетом возможного времени распростра- 45 нения сигнала по цепи элементов 3, 4, 5. При равенстве кодов старшинства операционных знаков на нулевой и единичн ый входы триггера одновременно поступают сигналы. В результате поступления этих сигналов триггер 50 должен был бы оказаться в неопределенном состоянии, но триггер устанавливается в единицу, так .как сигнал, устанавливаюший триггер в единицу, в этом случае проходит через элемент «И 3, линию задержки 4 и формиро- 55 ватель 5. Время задержки цепи, состояшей из элементов 3, 4, 5, больше или равно .времени срабатывания триггера. Формирователь 5 необходим для усиления сигнала после линии аде.ржки 4. Сигналы с нулевого и единично- 60 го выходов триггера передаются в устройство управления машины. Пример. Пусть вычислительная машина выполняет следующие операции: сложение, вычитание, умножение, деление, извлечение корня, возведение в степень. В этом случае приоритетность с учетом наличия .разделителъных знаков имеет следующий порядок: Пусть, например, знакн операций и скобок закодированы следующим образом: ) 00000001: 10000100 -f 001 00010У 101 01000 -- 01000010t 11001000 X oil 00100( 111 10000 Если считать, что последние пять разрядов представляют приоритет знака, а первые три разряда - собственно коды онерационных знаков, то нри поступлении кодов приоритетов знаков на нулевой и единичный входы триггера последний оказывается в соответствующем состоянии. Предмет изобретения Устройство для определения старщинства вынолняемых операций в вычислительных машинах, содержан1,ее регистр знака, соединенный со стеком операционных зна.ков, отличающееся тем, что, с целью упрощения, оно содержит два элемента «ИЛИ, элемент «И, линию задержки, формирователь и триггер, причем регистр знака и стек операционных знаков подключены через элемент «И, линию задержки и формирователь к одному из входов первого элемента «ИЛИ, второй вход которого соединен со стеком операционных знаков, а выход - с единичным входом триггера, нулевой вход которого через второй элемент «ИЛИ 1подключен к выходу регистра знака.

| название | год | авторы | номер документа |

|---|---|---|---|

| ПРИОРИТЕТНОЕ УСТРОЙСТВО ДЛЯ ВЫПОЛНЯЕМЫХ | 1973 |

|

SU407312A1 |

| Микропрограммный процессор со средствами быстрого прерывания | 1982 |

|

SU1116432A1 |

| Устройство для сопряжения центрального процессора с группой арифметических процессоров | 1984 |

|

SU1254495A1 |

| Устройство для сопряжения центрального процессора с группой арифметических процессоров | 1988 |

|

SU1529236A1 |

| Многофункциональное запоминающее устройство | 1972 |

|

SU458037A1 |

| Устройство для определения старшинства операций | 1979 |

|

SU857994A1 |

| Устройство для обучения | 1988 |

|

SU1663618A1 |

| СЛЕДЯЩИЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 1989 |

|

RU2028731C1 |

| Устройство для сопряжения процессора с устройством ввода-вывода | 1984 |

|

SU1180911A1 |

| Цифроаналоговый преобразователь с автоматической коррекцией нелинейности | 1988 |

|

SU1594699A1 |

Авторы

Даты

1973-01-01—Публикация