И, второй выход стека подключен к второму входу второго и второму входу четвертого элементов И, третий вход второго, третьего и четвертого элементов И подключен к седьмому входу устройства, выход второго, третьего и четвертого элементов И через элемент ИЛИ соединен с единичным входом триггера Г2.

Недостатком устройства является то, что оно работает последовательно, т.е. в каждом такте его работы осуществляется обработка только одного разряда кода, заданвдегр приоритет операционных знаков.

Цель изобретения - повышение быстродействия.

Поставленная цель достигается тем, что в устройство для определения старшинства операций, содержащее регистр знака, информационный вход которого соединен с информационным входом устройства, блок магазинной памяти, первый выход которого соединен с первым информационным выходом устройства, причем управляющие входы регистра знака и блока магазинной памяти соединены соответственно с первым и вторым выходами блока управления, а первый выход регистра знака соединенс информационным входом блока магазинной памяти, введен регистр адреса и блок оперативной памяти, причем вторые выходы регистра знака и блока магазинной памяти соединены с входами соответственно старших и младших разр5здов регистра адреса, выход которого и третий выход блока управления соединены соответственно с адресным и запускающим входами блока оперативной памяти,а информационный выход блока оперативной памяти соединен с входом блока управления.

Кроме того, блок управления содержит регистр адреса, первый вход которого является входом блока, а выход соединен с адресным входом памяти микрокоманд, выход которой соединен с входом регистра микрокоманд первый и второй выходы которого соединены соответственно с вторым входом регистра адреса и с входом дешифратора микрокоманд, выход которого соединен с информационным входом формирователя функциональных сигналов/ выходы которого являются соотве ственно первым, вторым и третьим выходами блока, узел синхронизации, выход которого соединен с синхровходами регистра адреса, памяти микрокоманд и формирователя функциональных сигналов.

На фиг. 1 приведена структурная схема устройства; на фиг. 2 - один из вариантов построения блока управления. , Устройство (фиг.1) содержит реблок 2 магазинной

тистр 1 знака

памяти, регистр 3 адреса, блок 4 оперативной памяти, информационный вход 5, управляющие входы 6-8, информационный выход 9, вход 10 блока управления, вход 11 блока магазинной g памяти, блок 12 управления.

Блок управления (фиг.2) может быть построен в виде регистра 13 адреса, памяти 14 микрокоманд, регистра 15 микрокоманд, дешифратора

Q 16 микроопераций, формирователя 17 функциональных сигналов и узла 18 си нхронизации.

Устройство работает следующим образом.

Код очередного знака программы на алгоритмическом языке поступает через информационный вход 5 устройства на регистр 1 знака. Под воздействием управляющего сигнала, выдаваемого по шине 6 блока 12 управления, этот код передается в стариие . разряды регистра 3 адреса. Одновременно, при помсчци управляющего сигнала на входе 7 блока 12, осуществляется передача кода знака из вершины блока 2 магазинной памяти в младшие разряды регистра 3 адреса. При поступлении сигнала по входу 8 выполняется чтение информации из ячейки блока 4 оперативной памяQ ти, адрес которой определяется кодом, находящимся на регистре 3. Считанная информация выдается на вход 10 блока 12.

В зависимости от полученной ин« формации об относительном приоритете операционных знаков может возникнуть потребность в обработке знака из блока 2 магазинной памяти, который выдается на выходе 9, или в записи кода знака из регистра 1 знака в

0 блок 2 магазинной памяти, которая производится по входу 11 под воздействием управляющих сигнале на входах б и 7.

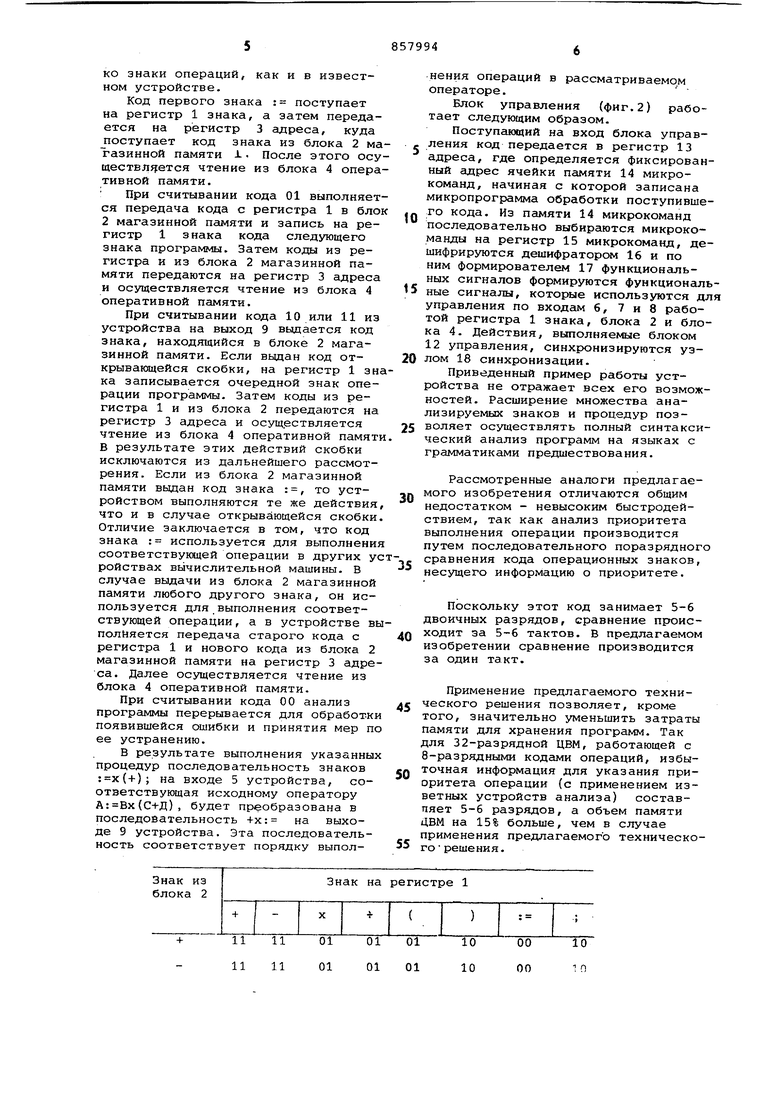

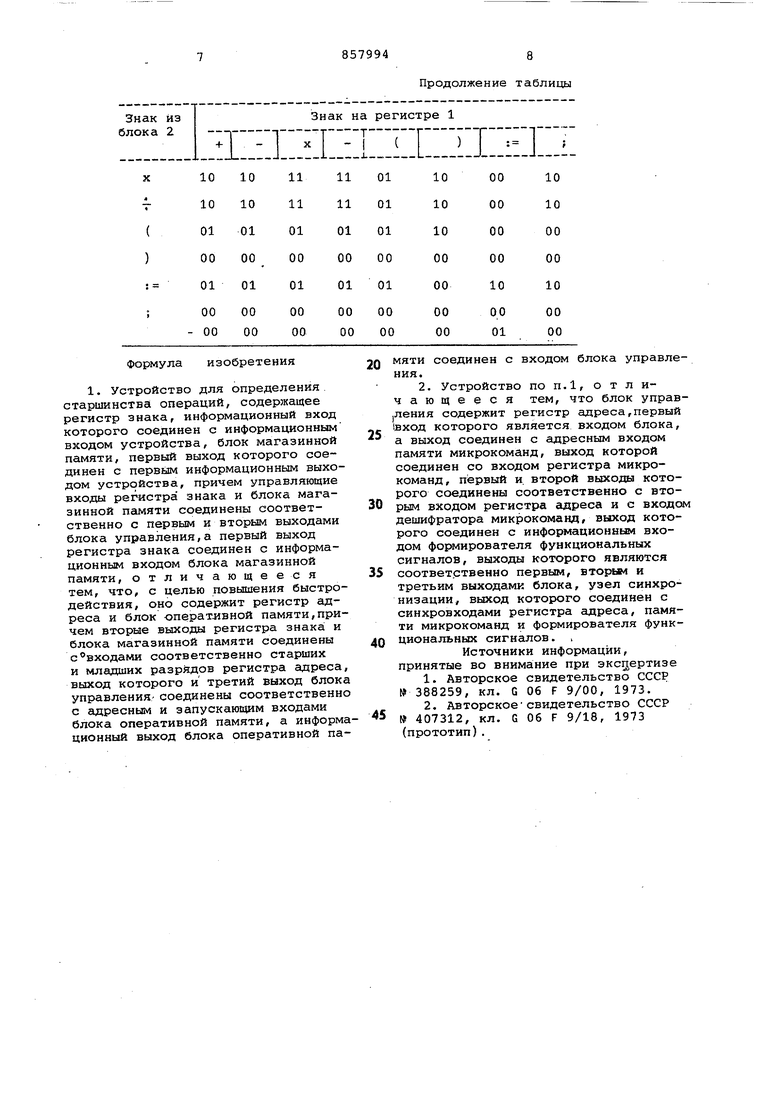

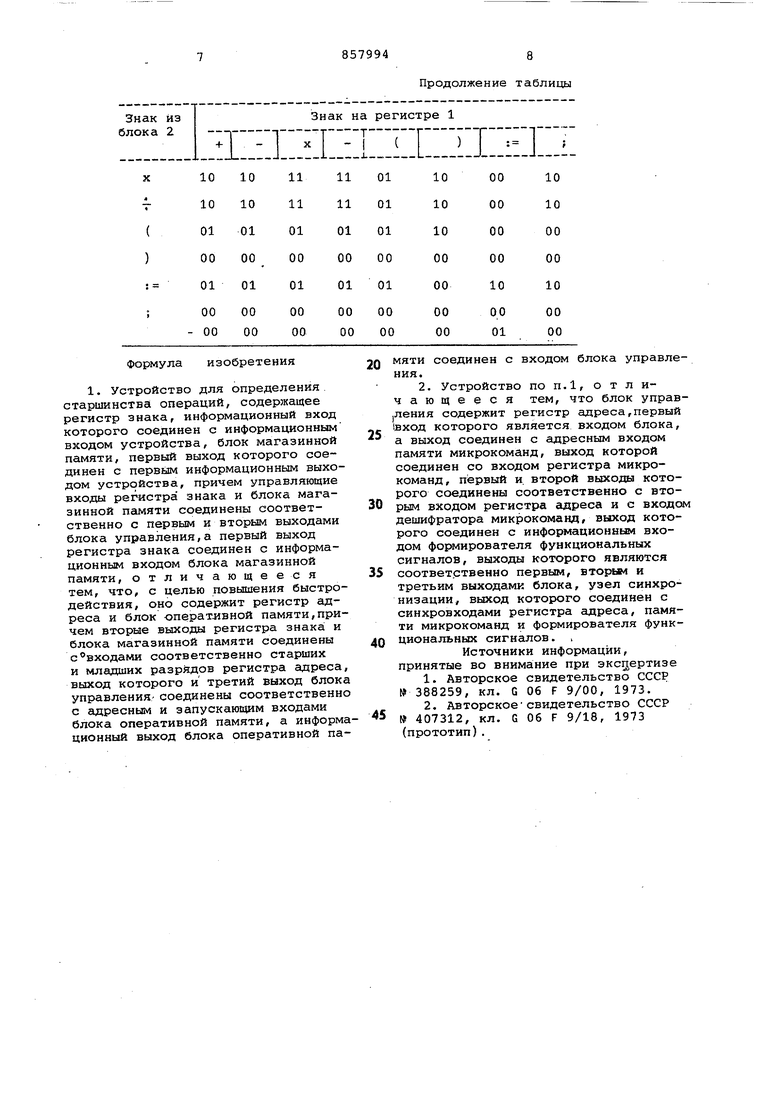

В таблице представлен пример содержимого ячеек блока 4 оперативной памяти для анализа оператора присваивания (знак X обозначает начальный символ в блоке 2 магазинной памяти) . Значениями этой таблицы явQ ляются коды, соответствукицие определенной комбинации знаков на регистре 1 знака и в блоке 2 магазинной памяти.

Коды интерпретируются следующим образом: 01 - приоритет знака на регистре 1 выше приоритета знака из блока 2; 10 - приоритет знака на регистре 1 меньше приоритета знака из блока 2; 11 - знаки имеют один 0 и тот же приоритет; 00 - недопустимое сочетание знаков.

Рассмотрим работу устройства на примере обработки оператора А: Бх(С+Д); при условии, что в предлагаемое устройство поступают только знаки операций, как и в известном устройстве.

Код первого знака : поступает на регистр 1 знака, а затем передается на регистр 3 адреса, куда поступает код знака из блока 2 маЪазинной памяти i После этого осуmecTBfljfeTCH чтение из блока 4 оперативной памяти.

При считывании кода 01 выполняется передача кода с регистра 1 в блок 2 магазинной памяти и запись на регистр 1 знака кода следующего знака программы. Затем коды из регистра и из блока 2 магазинной памяти передаются на регистр 3 адреса и осуществляется чтение из блока 4 оперативной памяти.

При считывании кода 10 или 11 из устройства на выход 9 выдается код знака, находящийся в блоке 2 магазинной памяти. Если выдан код открывающейся скобки, на регистр 1 знака записывается очередной знак операции программы. Затем коды из регистра 1 и из блока 2 передаются на регистр 3 адреса и осуществляется чтение из блока 4 оперативной памяти В результате этих действий скобки исключаются из дальнейшего рассмотрения. Если из блока 2 магазинной памяти выдан код знака :, то устройством выполняются те же действия, что и в случае открывающейся скобки. Отличие заключается в том, что код знака : используется для выполнения соответствукяцей операции в других ус ройствах вычислительной машины, в случае выдачи из блока 2 магазинной памяти любого другого знака, он используется для выполнения соответствующей операции, а в устройстве выполйяется передача старого кода с регистра 1 и нового кода из блока 2 магазинной памяти на регистр 3 адреса. Далее осуществляется чтение из блока 4 оперативной памяти.

При считывании кода 00 анализ программы перерывается для обработки появившейся ошибки и принятия мер по ее устранению.

В результате выполнения указанных процедур последовательность знаков (+); на входе 5 устройства, соответствующая исходному оператору (С+Д), будет преобразована в последовательность +х: на выходе 9 устройства. Эта последовательность соответствует порядку выполнения операций в рассматриваемом операторе.

Блок управления (фиг.2) работает следующим образом.

Поступающий на вход блока управления код передается в регистр 13 адреса, где определяется фиксированный адрес ячейки памяти 14 микрокоманд, начиная с которой записана микропрограмма обработки поступившего кода. Из памяти 14 микрокоманд

o последовательно выбираются микрокоманды на регистр 15 микрокоманд, дешифрируются дешифратором 16 и по ним формирователем 17 функциональных сигналов формируются функциональ5ные сигналы, которые используются для управления по входам 6, 7 и 8 работой регистра 1 знака, блока 2 и блока 4. Действия, выполняемые блоком 12 управления, синхронизируются уз0лом 18 синхронизации.

Приведенный пример работы устройства не отражает всех его возможностей. Расширение множества анализируемых знаков и процедур позволяет осуществлять полный синтакси5ческий анализ программ на языках с грамматиками предшествования.

Рассмотренные аналоги предлагаемого изобретения отличаются общим

0 недостатком - невысоким быстродействием, так как анализ приоритета выполнения операции производится путем последовательного поразрядного сравнения кода операционных знаков,

5 несущего информацию о приоритете.

Поскольку этот код занимает 5-6 двоичных разрядов, сравнение происходит за 5-6 тактов. В предлагаемом

0 изобретении сравнение производится за один такт.

Применение предлагаемого технического решения позволяет, кроме

5 того, значительно уменьшить затраты памяти для хранения программ. Так для 32-разрядной ЦВМ, работающей с 8-разрядными кодами операций, избыточная информация для указания при0оритета операции (с применением изветных устройств анализа) составпяет 5-6 разрядов, а объем памяти ДВМ на 15% больше, чем в случае применения предлагаемого техническо5го решения.

8579948

Продолжение таблицы

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство для анализа программ | 1980 |

|

SU943729A1 |

| Вычислительное устройство | 1987 |

|

SU1430962A1 |

| Микропроцессорное вычислительное устройство | 1982 |

|

SU1269145A1 |

| Селекторный канал | 1983 |

|

SU1226477A1 |

| Устройство для перевода выражений в польскую инверсную запись | 1982 |

|

SU1130879A1 |

| Устройство для сопряжения двух магистралей | 1986 |

|

SU1348874A1 |

| Анализатор спектров | 1982 |

|

SU1023341A1 |

| Многоканальное устройство для сопряжения ЭВМ | 1988 |

|

SU1695311A1 |

| Микропрограммный процессор со средствами быстрого прерывания | 1982 |

|

SU1116432A1 |

| Устройство синтаксически управляемого перевода | 1989 |

|

SU1651298A1 |

Авторы

Даты

1981-08-23—Публикация

1979-12-14—Подача