1

Изобреггелие относится к радиотехнике.

Р1з1вестны устройства для фильтрации сигналов, содержащие генератор опорного сигнала, к которому через фазо-расщепитель подсоедниены два сдвигающих регистра, матрицы весовых сум1мато;ров и квадратичный сумматор. На выходе известных устройств фильтрации отношение сигнал - щум уменьшается, чт.о затрудняет выделение пО|ЛезиоГ|0 си,Г|Нала и иЗ:Менание его параметров.

Предложенное устройство отличается тем, что оно содержит два логических преобразователя, входы которых соединены с выходами фазовых детекторов, а выходы подключены ко входам соответствующих регистров сдвига.

Каждый логический преобразователь содержит четыре схем1Ы совпадения, два сумматора, два вычитателя, выходной сумматор и последовательно включенные многоуровневый квантователь ам плитуды и сдвигающий регистр, выходы которого попарно соеди1нены со входами дв|Л-х сумматоров и двух вычитателей, подключенных через четыре схемы совпадения ко входам выходного сумматора. Это позволяет повысить на выходе фильтра отношение полезного сигнала к фазОМа.нииулированной полгехе.

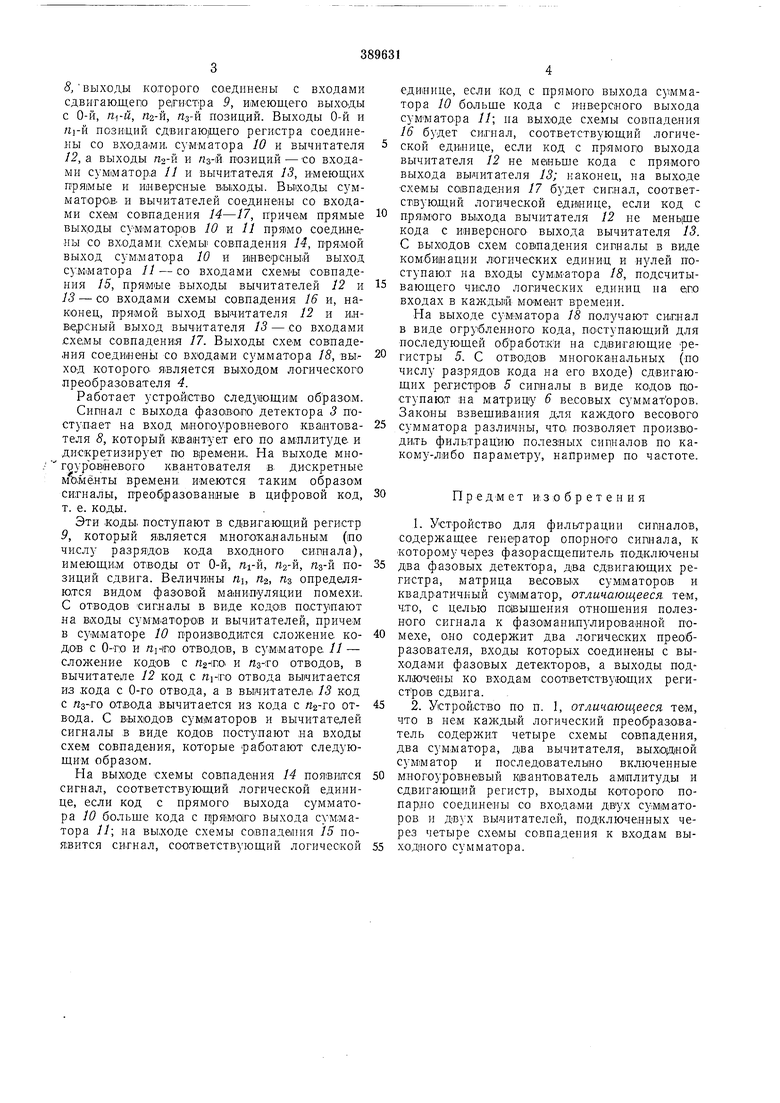

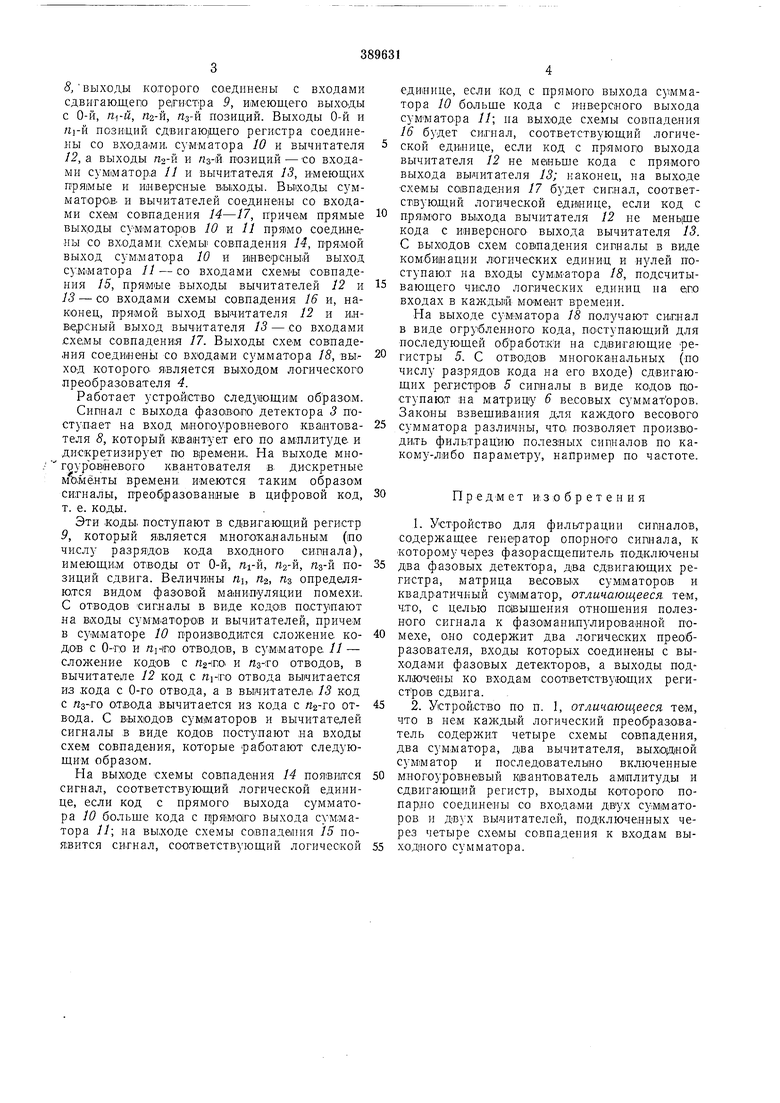

На фиг. 1 изображена блок-схема устройства.

Устройство состоит из генератора опорного си1гнала 1, фазорасщепителя 2, двух квадр.атурных каналов, в.клЮ|Чающих в себя фазовые детекторы 3, логические преобразователи 4, сдвигающие регистры с отводами 5, м.атрицы 6 11 7 весовых сумматоров и квадратичных сумматоров..

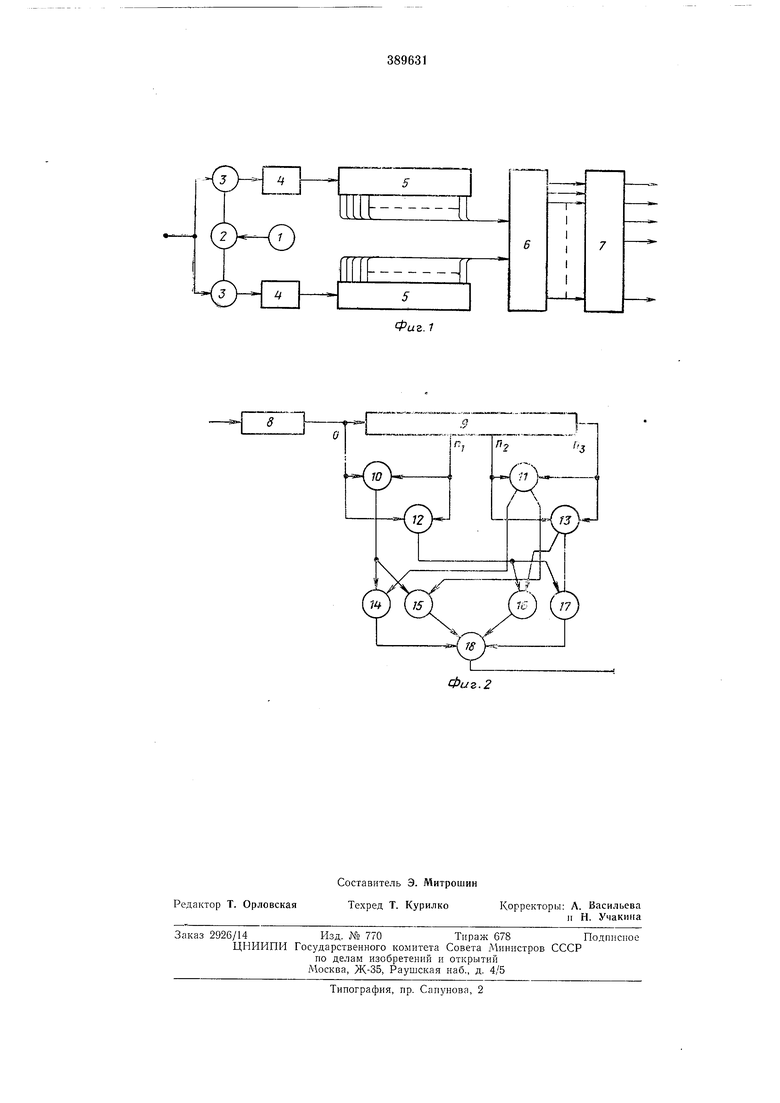

На фиг. 2 показана структурная схема логического преобразователя. Преобразователь

состоит из М1но,гоуровневого квантователя 8, сдвигак ще;10 регистра 9 с отводами на малое в сравнении с длительностью сигнала время, сумматоров 10, 11, вычнтателей 12, 13, схем соБпаде ния 14-17 и сумматора 18.

Элементы устройства соединены следующим образом.

Выход генератора опорного сигнала / соединен с фазорасп епителем 2, вы.ход фазо-. расщепителя - с управляющими. входа:ми

фазовых детекторов 3. Другие входы фазовых детекторов являются входом устройства. Выходы фазовых детекторов соединены с логическими преобразователями, выходы которых соединены со сдвигающими регнстр|ами 5. К выходам сдвигающих регистров 5 подсоединены входы матрицы 6 весовых сумматоров, к выходам которой подсоединены Вгходы матрицы 7 квадратичных сумматоров. Входом логического преобразователя 4 является вход многоуровневого, квантователя

5,выходы которого со.едннеиы с входами сдвигающегю peiracTipa 9, имеющего выходы с 0-й, «i-M, /г2-й, Яз-й позиций. Выходы 0-й и П1-Й позиций сдвигаЮ)Щего регистра соединены со входа ми, сумматора 10 и вычитателя }2,а выходы Л2-Й и «з-й позиций-со входами сум1матор:а 11 и вычитателя 13, ИМеющи.х прямые и ииверсиые вькоды. Вы1ходы сумматоре и вычитателей соединены со входами схем совшадения 14-17, причем прямые выходы сум(мато.ров 10 и 11 прямо соедине,ны со входами схе.мы совпадеиия 14, прямой выход сум,мато.ра 10 и ииверсный выход сумматора 11 - со входами схемы совпадения 15, прямые выходы вычитателей 12 и 13 - со входами схемы совпадения 16 и, наконец, пря:мой выход вы:читателя 12 и и,нверсный выход вычитателя 13 - со входами .схемы совпадения 17. Выходы схе-м совпадения соединены со входами сумматора 18, вы.ход которого является выводом логического преобразователя 4.

Работает устройство следующим образом.

Сипнал с выхода (ПО детектора 3 поступает на вход многоуровневого квантователя 8, который ковантует его по амплитуде и дискретизирует по В|ре1М.ени.. На выходе многоурЪвневого квантователя в дискретные моменты времени, имеются таким образом сигналы, преобразованные в цифровой код, т. е. коды.

Эти коды, поступают в сдвигающий регистр 9, который является многоканальным (по числу разрядов кода входного сиппала), имеющим от 0-й, rti-й, Дг-й, «з-й позиций сдвига. Величины rtj, HZ, Пъ определяются видом фазовой манипуляции помехи:. С отводов сигналы в виде кодов поступают на вйоды сумМаторое и вычитателей, причем в сумматоре 10 производился слолсение кодов с О-ГО и ,о отводов, в сум;маторе // - кодов с П2-1г;о. и Яз-го отводов, в вычитателе 12 код с отвода вычитается из кода с 0-го отвода, а в выяитателе 13 код с «3-го отвода вычиtaeтcя из кода с «2-го отвода. С выходов сумматоров и вычитателей сигналы в виде кодов поступают на входы схем совпадения, которые работают следующим образом.

На выходе схемы совпадения 14 поя1ви|тся сигнал, соответствующий логической единице, если код с прямого выхода сумматора 10 больще кода с п ря мо|го выхода сумматора 11; на выходе схемы совпадешия 15 появится сигнал, соответствзющий логической

единице, если код с прямого выхода сумматора 10 больще кода с и-нв.ерсного выхода сумматора //; на выходе схемы совпадения 16 будет сигнал, соответствующий логической единице, если код с прямого выхода вычитателя 12 не меньше кода с прямого выхода вьгаитателя 13; наконец, на выходе схемы совпадения 17 будет сигнал, соответствующий логической единице, если код с прямого выхода вычитателя 12 не меньще кода с инверсного выхода вычитателя 13. С выходов схем совпадения сигналы в виде комбинации логических единиц и нулей поступают на входы cyMiM-атора 18, подсчитывающего чвсло логических единиц на его входах в каждый момент времени.

На выходе сумматора 18 получают си1гнал в виде огрубленного кода, поступающий для последующей обработки иа сдвигающие регистры 5. С отводов многоканальных (по числу разрядов кода на его входе) сдвигающих регистров 5 сигналы в виде кодов поступают на матрицу 6 весовых сумматоров. Законы взвещивания для каждого весового сумматора различны, что позволяет производить фильтрацию полезных сипналов по какому-либо параметру, напри-мер по чаСтоте.

Предмет изобретения

1.Устройство для фильтрации снпналов, содержащее генератор опорного сигнала, к которому через фазорасщепитель подключены два фазовых детектора, два сдвигающих регистра, матрица весовых сумматор01В и квадр.атичный сумматор, отличающееся тем, что, с целью по|выщения отнощения полезного сигнала к фазоманипулированной помехе, оно содерлсит два логических преобразователя, входы которых соединены с выходами фазовых детекторов, а выходы под ключеиы ко входам соотшет1ствующих регистров сдвига.

2.Устройство по п. 1, отличающееся тем, что в нем калсдый логический преобразователь содержит четыре схемы совпадения, два сумматора, два вычитателя, выходной С}М1матор и последователыно включенные многоуровневый крантователь амплитуды и сдвигающий регистр, выходы которого попарно соединены со входами двух суздматоров и двух вычитателей, подключенных через четыре схемы совпадения к входам выходного сумматора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для многоуровневой дельта - модуляции | 1988 |

|

SU1674377A1 |

| Устройство для вычисления показателя экспоненциальной функции | 1986 |

|

SU1335990A1 |

| МОНОИМПУЛЬСНАЯ РАДИОЛОКАЦИОННАЯ СИСТЕМА | 2006 |

|

RU2309430C1 |

| Цифровой Фурье-преобразователь | 1982 |

|

SU1043663A1 |

| Цифровой фильтр | 1983 |

|

SU1116535A1 |

| Многоканальное устройство приема сложных сигналов | 1989 |

|

SU1786664A1 |

| ПРИЕМНИК ЦИФРОВЫХ СИГНАЛОВ | 2010 |

|

RU2423794C1 |

| Устройство для корреляционного приема фазоманипулированных сигналов | 1984 |

|

SU1197137A1 |

| МОНОИМПУЛЬСНАЯ РАДИОЛОКАЦИОННАЯ СИСТЕМА | 2000 |

|

RU2178896C1 |

| Цифровой фильтр | 1990 |

|

SU1736002A2 |

I

Фиг. 2

Авторы

Даты

1973-01-01—Публикация