1

Предлагаемое изобретение относится к аналоговой вычислительной технике, измерительной технике, может найти применение в радиотехнике, устройствах автоматического управления и других областях техники, где требуется точная по амплитуде и времени задержка аналоговых сигналов.

Известны схемы аналоговых регистров сдвига, содержащие запоминающие ячейки, например, конденсаторного типа, работающие по принципу последовательной перезаписи аналогового сигнала с одной запоминающей ячейки на другую.

Обычно передача сигнала осуществляется за два такта, в первом из которых информация со всех основных запоминающих ячеек записывается иа промежуточные запоминающие ячейки, а во втором сигналы с промежуточных ячеек одновременно передаются иа следующие основные ячейки. В таких схемах на каждый запоминаемый и сдвигаемый отсчет входного сигнала необходимо иметь две аналоговые запоминающие ячейки. При каждой перезаписи сигнала с ячейки на ячейку возникают ощибки нередачи, которые накапливаются за время сдвига и при большой емкости регистра сдвига могут составить значительную величину. Попытки повышения точности каждой запоминающей ячейки, например, за счет подбора запоминаемого напряжения по замкнутой схеме

приводят к значительному увеличению оборудования.

Целью предлагаемого изобретения является устранение указанных недостатков, т. е. повышение точности передачи сдвигаемой информации и сокращение общего количества оборудования.

Цель достигается введением распределителя импульсов, коммутатора и дифференциального

усилителя постоянного тока.

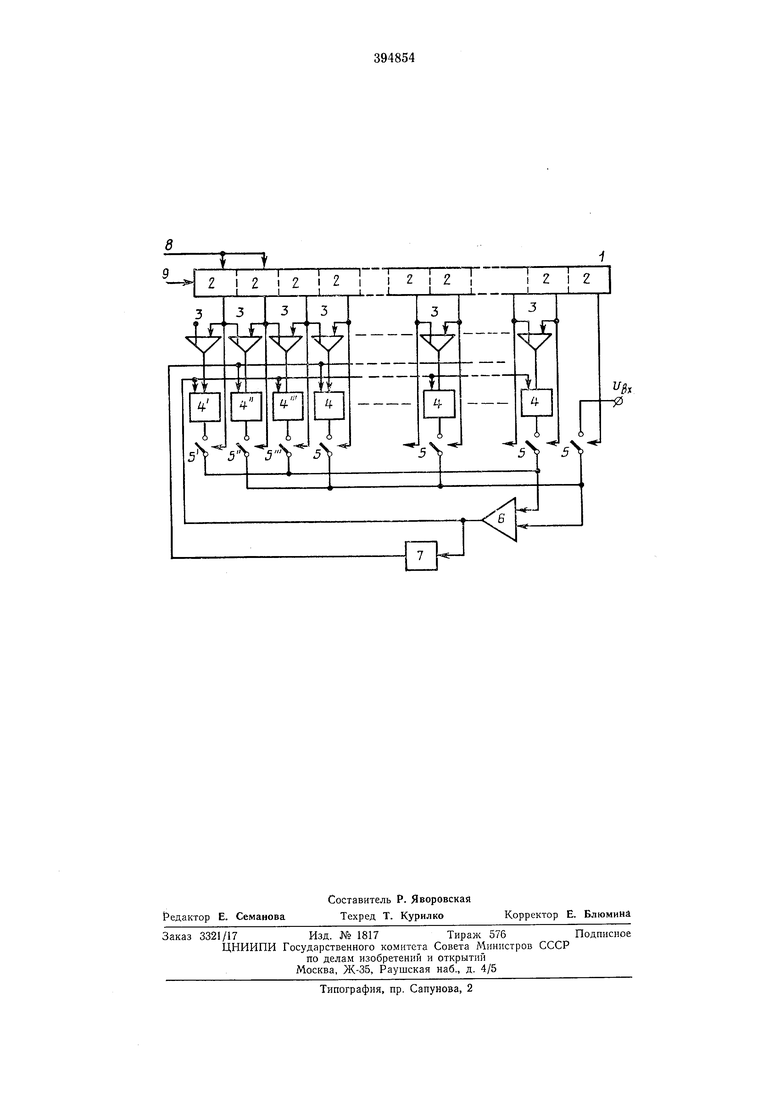

Ца чертеже изображена схема аналогового регистра сдвига.

Предлагаемый регистр сдвига содержит цифровой регистр сдвига 1, триггерные ячейки 2

регистра сдвига, логические элементь «НЕ Г 3, аналоговые запоминающие ячейки 4, аналоговые ключи 5, дифференциальный усилитель (J постоянного тока, инвертор 7, шипу S сигнала сдвига аналоговой информации и шину 9 высокочастотных тактовых импульсов.

Сигнал по шине 8 сдвига подай на входы установки в единицу двух младших ячеек 2 цифрового регистра сдвига /. На управляющий вход регистра сдвига / поданы высокочастотные тактовые импульсы по шине 9. Выходы iBcex соседни.х лар ячеек 2 регистра сдвига / подключены к входам логических элементов «НЕТ 3, причем выход младшего разряда подключен к запрещающему входу, а старшего - к разрешающему. Выходы элементов

«НЕТ 5 подключены к управляющим входам апалоговых запоминающих ячеек 4. Выходы аналоговых запоминающих ячеек соединены с ключами 5, управляющие входы которых соединены с выходами соответствующих разрядов регистра сдв-ига /. Выходы четных ключей 5 подключены на один из входов дифференциального усилителя 6, а нечетных ключей 5 - на другой. Выход усилителя 6 соединен со входами всех нечетных запоминающих ячеек 4 и входом инвертора 7. Выход инвертора соединен со входами всех четных запоминающих ячеек 5. Входной сигнал UB-S. подключается ко входу усилителя с помощью ключа 5, управляющий вход которого соединен со старщим разрядом цифрового регистра сдвига.

Схема работает следующим образом.

Сигнал сдвига по щине 8 устанавливает триггеры младших разрядов в единичное состояние, при котором выходы этих разрядов возбуждены. Это состояние сохраняется до прихода первого тактового импульса по щине 9. При этом через первый логический элемент «НЕТ на управляющий вход первой аналоговой запоминающей ячейки 4 подается сигнал, разрещающий запись, а на вход второй 4 и всех остальных ячеек 4 поданы сигналы, запрещающие запись.

Одновременно замыкаются ключи 5 и 5 (замыкается цепь обратной связи). На выходе усилителя 5 и на выходе первой запоминающей ячейки 4 подбирается напряжение, сводящее к нулю разбаланс напряжений на входе усилителя 6. Через некоторое время, определяемое инерционностью усилителя 6 и запоминающей ячейки 4, сигналы на выходе соседних ячеек выравниваются, т. е. осуществляется перезапись информации со второй ячейки 4 на первую.

Следующий тактовый импульс сдвигает информацию в цифровом регистре сдвига /, переводя его в состояние, при котором возбуждены выходы второго и третьего разрядов pei-истра сдвига /. Теперь сигнал разрещения записи подан на вторую ячейку 4, а на всех остальных ячейках присутствуют сигналы, запрещающие запись. Замкнуты ключи 5 и 5, и по цепи обратной связи, вклЕочающей усилитель 6 и инвертор 7, на ячейке 4 подбирается напряжение, равное нанряжению на ячейке / .

После следующего тактового импульса возбуждаются третий и четвертый РЫХОДЫ регистра сдвига, и аналогичным образом пронсходит перезапись напряжения с прсдыдугцей запоминающей ячейки 4 на последующую и так далее.

Таким образом, через число тактов, равное количеству запоминающих ячеек, происходит сдвиг всей информации, хранивщейся в ячейках 4 аналогового регистра, в соседние ячейки

с меньщими номерами и запись нового значения входного сигнала в последнюю ячейку.

В процессе работы функции входных зажимов дифференциального усилителя 6 меняются. Каждый нз них поочередно оказывается либо входом следящей систе.мы, либо входом цепи обратной связи. Это приводит к тому, что ошибки, вносимые дифференциальным усилителем 6 из-за дрейфа нуля и неравенства коэффициентов передачи но разным входам при каждой перезаписи, меняют знак и не паканливаются, а компенсируются. Таким образом, суммарные оЩИбки аналогового регистра сдвига существенно уменьщаются по сравнению с

известными схемами.

Инвертор 7 служит для изменения знака коэффициента передачи замкнутой цепи подбора сигналов на запоминающих элементах таким образом, чтобы он был всегда отрицательным.

Общее количество аналоговых запоминающих ячеек равно количеству заноминаемых выборок и вдвое меньще, чем в известных схемах.

Предмет изобретения

Аналоговый регистр сдвига, содержащий аналоговые запоминающие ячейки, отличающийся тем, что, с целью повыщепия точности

передачи сдвигаемой информации и сокращения количества оборудования, в устройство введены цифровой регистр сдвига с триггерными ячейками, элементы «НЕТ, аналоговые ключи, дифференциальный усилитель постоянного тока и инвертор, причем выходы цифрового регистра сдвига через элементы «НЕТ подключены к управляющим входам аналоговых запоминающих ячеек, запрещающие входы элементов «НЕТ каждого разряда соединены с выходами предществующего разряда цифрового регистра, выход каждой аналоговой запоминающей ячейки подключен к аналоговому ключу, соединенному с выходом соответствующего разряда цифрового регистра сдвига, выходы всех четных аналоговых ключей подключены к одному из входов дифференциального усилителя постоянного тока, а нечетных- к другому входу; выход дифференциального усилителя постоянного тока соединен

со входами всех четных аналоговых запоминающих ячеек и входом инвертора, выход которого соединен со входами нечетных аналоговых запоминающих ячеек; щина сигнала сдвига соединена со входами установки в единицу

младших разрядов цифрового регистра сдвига, управляющие входы которого соединены с шиной тактового сигнала, шина входного сигнала соединена со входом дифференциального усилителя через аналоговый ключ, подключенный

к старщему разряду цифрового регистра сдвига.

8

Ш

i 2 1 2 I

IIL

Щ

| название | год | авторы | номер документа |

|---|---|---|---|

| СУММИРУЮЩАЯ ЛИНИЯ ЗАДЕРЖКИ | 1972 |

|

SU420095A1 |

| Анализатор спектра | 1977 |

|

SU732759A1 |

| АНАЛОГО-ЦИФРОВАЯ МНОГОПРОЦЕССОРНАЯ СИСТЕМА | 2006 |

|

RU2333533C1 |

| Функциональный преобразователь многих перемнных | 1981 |

|

SU1115068A1 |

| Калибратор переменного напряжения | 1983 |

|

SU1115031A1 |

| Программно-управляемый цифровой фильтр | 1985 |

|

SU1338006A1 |

| Способ многоканального аналого-цифрового преобразования и многоканальный аналого-цифровой преобразователь | 1986 |

|

SU1451858A1 |

| Регистр сдвига | 1979 |

|

SU855732A1 |

| СДВИГОВЫЙ РЕГИСТР (ВАРИАНТЫ) | 2013 |

|

RU2530271C1 |

| Аналого-цифровой преобразователь | 1985 |

|

SU1297224A1 |

Авторы

Даты

1973-01-01—Публикация