1

Изобретение относится к вычислительной технике и может -быть использовано для проектирования накопителей цифровой информации оперативных запоминающих устройств.

Известны ячейки памяти динамического типа, предназначенные для оперативных ЗУ. Однако в них происходит стирание инфор.мации при считывании.

Для сохранения информации при считывании предлагаемая ячейка содержит буферный транзистор, затвор и подложка которого подключены к затоЛШнающему (конденсатору, сток - к шине считывания «ода, исток - к адресной шине считывания «ода.

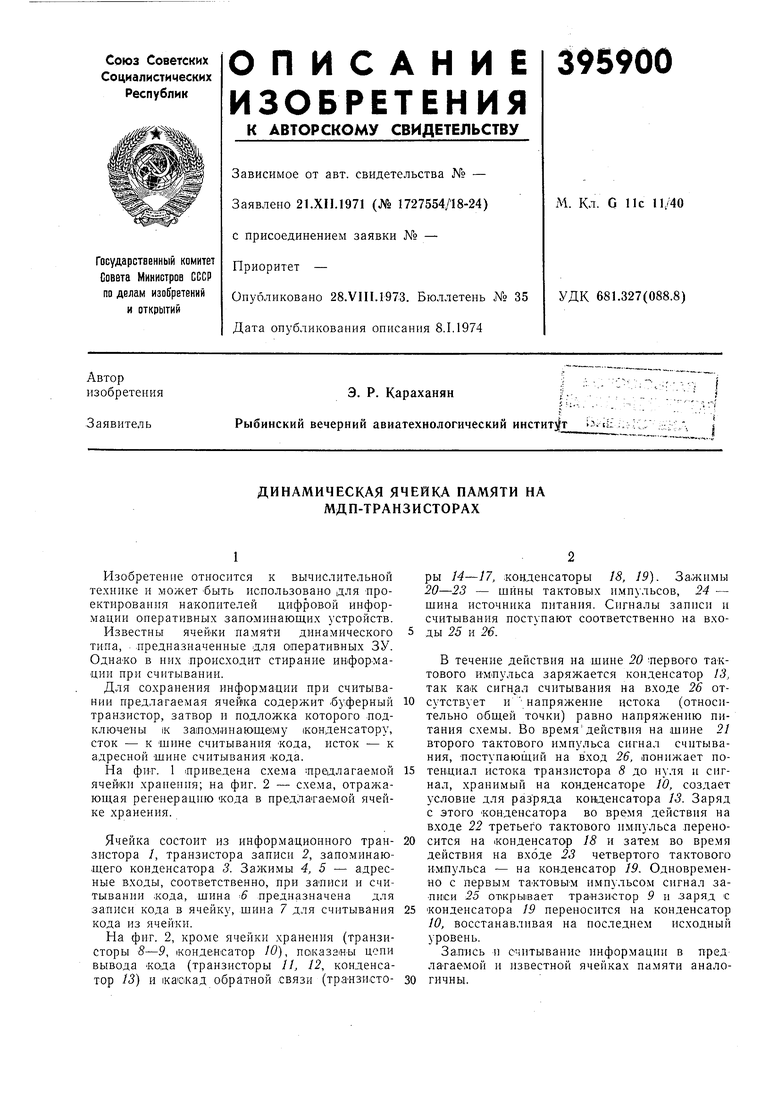

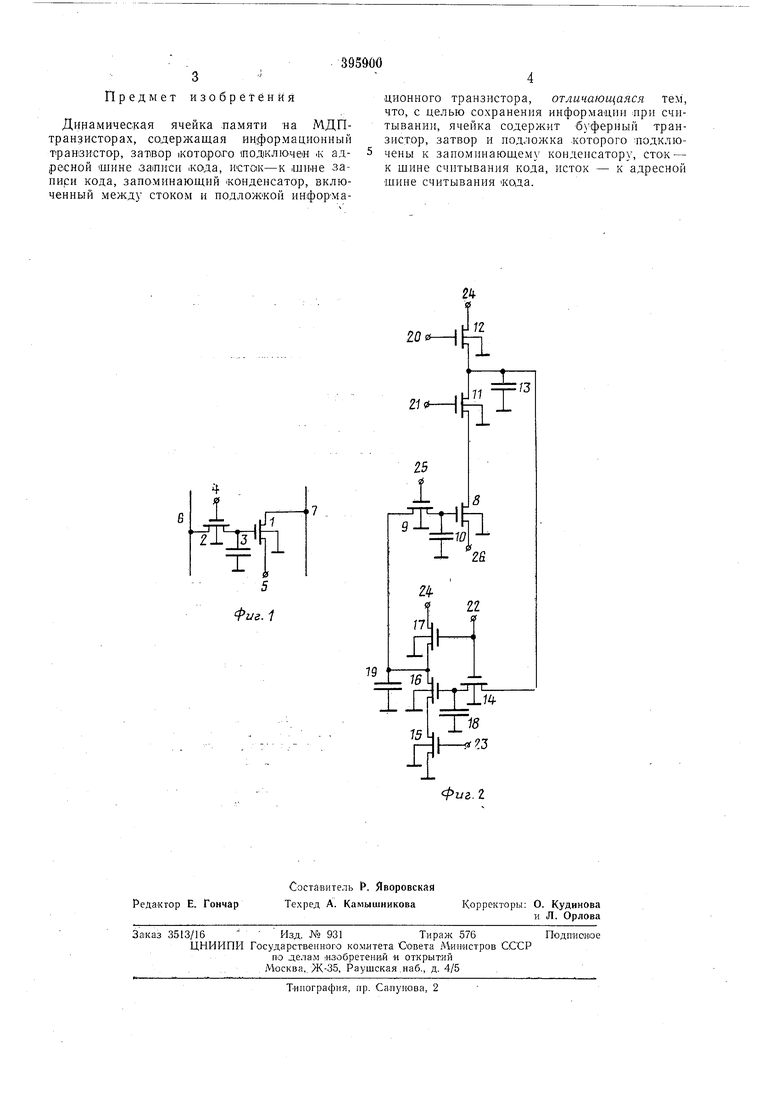

На фиг. 1 лриведена схема предлагаемой ячейки хранения; на фиг. 2 - схема, отражающая регенерацию кода в предлагаемой ячейке хранения.

Ячейка состоит из информационного транзистора /, транзистора записи 2, запоминающего конденсатора 3. Зажимы 4, 5 - адресные входы, соответственно, при записи и считывании .кода, шина 6 предназначена для записи кода в ячейку, шина 7 для считывания кода из ячейки.

На фиг. 2, кро.ме ячейки хранения (транзисторы 8-9, (Конденсатор /0), по каза1ны цепи вывода «ада (транзисторы И, 12, конденсатор 13) и 1ка1окад обратной связи (тр.аНЗИ1Сторы М-17, конденсаторы 18, 19). Зажнмы 20-23 - шины тактовых импульсов, 24 - шина источника питания. Сигналы записи и считывания поступают соответственно на входы 25 и 26.

В течение действия на шине 20 первого тактового импульса заряжается конденсатор 13, так как сигнал считывания на входе 26 отсутствует и напряжение истока (относительно общей точки) равно напряжению питания схемы. Во времядействия на шине 21 второго тактового импульса сигнал считывания, -поступающий на вход 26, понижает потеициал истока транзистора 8 до нуля и сигнал, хранимый на коиденсаторе 10, создает условие для разряда конденсатора 13. Заряд с этого конденсатора во время действия на входе 22 третьего тактового импульса переносится на конденсатор 18 и затем во время действия на входе 23 четвертого тактового имлульса - на конденсатор 19. Одновременно с первым тактовьгм импульсом сигнал записи 25 от1кры1вает тра«зистор 9 и .заряд С

конденсатора 19 переносится на конденсатор 10, восстанавливая на последнем исходный уровень.

За.пись и считывание информации в пред латаемой и известной ячейках памяти аналогичны.

Предл ет изобретения

Дирамическая ячейка .памяти на МДПтрандисторах, содержащая информационный транвистар, затвор iKOTOiporo шсдключеи .к ад1ре.сной шине зашиси .кода, исток-к ,ши«е записи кода, запоминающий конденсатор, включенный между стоком и подложкой информационного транзистора, отличающаяся тем, что, с целью сохранения информации лри считывании, ячейка содержит буферный транзистор, затвор и подложка .которого подключены к запоминающему конденсатору, сто-к - к щине считывания кода, исток - к адресной щине считывания «ода.

| название | год | авторы | номер документа |

|---|---|---|---|

| Полупроводниковая ячейка памяти | 1976 |

|

SU723680A1 |

| Ячейка памяти на мдп-транзисторах | 1975 |

|

SU533988A1 |

| Элемент памяти для ассоциативного накопителя | 1976 |

|

SU690565A1 |

| Ячейка памяти | 1977 |

|

SU693437A1 |

| Оперативное запоминающее устройство на мдп-транзисторах | 1978 |

|

SU769628A1 |

| Оперативное запоминающее устройство на мдп-транзисторах | 1974 |

|

SU744726A1 |

| Запоминающее устройство с перезаписью информации | 1974 |

|

SU570920A1 |

| ЯЧЕЙКА ПАМЯТИ ДЛЯ БЫСТРОДЕЙСТВУЮЩЕГО ЭСППЗУ С УПРАВЛЯЕМЫМ ПОТЕНЦИАЛОМ ПОДЗАТВОРНОЙ ОБЛАСТИ | 2011 |

|

RU2465659C1 |

| КРЕМНИЕВЫЙ МУЛЬТИПЛЕКСОР | 2015 |

|

RU2602373C1 |

| Запоминающий элемент на мдп транзисторах | 1973 |

|

SU450230A1 |

П

Z001

/3

Z1

25 1

тН

-i- ffi

Авторы

Даты

1973-01-01—Публикация