(54; ДЕЛИТЕЛЬ ЧАСТОТЫ ИМПУЛЬСОВ С РЕГУЛИРУЕМЫМ КОЭФФИЦИЕНТОМ ДЕЛЕНИЯ

| название | год | авторы | номер документа |

|---|---|---|---|

| Умножитель частоты с переменным коэффициентом умножения | 1977 |

|

SU743180A1 |

| Цифровой частотомер | 1973 |

|

SU481851A1 |

| Устройство для вычисления полиномов | 1978 |

|

SU792263A1 |

| Цифровой анализатор фазового кепстра | 1980 |

|

SU960655A1 |

| Цифровой частотомер | 1973 |

|

SU447637A1 |

| Синтезатор интервалов времени | 1986 |

|

SU1406558A1 |

| ПРЕОБРАЗОВАТЕЛЬ НИЗКИХ И ИНФРАНИЗКИХ ЧАСТОТ В ЦИФРОВОЙ КОД | 1970 |

|

SU277415A1 |

| Синтезатор частот | 1984 |

|

SU1293841A1 |

| Число-импульсное арифметическое устройство | 1980 |

|

SU951303A1 |

| Преобразователь активной мощности трехфазной электрической цепи в цифровой код | 1977 |

|

SU739736A1 |

Изобретение относится к импульсной тех- ншсе.

Известен делитель частоты с регулирув мым коэффициентом деления, содержащий реверсивный счетчик с п+1 счетными ячей- j ками, соединенными друг с другом через вентильные ячейки. Оба выхода каждой ячейки кроме последней соединены с переключаюшим устройством, параллельные входы которого соединены с основными или дополнитель-Q ным входами каждой ячейки. В состав выходного блока вводят логические элементы НЕ-И и НЕ-ИЛИ l.

Данный делитель сложен.

Наиболее близок к предлагаемому дели- jj гель, содержащий два умножителя частоть импульсов, каждый из которых состоит из последовательно соединенных триггеров и потенхшально-импульсных ключей, один-вход каждого из которых соединен с выходом jO соответствующего триггера умножителя, вторые входы подключены к источникам сигнала установки делителя и делимого коэффициента деления, а выходы объединены, причем выходы ключей первого умножителя частоты 25

импульсов соединены с первым входом логического элемента Запрет, второй вход которого соединяется с источником входного сигнала 2J.

Недостаток данного делителя - невозмох ность управления сигналами в двоично-десятичном коде.

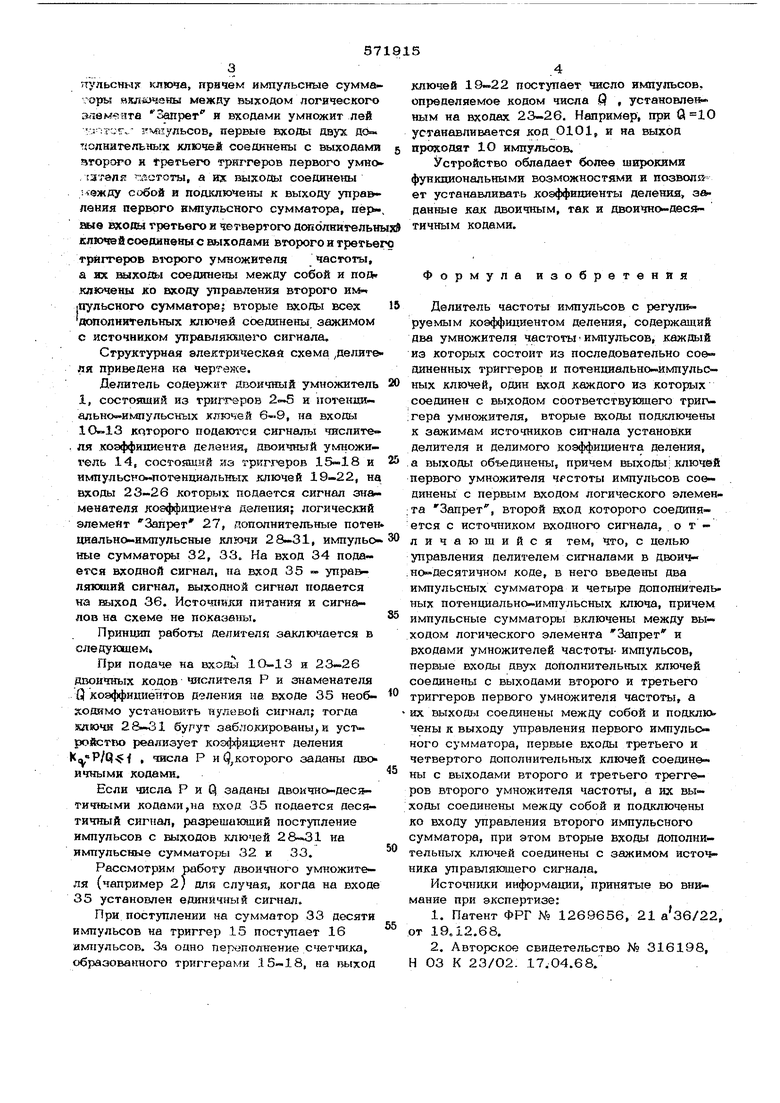

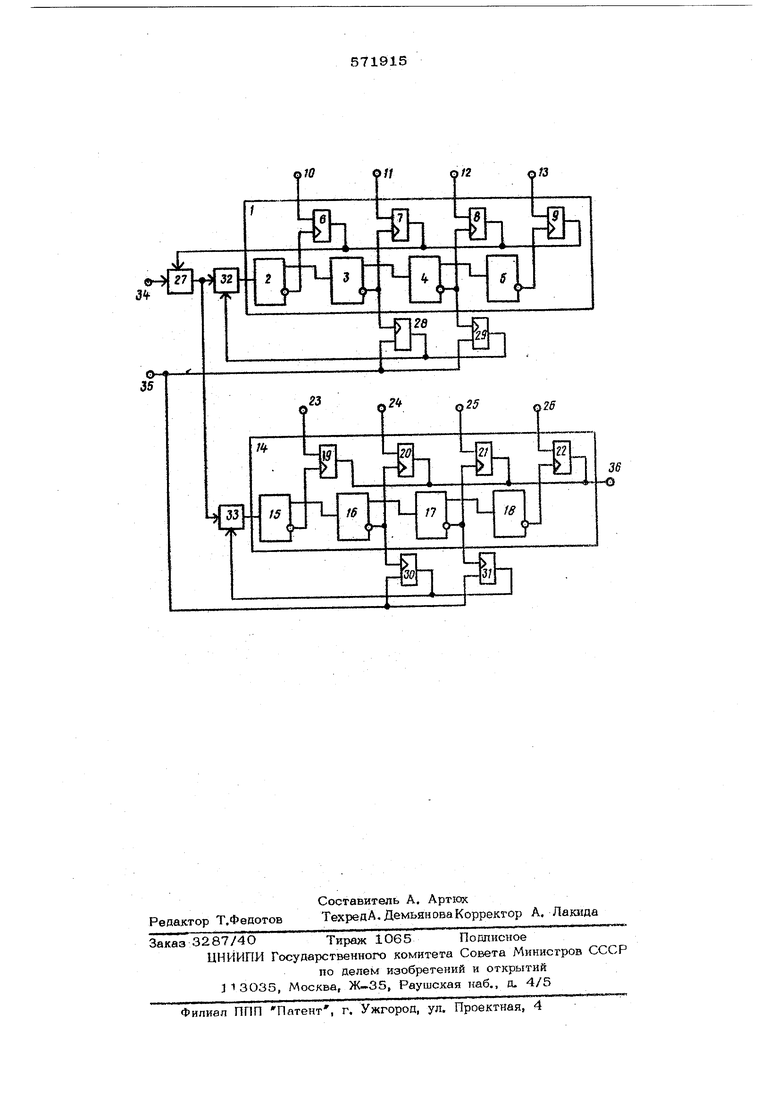

ЦеЛь изобретения - управление делителем сигналами в двоично-десятичном коде - доотигается тем, что в делитель частоты, содержаший два умножителя частоты импульсов каждый из которых состоит из последовательно соединенных триггеров и потендайльноимпульсных ключей, один вход каждого из которых соединен с выходом соответствукм щего триггера умножителя, вторые входы подключены к зажимам источников сигнала установки делителя и делимого коэффициента деления, а выходы объединены, причем исходы ключей первого умножителя частоты импульсов соединены с первым входом логического элемента Запрет, второй вход которого соединяется с источником входтюго сигнала, введены два импульсных сумматора « четыре дополнительных потенциально-ямттульснык ключа, причем импульсные сумматоры между выходом логического элемента Запрет я входами умнтекит лей :д-:т:;г з чсйульсов, первые входы двух до ; олнательнь х ключей соешгаены с выходами второго и третьего триггеров первого умно , гйстоты, а яэс выходы соединены 9жду собой и подключены к выходу упра& лвния первого импульсного сумматора, перныв вховы третьего и четвертого дополнительн лючей соединены с выходами второго я третье триггеров В1юрого умножителя частоты, а их кыхояы соединены между собой и под ключены ко входу управления второго им« (Пульсного сумматоре вторые входы всех дополнительных ключей соедзгаены зажимом с источником управляющего сигнала. Структурная электрическай схема делителя приведена ка чертеже. Делитель содержит Двоичный умножитель i, состоящий из триггеров 2™5 и потенхшально импульсных ключей 6-9, на входы которого подакпся сигналы числите. ля коэффициента деления, двоичный умножитель 14, состоящий из триггеров 15-18 и импульсио потенциальных ключей 19-22, на входы 23-26 которых подается сигнал зн&менателя коэффициента деления; логический элемент Запрет 27, дополнительные потен 1Иально-импульсные ключи 28-31, импульоные cyMMaTOffci 32, 33. На вход 34 подается входной сигнал, на вход 35 - управЛ5ПСШИЙ сигнал, выходной сигнал подается на выход 36. Источники питания и сигналов на схеме не показаны. Принцип работы делителя заключается в следующем При подаче на входы 1О-13 и 23-26 двоичных кодов числителя Р и знаменателя и коэффициентов дэления на входе 35 необходимо установить нулевой сигнал; тогда ключи 26-31 бупут заблоккрованы и уст ройство реализует коэффициент деления J i P/Q-S -f , числа Р и Q KOTOporo заданы дво ичными кодами. Если числа Р и Q заданы двоично-десятичными кодами,на кход 35 подается десятичный сигнал, разрешающий поступление импульсов с выходов ключей на импульсные сумматоры 32 и 33. Рассмотрим работу двоичного умножителя (например 2; длк случая, когда на входе 35 установлен единичный сигнал. При поступлении на сумматор 33 десяти импульсов на триггер 15 поступает 16 импульсов. За одно перополнение счетчика, образованного триггерами 15-18, на выход ключей поступает число импульсов, определяемое коном числа И , установленным на входах 23-26. Например, гфи Q 10 устанавливается код 0101, и на выход проходят 1О импульсов. Устройство обладает более широкими функциональными возможностями и позволь ет устанавливать коэффициенты деления, заданные как двоичным, так и двоично«-деся тичным кодами. Формула изобретения Делитель частоты импульсов с регулируемым коэффициентом деления, содержащий два умножителя частоты импульсов, каждый из которых состоит из последовательно соединенных триггеров и потенциально-импульсных ключей, один вход каждого из которых соединен с выходом соответствующего триггера умножителя, вторые входы подключены к зажимам источников сигнала установ;ки делителя и делимого коэффициента деления. а выходы объединены, причем выходы; ключей первого умножителя чрстоты импульсов сое- динены с первым входом логического элемента Запрет, второй вход которого соединяется с источником входного сигнала, о т личаюшийся тем, что, с целью управления делителем сигналами в двоично-десятичном коде, в него введены два импульсных сумматора и четыре дополнительных потенциально-импульсных ключа, причем импульсные сумматоры включены между выходом логического элемента Запрет и входами умножителей частоты- импульсов, первые входы двух дополнительных ключей соединены с выходами второго и третьего триггеров первого умножителя частоты, а их выходы соединены между собой и подклю чены к выходу управления первого импульсного сумматора, первые входы третьего и четвертого дополнительных ключей соединены с выходами второго и третьего трегге- ров второго умножителя частоты, а их выходы соединены между собой и подключены ко входу управления второго импульсного сумматора, при этом вторые входы дополнительных ключей соединены с зажимом источника управляющего сигнала. Истошики информации, принятые во внимание при экспертизе: 1.Патент ФРГ № 1269656, 21 азб/22, от 19Л2.68. 2.Авторское свидетельство № 316198, И 03 К 23/02. 17.04.68.

Авторы

Даты

1977-09-05—Публикация

1976-05-18—Подача