1

Изобретение относится к области вычислительной техники и может найти нрименепие в системах телеуправления и связи.

Известны шифраторы и дешифраторы, построенные на основе графов кодовых нересече 1ий, содержаш,ие регистр сдвига и ключи.

Однако с их помощью невозможно без изменения структуры поочередно работать в режимах шифратора и дешифратора.

Целью изобретения является расширение функциональных возможностей устройства.

Это достигается за счет того, что выход каждой ячейки регистра сдвига через входные ключи соединен с выходом шифрации, пулевой вход деншфрации подключен ко входам записи нечетных ячеек регистра сдвига, а единичный вход дешифрации - ко входам записи четных ячеек регистра сдвига.

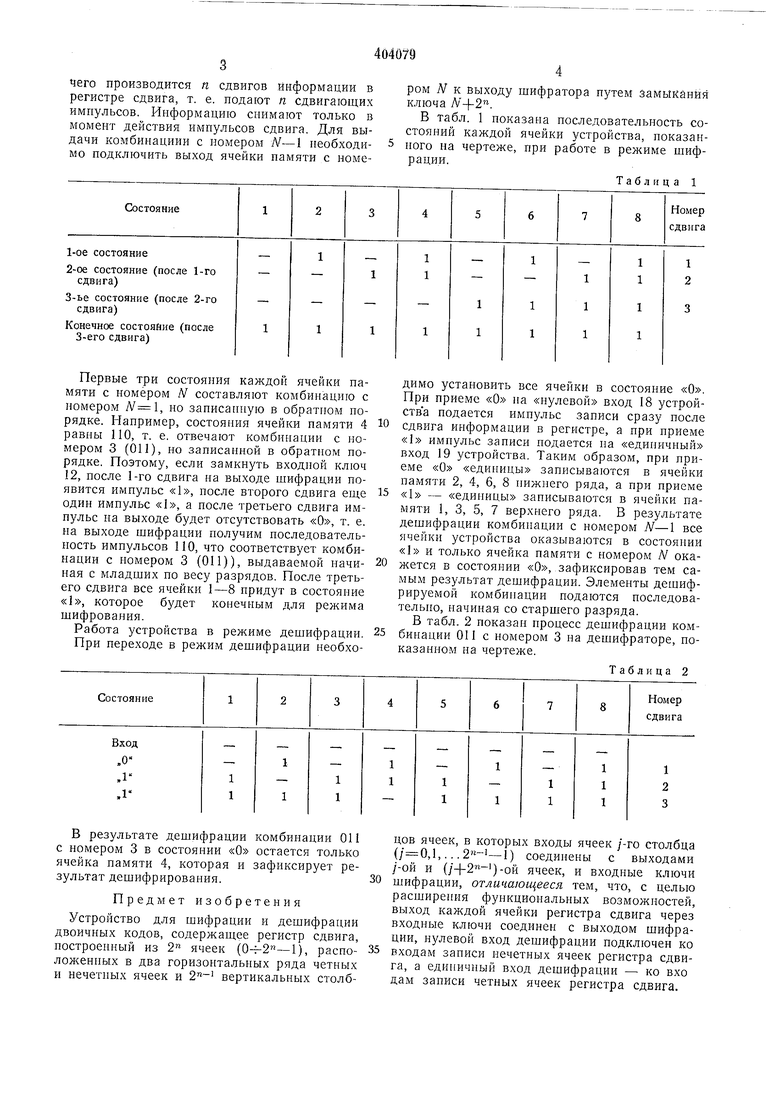

Блок-схема предложенного устройства приведена на чертеже. Устройство содержит: ячейки 1-8 памяти регистра сдвига, входные ключи 9-16, выход 17 шифрации, входные шины записи 18 и 19, выходы 20-27 дешифрации, схемы «ИЛИ 28-31. Шина сдвига иа чертеже не показана. Для установки схемы в исходное состояние в режимах шифрации и дешифрации можно использовать шину сдвига и входную шину заниси 18.

В режиме шифрации исходным состоянием является состояние «О ячеек 2, 4, 6, 8 нижне2

го ряда. Установка исходного состояния в этом случае осуществляется в два этана: сначала все ячейки 1-8 переводятся в состояние «О путем подачн па шину сдвига имнульса большой длительности, а затем ячейки 2, 4, 6, 8 нижнего ряда переводятся в состояние «1 за счет имнульса на входную шипу записи 18. В режиме дешифрации исходпым является состояние «О всех ячеек, в которое они могут быть переведены путем подачи на ншну сдвнга имнульса больнюй длительности, благодаря чему перенос информации из ячейки в ячейку невозможен {стнранне информации).

Мы рассматриваем двоичные коды без избыточносчи. Отнесем каждой комбинации

(Sj 0,1)номер 1

л-1 ®п-2 в

номер

п-1

N E i2-i + + ... + в„ у; е,2.

Очевидно .

Работа устройства в режиме шифрации.

Каждая ячейка памяти с номером /V генерирует комбинацию с номером V-1, начинал с младших разрядов. С этой целью неред началом работы все ячейки 2, 4, 6, 8 нижнего ряда устанавлнваются в состояннн «1, а

верхнего ряда - в состояние «нуля, после чего производится п сдвигов информации в регистре сдвига, т. е. подают п сдвигающих импульсов. Информацию снимают только в момент действия импульсов сдвига. Для выдачи комбинациии с номером Л-1 пеобходи- 5

мо подключить выход ячейки памяти с номерации.

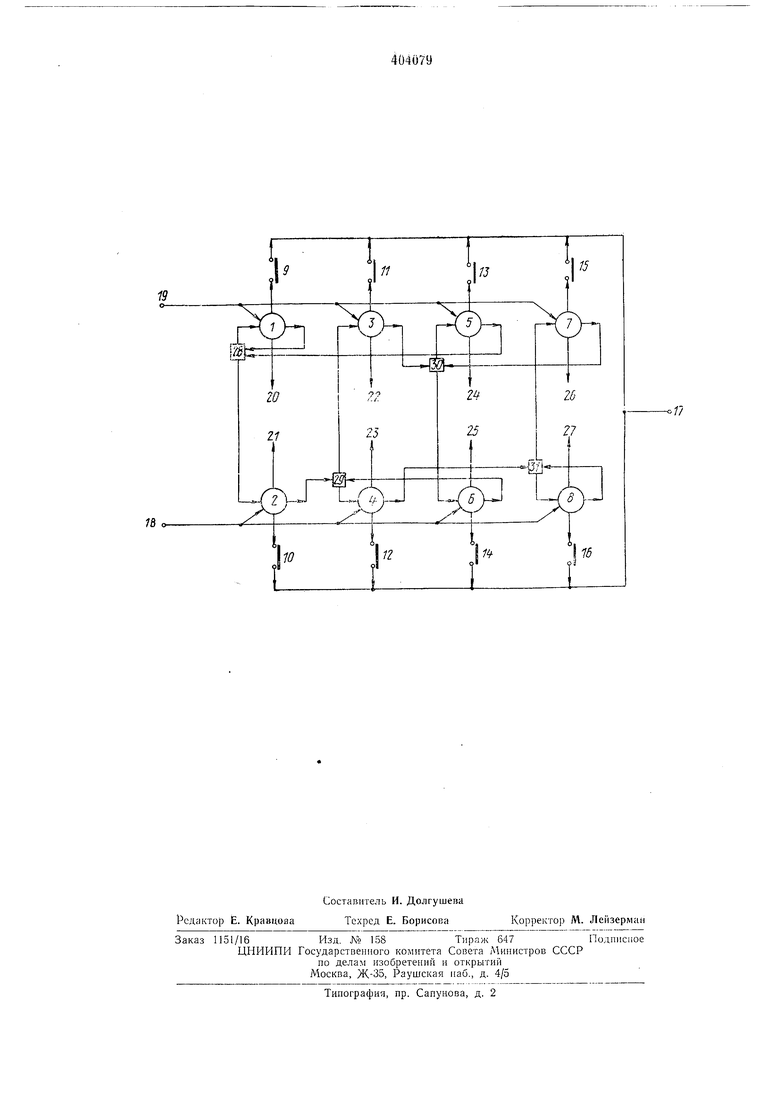

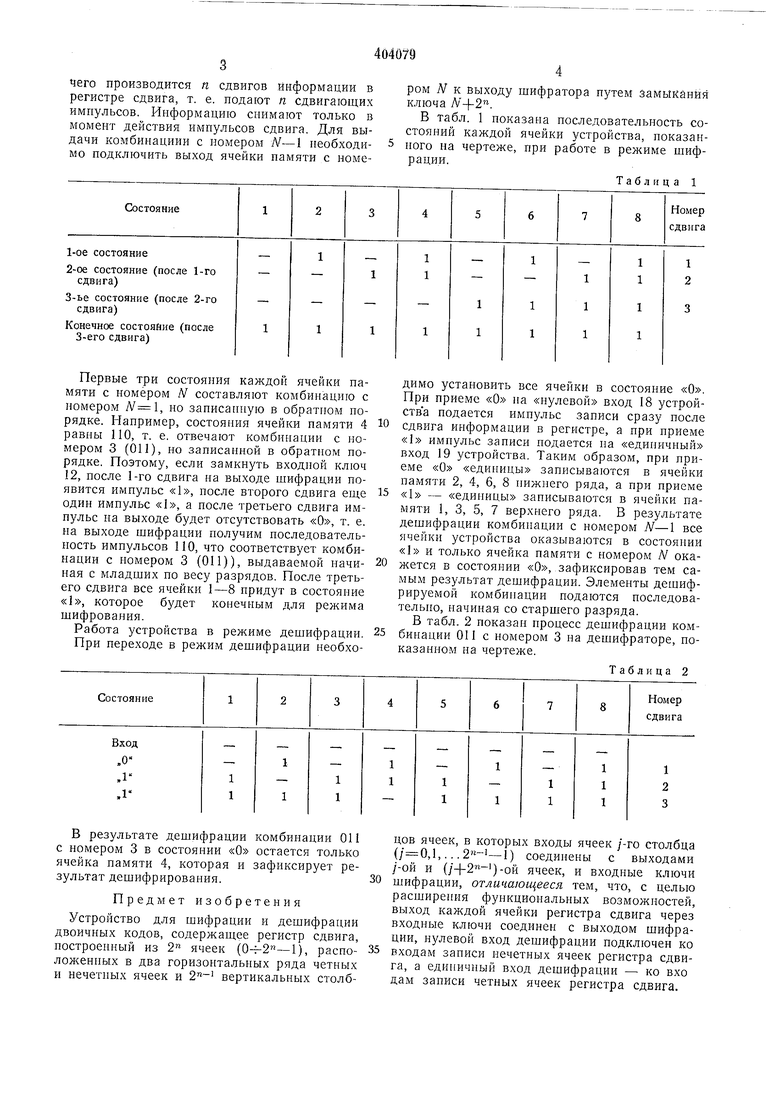

Таблица 1 ром N к выходу П1ифратора путем замыкйнйя ключа Л4-2. В табл. 1 показана последовательность состояний каждой ячейки устройства, показанцого на чертеже, при работе в режиме шиф

| название | год | авторы | номер документа |

|---|---|---|---|

| ПАНЕЛЬ ЖИДКОКРИСТАЛЛИЧЕСКОГО ДИСПЛЕЯ (ПЖКД) И СПОСОБ ЕЕ УПРАВЛЕНИЯ | 1993 |

|

RU2122242C1 |

| СИСТЕМА ЗАСЕКРЕЧЕННОЙ ПЕРЕДАЧИ И ПРИЕМА РЕЧЕВОЙ ИНФОРМАЦИИ, СИСТЕМА СИНХРОНИЗАЦИИ ДЛЯ СИСТЕМЫ ЗАСЕКРЕЧЕННОЙ ПЕРЕДАЧИ И ПРИЕМА РЕЧЕВОЙ ИНФОРМАЦИИ И УСТРОЙСТВО ШИФРАЦИИ ИЛИ ДЕШИФРАЦИИ ИНФОРМАЦИИ ДЛЯ СИСТЕМЫ ЗАСЕКРЕЧЕННОЙ ПЕРЕДАЧИ И ПРИЕМА РЕЧЕВОЙ ИНФОРМАЦИИ | 1996 |

|

RU2099885C1 |

| Дешифратор времяимпульсных кодов | 1991 |

|

SU1807562A1 |

| Арифметическое устройство с микропрограммным управлением | 1988 |

|

SU1559341A1 |

| Цифровое устройство для управления ведомым сетью преобразователем | 1986 |

|

SU1381668A1 |

| Арифметическое устройство с микропрограммным управлением | 1988 |

|

SU1541594A1 |

| Арифметическое устройство с микропрограммным управлением | 1988 |

|

SU1559340A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1971 |

|

SU289448A1 |

| Устройство для управления шаговым двигателем | 1977 |

|

SU663058A1 |

| Асинхронный регистр сдвига | 1980 |

|

SU1015441A1 |

Первые три состояния каждой ячейки памяти с номером N составляют комбинацию с номером , но записанную в обратном порядке. Например, состояния ячейки памяти 4 равны 110, т. е. отвечают комбинации с номером 3 (011), но записанной в обратном порядке. Поэтому, если замкнуть входпой ключ 12, после 1-го сдвига на выходе шифрации появится импульс «1, после второго сдвига еще один импульс «1, а после третьего сдвига импульс па выходе будет отсутствовать «О, т. е. на выходе шифрации получим последовательность импульсов ПО, что соответствует комбинации с номером 3 (011)), выдаваемой начиная с младщих по весу разрядов. После третьего сдвига все ячейки 1-8 придут в состояние «1, которое будет конечным для режима щифрования. Работа устройства в режиме дешифрации. При переходе в режим дешифрации необхоВ результате дешифрации комбинации 011 с номером 3 в состоянии «О остается только ячейка памяти 4, которая и зафиксирует результат дешифрирования.

Предмет изобретения

Устройство для шифрации и дешифрации двоичных кодов, содержащее регистр сдвига, построенный из 2 ячеек (O-f-2 -1), расположенных в два горизонтальных ряда четных и нечетных ячеек и вертикальных столбцов ячеек, в которых входы ячеек /-го столбца (,1,... ) соединены с выходами /-ОЙ и (/-}-2 )-ой ячеек, и входные ключи шифрации, отличающееся тем, что, с целью расширения функциональных возможностей, выход каждой ячейки регистра сдвига через входные ключи соединен с выходом шифрации, пулевой вход дешифрации подключен ко входам записи нечетных ячеек регистра сдвига, а единичный вход дешифрации - ко вхо дам записи четных ячеек регистра сдвига. димо установить все ячейки в состояние «О. При приеме «О на «нулевой вход 18 устройства подается импульс записи сразу после сдвига информацни в регистре, а при приеме «1 импульс записи подается па «единичный вход 19 устройства. Таким образом, при приеме «О «единицы записываются в ячейки памяти 2, 4, 6, 8 нижнего ряда, а при приеме «1 - «единицы записываются в ячейки памяти 1, 3, 5, 7 верхнего ряда. В результате дешифрации комбинации с номером N-1 все ячейки устройства оказываются в состоянии «1 и только ячейка памяти с номером N окажется в состоянии «О, зафиксировав тем самым результат дешифрации. Элементы дешифрируемой комбинации подаются последовательно, начиная со старшего разряда. В табл. 2 показан процесс дешифрации комбинации 011 с номером 3 на дешифраторе, показанном на чертеже. Таблица 2

Авторы

Даты

1973-01-01—Публикация