ri-ретьего элементов соединены и являются вторым и четвертым входами ячейки памяти, а третьи входы первой

группы входов И второго и третьего элементов являются шестьом и пятым входами ячейки памяти.

| название | год | авторы | номер документа |

|---|---|---|---|

| Асинхронный регистр сдвига | 1982 |

|

SU1076951A2 |

| Асинхронный регистр сдвига | 1985 |

|

SU1259337A1 |

| Асинхронный последовательный регистр | 1983 |

|

SU1136216A1 |

| Асинхронный регистр сдвига на МДП-транзисторах | 1986 |

|

SU1411829A1 |

| Асинхронный последовательный регистр | 1987 |

|

SU1481859A1 |

| Асинхронный последовательный регистр на КМДП-транзисторах | 1987 |

|

SU1494041A1 |

| Асинхронный последовательный регистр на КМДП-транзисторах | 1987 |

|

SU1501168A1 |

| Асинхронный регистр сдвига | 1982 |

|

SU1119082A1 |

| Ячейка памяти для буферного регистра | 1980 |

|

SU905860A1 |

| Асинхронный последовательный регистр | 1987 |

|

SU1499406A1 |

1. АСИНХРОННЫ РЕГИСТР СДВИГА, содержащий ячейки памяти причем первый, второй и третий выходы каждой четной ячейки памяти соединены соответственно с первым, вторым и третьим входами предыдущей нечетной ячейки памяти, а четвертый и пятый входы каждой нечетной ячейки памяти, кроме первой, соединены с вторым и третьим выходами предыдущей четной ячейки памяти, первый вход каждой чв«гной ячейки памяти, кроме последней, соединен с первьли выходом последующей нечетной ячейки памяти, а второй и третий входы каждои ч,етной ячейки памяти - с первым и вторым выходами предыдущей нечетной ячейки памяти, четвертый и пятый входы первой нечетной ячейки памяти ЯВЛ5ИОТСЯ вторым и третьим входами регистра, первый, второй и третий выходы последней четной ячейки памяти являются соответствующими выходами регистра, первый вход ц последней четной ячейки памяти является .чет:вертым входом регистра, первый выход первой нечетной ячейки памяти является четвертым выходом регистра, отличающийся тем, что, с целью упрощения регистра, в нем шестой вход каждой нечетной ячейки памяти, кроме последней, соединен с вторым выходом следующей нечетной ячейки памяти, а четвертый, питый и шестой входы каждой четной ячейки памяти, кроме первой, соединены соответственно с первым, вторым и третьим выходами предыдущей четной ячейки памяти, четвертый вход первой четной ячейки памя- .. ти является.первым входом регистра, шестой вход последней нечетной ячей ки памяти - пятым входом регистра, второй выход первой нечетной ячейки памяти - пятым выходом регистра. 2, Регистр сдвига по п. 1, о т§ л и ч а ю щ и и с я тем, что каждая его нечетная ячейка памяти выполне(П на в виде двухстабильного триггера, состоящего из двух элементов И-ИЛИс НЕ, имеющих две группы входов И, причем выходы первого и второго элементов И-ИЛИ-НЕ соединены с входами С2 второй группы входов И йторого и первого элементовИ-ИЛИ-НЕ и являются первым и вторым выходами памяти, входы первой группы входов И первого элемента И-ИЛИ-НЕ явсл ляются вторым, третьим и шестым входами ячейки памяти, а соответствую4 щие входы второго элемента И-ИЛИ-НЕ первым, четвертым и пятым входами i ячейки Пс1мяти. : 3. Регистр сдвига по n.l. 6 jлйчающийся тем, что кажда :его четная ячейка памяти выполнена в виде трехстабильного триггера, Состоящего из трех элементов И-ИЛИ-НЁ, . имеющих по двегруппы входов И, причем выходы каждого элемента соединены с входами второй группы вхо1дов И других элементов и являются выходами ячейки памяти, входы первой группы входов И первого элемента являются первым и третьим входами ячейки;памяти, первый и второй входы первой группы входов И второго и

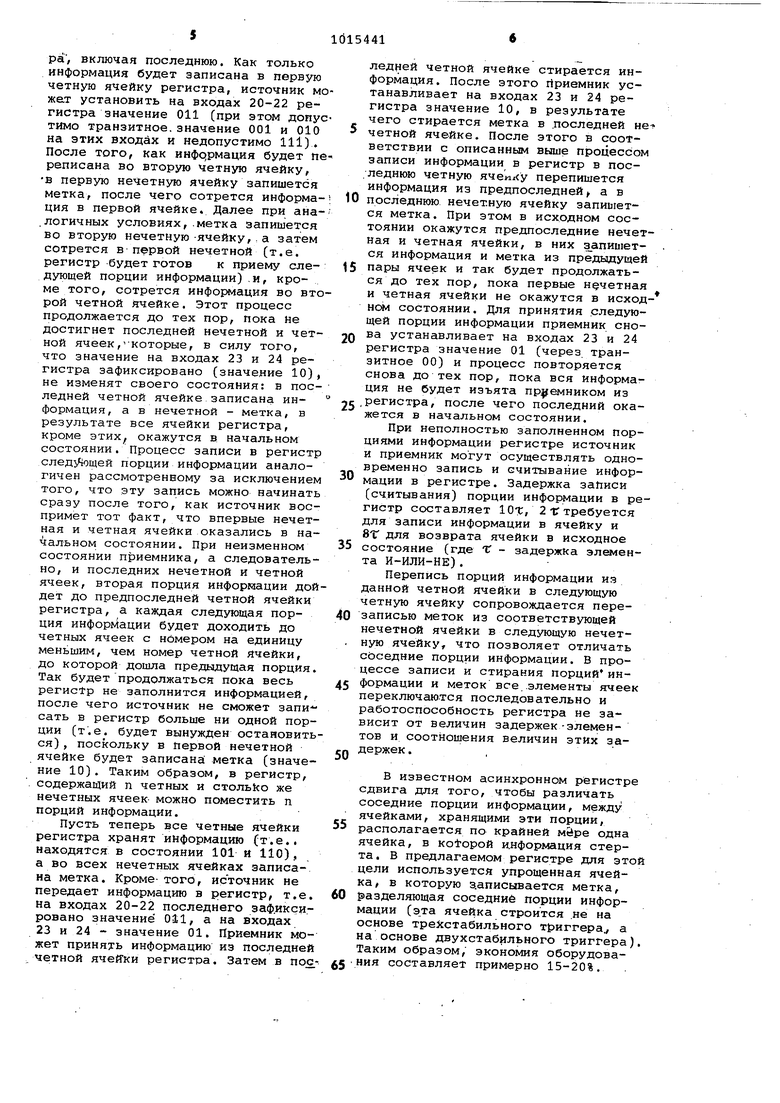

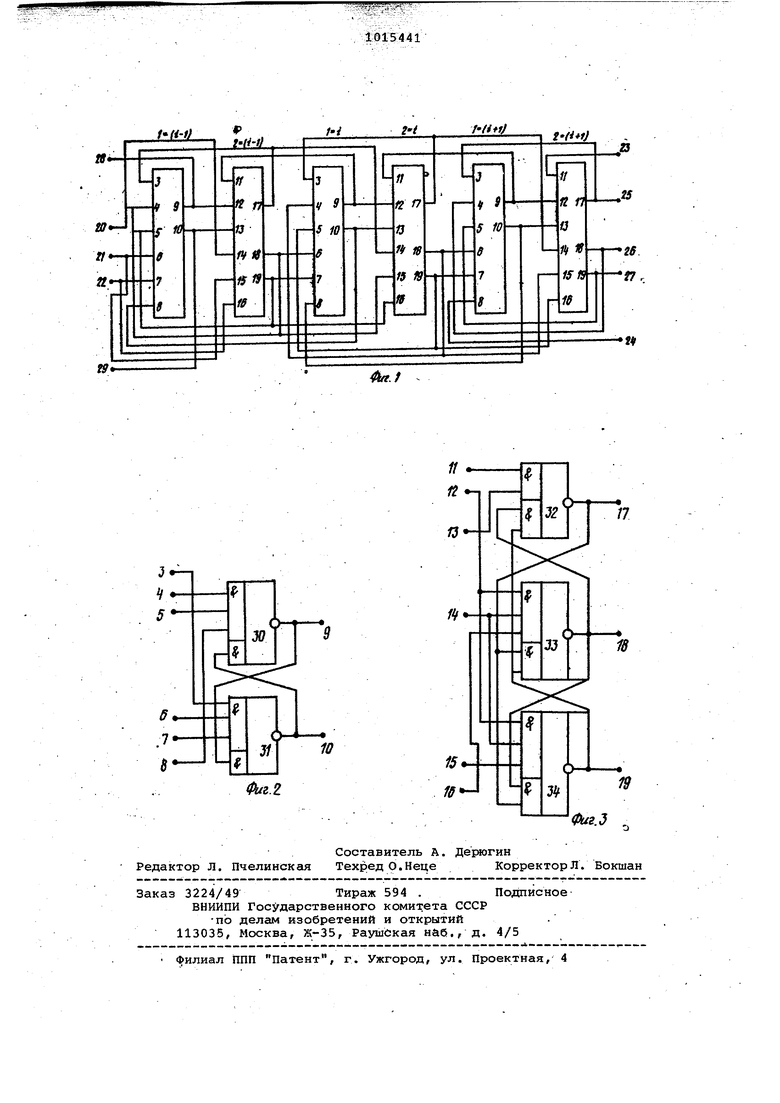

Изобретение относится к автомати ке и вычислительной технике и Может быть использовано при построении цифровых вычислительных машин. Известен аоинхронный регистр сдв га входы каждой ячейки памяти которого соединены с выходами предыдущей и последующей ячеек, а входы и выходы первой и последней ячеек сое динены с выходами и входами источни ка и приемника информации соответст венно. Управление регистром в режиме Запрос-ответ осуществляется источником (при заполнении регистра информацией) и приемником (при считывании информации из .регистра) . Ре гистр может одновременно воспринимать информацинз из источника и пере давать в приемник ранее записанную в регистр информацию, т.е. обладает буферными свойствами СЧНедостаток известного регистра низкая надежность, так как он нераб тоспособен при определенном соотношении задержек элементов. Наиболее близок к предлагаемому .регистр, в котором каждая ячейка памяти построена по схеме трехстабильного триггера на трех элементах И-ИЛИ-НЕ и имеет шесть входов, причем три из них соединены с выходами предыдущей ячейки, а другие три с выходами последующей ячейки, а входы и выходы первой и последней ячеек соединены с выходами и входами источника и приемника информации соответственно. Регистр обладает вы сокой надежностью функционирования при любых величийах зa DLepжeк элемен тов и их соотношении И. Недостатком указанного регистра : является избыточность оборудования (для хранения п-раэрядного кода регистр должен содержать 2п ячеек памяти, построенных На трёх элементах И-ИЛИ-НЕ каждая). Цель изобретения - экономия оборудования асинхронного регистра сдв га. Поставленная цель достигается. . тем, что в асинхронном Е5егистре сдв га, ячейки памяти которого имею по шесть входов, первый, второй и третий выходы 1 аждой четной ячейки памяти соединены соответственно с первым, вторым и третьим входами V предыдущей нечетной ячейки памяти. а четвертый и пятый входы каждой нечетной ячейки памяти, кроме первой, соединены с вторым и третьим выходами предыдущей четной ячейки памяти, первый вход каждой четной ячейки памяти, кроме последней, соединен с первым выходом последующей нечетной ячейки памяти, а второй и третий входы каждой четной ячейки памяти - с первым и вторым выходами предыдущей нечетной ячейки памяти, четвертый и;,пятый входы первой нечетной ячейки памяти являются вторым и третьим входами регистра, первый, второй и третий выходы последней четной ячейки памяти являются соответствующими выходами регистра, первый вход последней четной ячейки памяти является четвертым входом регистра, первый выход первой нечетной ячейки памяти является четвертым выходом регистра, шестой вход каждой нечетной ячейки памяти, кроме последней, соединен со вторым выходом следующей нечетной ячейки памяти,, а четвертый , ПЯТЫЙ и шестой входы каждой четной ячейки памяти, кроме первой,, соединены соответственно с первым, вторым и третьим выходами пpe iыдyщей четной ячейки памяти, четвертый вход первой четной ячейки памяти является первым входом регистра, шестой вход последней нечетной ячей ки памяти - пятым входом регистра, второй выход первой йечетной ячейки памяти г- пятым выходом регистра. Кроме того, каждая нечетная ячейка памяти регистра выполнена в виде двухстабильного триггера, состоящего из двух элементов И-ИЛИ-НЕ, имеющих две -группы входов И, причем выходы первого и второго элементов И-ИЛИ-НЕ соединены с входами второй группы входов И второго и первого элементов И-ИЛИ-НЕ и являются первым и вторым выходами ячейки памяти, входы первой группы, входов И первого элемента И-ИЛИ-НЕ являются вторым, третьим и шестым входами ячейки памяти, а соответствующие входы второго элемента И-ИЛИ-НЕ - первым, четверть и пятым входами ячейки памяти, Каждая четная ячейка памяти регистра выполнена в виде трехстабильного триггера, состоящего из трех элементов И-ИЛИ-НЕ имеющих по две группы входов И, причем выходы каждого элемента соединены с входами второй группы входов И других элеме тов и являются выходами ячейки памя ти, входы первой группы входов И пе вого элемента являются первым и тре тьим входами ячейки памяти, первый и второй входы первой группы входов И второго и третьего элементов соединены и являются вторым и четверты входами .ячейки памяти, а третьи вхо ды первой группы входов И второго и третьего элементов являются шес1ым и пятым входами ячейки памяти. На фиг. 1 приведена схема асинхронного регистра сдвига; на фиг. 2 схема нечётной ячейки регистра} на фиг. 3 - схема четной ячейки (порядок входов и выходов ячеек задается сверху вниз). Регистр, содержит нечетные 1 (i-1), 1 1и1 (i 1) и четны 2(i-1),2 i и2 (i + 1) ячейки памяти. Каждая нечетная ячейка имеет входы 3-8 и выходы 9 и 10, каждая четная ячейка - входы 11-16 (И выходы 17-19. Входы 14-16 первой четной ячейки являются первым 20,. вторым-21 и третьим 22 входами регистра, вход 11 последней четной ячейки - четвертым входом 23, а вход 8 последней нечетной ячейки пятьв входом 24 регистра. Выходы 17-19 последней четной ячейки являются первым 25, вторым 26 и треть 27 выходс1ми регистра, а выходы 9 и 10 первой нечетной ячейки регистра его четвертым 28 и 29 выходами. Входы 3-5 ячейки Ifi соединены с выходами 17-19 ячейки 2 i, входы 6 и 7 - с входами 15 и 16 ячейки 2 i, а вход 8 - с выходом 10 ячей ки 1 (i + 1), входы 14-16 ячейки соединены с выходс1ми 17-19 ячейки 2 (i-1), входы 12 и 13 с выходами 9 и 10 ячейки 1 i, а вход 11 - с выходом 9 ячейки 1 (. Нечетная ячейка (фиг. 2) является двухд1габильным триггере, постро енным на двух элементах И-ИЛИ-НЕ 30 и 31, имеющих.две г зуппы входой И, причем выходы первого 30 и.второго 31 элементов соединены с входами вт рой группы вкодов И второго и первого элементов и являются первьыЭ и вторьш 10 выходами ячейки, входы первой группы входов И первого элемента 30 являются вторым 4,третьи) 5 и 1)естым 8 входами ячейки, а соот ветствующие входы второго элемента 31 - первым 3, четвертым 6 и пятым 7 входами ячейки. Четная ячейка (фиг. 3) является трехстабильным триггер ом, построеннъал на трех элементах И-ИЛИ-НЕ 32-3 имею1цих по две группы входов И, причем выходы каждого элемента сое- . динены с входами второй группы входов И других элементов и являются выходами ячейки 17-i9,. входы первой группы входов И первого элемента 32 являются первым 11 и третьим 13 .входами ячейки, первнй и второй входы первой группы входов И второго 33 и третьего 34 элементов соединены и являются вторым 12 и четвертым 14 ;Входами ячейки, а третьи входы первой группы входов И второго 33 и третьего 34 элементов являются шестым 16 и пятым 15 входами ячейки. Асинхронный регистр работает следующим образом. Состояния четной ячейки памяти (значения на ее выходах 17-19) соответствуют: 011 - информация в ячейке стерта, 101 - в ячейке зап.исана единица, 110 - в ячейке запиг сан нульJ Состояния нечетной ячейки памяти (значения на ее Выходах 9 и 10J соответствуют:10 - в ячейке записана метка, 01 - в ячейке метка стерта. Запись информации в четную ячейку 2 1 происхс 1ит, если в предыдущей четной ячейке 2 (i- 1) записана информация, а в нечетной ячейке стерта метка. Стирание информации в четной ячейке происходит, если в нечетной ячейке записана метка, а в нечетной ячейке 1 () метка стерта. Запись метки в нечетную ячейку происходит, когда в четную ячейку 2 Д записана информация, а в преда1дуь(ей четной ячейке 2 (1-.1) информация стерта. Стирание метки в нечетной ячейке , происходит, если в четнсЧ ячейке 2 1 информация стерта, а в следующей нечетнбй ячейке 1 (1+1) записана метка. Значения на входах 20-22 регистра соответствуют: 011 - источник не передает информацию, 101 - источник передает в регистр Itj 110 - ис-точник передает в регистр О. Значения на входах 23 и 24 регистра соответствуют: 01 - приемник готов при- нять информацию из регистра, 10 приемник не готов принять информацию из регистра. Пусть в начальном состоянии во всех нечетных ячейках регистра стерта метка (01), а во всех четных его ячейках информация стерта (011). Кроме того, приемник не готов принять информацию, на входах 23 и 24 имеется значение 10 и это значение не Меняется в течение всего времени работы регистра. Источник, установив на входах 20-22 регистра значение 101 (110), записывает в первую четную ячейку единицу (нуль) Эта информация, перезаписываясь из каждой четной ячейки в следующую четную, заполнит все четыре ячейки регистгpa, включая последнюю. Как только информация будет записана в первую четную ячейку регистра, источник мо жет установить на входах 20-22 регистра значение 011 Спри этом допус тимо транзитное.значение 001 и 010 на этих входах и недопустимо 111). После того, как инфррмация будет пе реписана во вторую четную ячейку, в первую нечетную ячейку запишется метка, после чего сотрется информация в первой ячейке. Далее при аналогичных условиях,.метка запишется во вторую нечетную -ячейку,,а затем сотрется в первой нечетной (т.е. регистр будет готов к приему следующей порции информации).и, кроме того, сотрется информация во вто рой четной ячейке. Этот процесс продолжается до тех пор, пока не достигнет последней нечетной и четной ячеек,-которые, в силу того, что значение на входах 23 и 24 регистра зафиксировано (значение 10), не изменят своего состояния: в последней четной ячейке записана информация, а в нечетной - метка, в результате все ячейки регистра, кроме этих/ окажутся в начальном состоянии. Процесс записи в регистр след Лощей порции информации аналогичен рассмотренному за исключением того, что эту запись можно начинать сразу после того, как источник воспримет тот факт, что впервые нечетная и четная ячейки оказались в начальном состоянии. При неизменном состоянии приемника, а следовательно, и последних нечетной и четной ячеек, вторая порция информации дой дет до предпоследней четной ячейки регистра, а каждая следующая порция информации будет доходить до четных ячеек с номером на единицу меньшим, чем номер четной ячейки, до которой дошла предыдущая порция Так будет продолжаться пока весь регистр не заполнится информацией, после чего источник не сможет записать в регистр больше ни одной порции (т.е. будет вынужден остановить ся) , поскольку в Первой нечетной ячейке будет записана: метка (значение 10). Таким образом, в регистр, . содержащий п четных и cтoльko же нечетных ячеек- можно поместить п порций информации. Пусть теперь все четные ячейки регистра хранят информацию (т.е.. находятся в состоянии 101 и 110), а во всех нечетных ячейках записана метка. Кроме- того, источник не передает информацию в регистр, т.е на входах 20-22 последнего зафикси ровано значение Oil, а на входах 23 и 24 - значение 01. Приемник мо жет принять информацию из последне четной ячейки регистра. Затем в по ледней четной ячейке стирается информация. После этого йриемник устанавливает на входах 23 и 24 регистра значение 10, в результате чего стирается метка в .последней не- четной ячейке. После этого в соответствии с описанным выше процессом Зсшиси информации в регистр в последнюю четную ячейку перепишется информация из предпоследней а в последнюю нечетную ячейку запиигется метка. При этом в исходном состоянии окажутся предпоследние нечетная и четная ячейки, в них з апиц1ется информация и метка из предыдущей пары ячеек и так будет продолжаться до тех пор, пока первые нечетная и четная ячейки не окажутся в исход- нем состоянии. Для принятия следующей порции информации приемник снова устанавливает на входах 23 и 24 регистра значение 01 (через транзитное 00) и процесс повторяется снова до тех пор, пока вся информация не будет изъята пр емником из регистра, после чего последний окажется в начальном состоянии. При неполностью заполненном порциями информации регистре источник и приемник могут осуществлять одновременно запись и считывание информации в регистре. Задержка записи (считывания) порции информации в регистр составляет 1 От, 2 ЧГ требуется для записи информации в ячейку и 8Т для возврата ячейки в исходное состояние (где Т - задержка элемента И-ИЛИ-НЕ). Перепись порций информации из данной четной ячейки в следующую четную ячейку сопровождается перезаписью меток из соответствующей нечетной ячейки в следующую нечетную ячейку, что позволяет отличать соседние порции информации. В процессе записи и стирания порций информации и меток все..элементы ячеек переключаются последовательно и работоспособность регистра не зависит от величин задержек-элементов и соотношения величин этих задержек. В известном асинхронном регистре сдвига для того, чтобы различать соседние порции информации, между ячейками, хранящими эти порции, располагается по крайней мире одна ячейка, в коТорой информация стерта . В предлагаемом регистре для этой цели используется упрощенная ячейка, в которую з.аписывается метка, 51азделяющая соседниб порции информации (эта ячейка строится .не на основе тре сстабильного т зиггера а на основе двухстабильного триггера). Таким образом, экономия оборудования составляет примерно 15-20%.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Перключатель магнитофона | 1977 |

|

SU661601A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1983-04-30—Публикация

1980-04-11—Подача