Изобретение относится к вычислительной технике.

В настоящее время передача цифровой информации между логическими вентилями в интегральных схемах на МОП-структурах с использованием четырехтактной логики осуществляется по индивидуальным коммутационным щинам (т. е. по шинам, соединяющим выход логического вентиля, передающего информацию, с входами логических вентилей, на которые эта информация должна передаваться). Индивидуальные коммутационные шины используются также при передаче цифровой информации между логическими вентилями, находящимися в разных интегральных схемах, т. е. между интегральными схемами.

Однако большое количество коммутационных шин, контактных площадок, сварных соединений, выводов корпуса, используемого для герметизации, увеличивает габариты кристалла интегральной схемы и корпуса, трудоемкость монтажа, а следовательно, и стоимость интегральной схемы.

Для уменьшения числа коммутационных шин между передающими и приемными вентилями предлагаемая схема содержит тактируемые проходные МОП-транзисторы, сток каждого из которых соединен с затвором соответствующего транзистора вентиля приемной группы, истоки проходных транзисторов

объединены и подключены к одному концу соединительной шины, второй конец которой подключен к объединенным выходам вентилей передающей группы, а затворы проходных транзисторов соединены с соответствующими шинами тактовых импульсов.

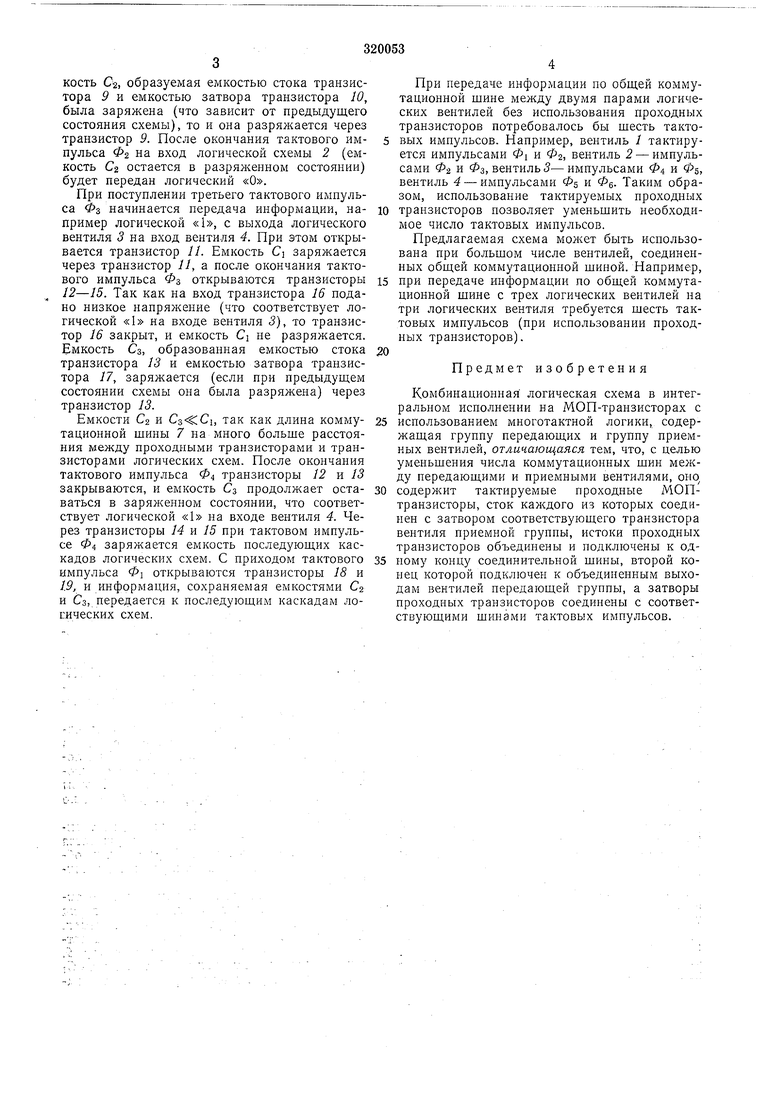

На чертеже представлена схема передачи информации в логических схемах на МОПструктурах между двумя независимыми парами логических вентилей с использованием четырехтактной логики.

Предположим, что необходимо передать информацию, например логический «О, с выхода инвертирующего логического вентиля / на логический вентиль 2 и логическую «I с выхода логического вентиля 5 на вентиль 4. В этом случае на вход (затвор транзистора 5) подано напряжение.

При подаче тактового импульса 0i на транзистор 6 последний открывается и заряжается емкость Сь образуемая диффузионными областями транзисторов и коммутационной шиной 7.

После окончания тактового импульса Ф емкость С продолжает сохранять свой заряд ввиду малых токов утечки в МОП-схемах. С приходом тактового импульса Ф2 открывается транзистор 8 и проходной транзистор 5. а так как открыт и транзистор 5, то емкость Cj

кость Cs, образуемая емкостью стока транзистора 9 и емкостью затвора транзистора 10, была заряжена (что зависит от предыдущего состояния схемы), то и она разряжается через транзистор 9. После окончания тактового импульса 02 на вход логической схемы 2 (емкость Сг остается в разряженном состоянии) будет передан логический «О.

При поступлении третьего тактового импульса Фз начинается передача информации, например логической «1, с выхода логического вентиля 3 на вход вентиля 4. При этом открывается транзистор 11. Емкость С заряжается через транзистор 11, а после окончания тактового импульса Фз открываются транзисторы 12-15. Так как на вход транзистора 16 подано низкое напряжение (что соответствует логической «1 на входе вентиля 3), то транзистор 16 закрыт, и емкость Cj не разряжается. Емкость Сз, образованная емкостью стока транзистора 13 и емкостью затвора транзистора 17, заряжается (если при предыдущем состоянии схемы она была разряжена) через транзистор 13.

Емкости Са и Сз-СС, так как длина коммутационной шины 7 на много больше расстояния между проходными транзисторами и транзисторами логических схем. После окончания тактового имнульса Ф транзисторы 12 и 13 закрываются, и емкость Сз продолжает оставаться в заряженном состоянии, что соответствует логической «1 на входе вентиля 4. Через транзисторы 14 и 15 при тактовом импульсе Ф4 заряжается емкость последующих каскадов логических схем. С приходом тактового импульса Ф открываются транзисторы 18 и 19, и информация, сохраняемая емкостями Cg и Сз, передается к последующим каскадам логических схем.

При передаче информации по общей коммутационной шине между двумя парами логических вентилей без использования проходных транзисторов потребовалось бы шесть тактовых импульсов. Например, вентиль / тактируется имнульсами Ф и Ф2, вентиль 2 импульсами Ф-2 и Фз, веитиль5-импульсами Ф и Фз, вентиль 4 - импульсами Фа и Фе. Таким образом, использование тактируемых проходпых

0 транзисторов позволяет уменьшить необходимое число тактовых импульсов.

Предлагаемая схема может быть использована при большом числе вентилей, соединенных общей коммутационной шиной. Например,

5 при передаче информации по общей коммутационной шине с трех логических вентилей на три логических вентиля требуется шесть тактовых импульсов (при использовании проходных транзисторов).

Предмет изобретения

Комбинационная логическая схема в интегральном исполнении на МОП-транзисторах с

5 использованием многотактной логики, содержащая группу передающих и группу приемных вентилей, отличающаяся тем, что, с целью уменьшения числа коммутационных шин между передающими и приемными вентилями, оно

0 содержит тактируемые проходные МОПтранзисторы, сток каждого из которых соединен с затвором соответствуюшего транзистора вентиля приемной группы, истоки проходных транзисторов объединены и подключены к одному концу соединительной шины, второй конец которой подключен к объединенным выходам вентилей передающей группы, а затворы проходных транзисторов соединены с соответствующими шинами тактовых импульсов.

| название | год | авторы | номер документа |

|---|---|---|---|

| Усилитель считывания | 1979 |

|

SU858093A1 |

| Дешифратор адреса | 1982 |

|

SU1068999A1 |

| Выходной усилитель | 1981 |

|

SU1015436A1 |

| В П ТБ h т^^1Щ1 ,-, -j-.• :,••..i,i j I | 1973 |

|

SU406298A1 |

| Постоянное запоминающее устройство | 1986 |

|

SU1388950A1 |

| Входное устройство для электронных часов | 1990 |

|

SU1774471A1 |

| Устройство для выборки адресов из блоков памяти | 1976 |

|

SU744722A1 |

| ДИНАМИЧЕСКИЙ ИНВЕРТОР НА ПОЛЕВЫХ ТРАНЗИСТОРАХ | 1969 |

|

SU235100A1 |

| Двухтактный сдвигающий регистр | 1968 |

|

SU736172A1 |

| Четырехфазный МДП-триггер | 1989 |

|

SU1628186A1 |

Даты

1971-01-01—Публикация