(54) ПОЛУПРОВОДНИКОВОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО

| название | год | авторы | номер документа |

|---|---|---|---|

| Полупроводниковое запоминающее устройство | 1979 |

|

SU788176A1 |

| Полупроводниковое запоминающее устройство | 1981 |

|

SU987679A1 |

| Усилитель считывания | 1981 |

|

SU1015435A1 |

| Постоянное запоминающее устройство | 1986 |

|

SU1388950A1 |

| Оперативное запоминающее устройство на мдп-транзисторах | 1974 |

|

SU744726A1 |

| Запоминающее устройство | 1985 |

|

SU1269209A1 |

| Адресный дешифратор для полупроводникового постоянного запоминающего устройства | 1980 |

|

SU960949A1 |

| Дешифратор на МДП-транзисторах | 1983 |

|

SU1455362A1 |

| Постоянное запоминающее устройство | 1979 |

|

SU841047A1 |

| Запоминающее устройство (его варианты) | 1983 |

|

SU1098035A1 |

Изобретение относится к области вычислительной техники, в частности к устройствам памяти на полупроводниковых приборах. Известно полупроводниковые запоминающие устройства (ПЗУ), одно из известных -полупроводниковых запоминающих устройств содержащее накопитель информации и дещифраторы. Од нако в таком устройстве выбор строки накопителя производится установ кой соответствующего кода адреса на входах дешифратора, что приводит к установлению нулевого потенциала на всех невыбранных строках и высокого потенциала на выбранной строке СП. При таком способе выборки время заряда емкости выбранной строки опре деляется сопротивлением нагрузочного транзистора дещифратора, что ограничивает быстродействие. Наиболее близким техническим решением к изобретению является ПЗУ 23 содержащее накопитель, дешифратор. транзисторы предзаряда, проходные транзисторы и нагрузочные транзисторы. Числовые щины накопителя предварительно заряжаются будучи отключенными от дещифратора при помо1Щ проходных транзисторов, которые закрыты в момент предзаряда. После отпирания проходных транзисторов происходит разряд невыбранных числовых щин накопителя через транзисторы дешифратора. Недостатком устройства является больщая площадь кристалла из-за наличия в каждой строке матрицы накопителя транзистора предзаряда, проходного транзистора и нагрузочного транзистора дещифратора. Кроме того, размеры указанных транзисторов ограничены шагом матрицы накопителя, что приводит к снижению быстродействия ПЗУ. Целью изобретения является упрощение и повышение быстродействия 1ВУ. Поставленная цель достигается тем, что в ПЗУ, содержащее накопитель, де(Шифратор, состоящий из ключевых тран зисторов и транзисторов заряда числовых шин,, при этом исток каждого транзистора заряда числовых шин соединен со стоками соответствующих ключевых транзисторов и с соответствующей числовой шиной накопителя, стоки подключены к источнику постоянного напряжения, а затворы,к первому источнику импульсного напряжения, и шину нулевого потенциала, введены управляющий транзистор, сток которого подключен к истокам транзисторов заряда числовых шин, исток - к шине нулевого потенциала, а затвор - ко второму источнику импульсного напряжения .

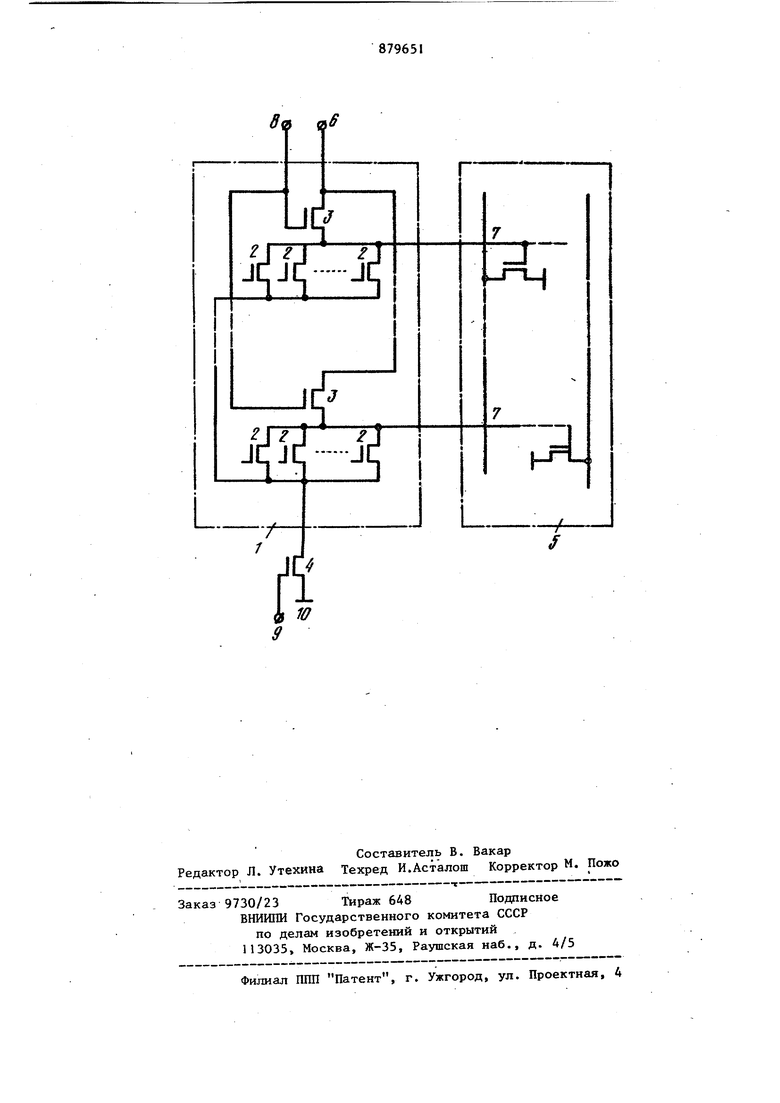

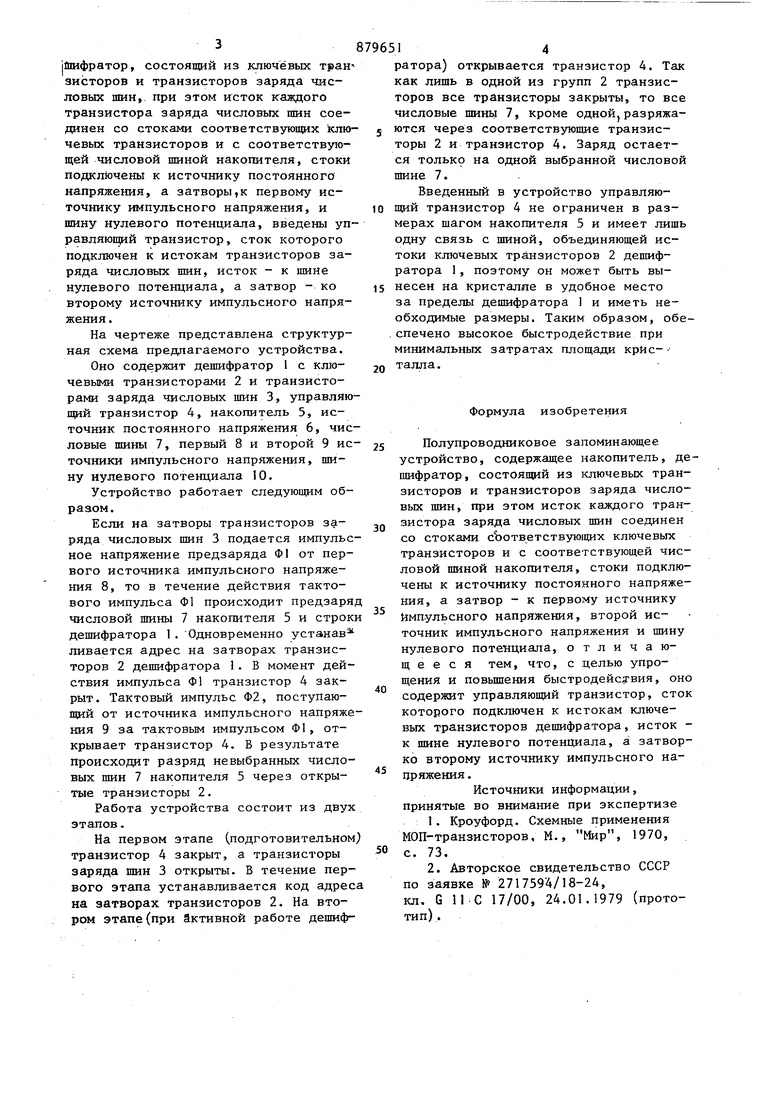

На чертеже представлена структурная схема предлагаемого устройства.

Оно содержит дешифратор 1 с ключевыми транзисторами 2 и транзисторами заряда числовых шин 3, управляюпщй транзистор 4, накопитель 5, источник постоянного напряжения 6, числовые шины 7, первый 8 и второй 9 источники импульсного напряжения, шину нулевого потенциала 10.

Устройство работает следующим образом.

Если на затворы транзисторов заряда числовых шин 3 подается импульсное напряжение предзаряда Ф1 от первого источника импульсного напряжения 8, то в течение действия тактового импульса Ф1 происходит предзаряд числовой шины 7 накопителя 5 и строки дешифратора 1. Одновременно устанав ливается адрес на затворах транзисторов 2 дешифратора 1. В момент действия импульса Ф1 транзистор 4 закрыт. Тактовый импульс Ф2, поступающий от источника импульсного напряжения 9 за тактовым импульсом Ф1, открывает транзистор 4. Б результате происходит разряд невыбранных числовых шин 7 накопителя 5 через открытые транзисторы 2.

Работа устройства состоит из двух этапов.

На первом этапе (подготовительном) транзистор 4 закрыт, а транзисторы заряда шин 3 открыты. В течение первого этапа устанавливается код адрес на затворах транзисторов 2. На втором этапе(при активной работе дешифратора) открывается транзистор 4. Так как лишь в одной из групп 2 транзисторов все транзисторы закрыты, то все числовые шинь 7, кроме одной, разряжаются через соответствуюшие транзисторы 2 и транзистор 4. Заряд остается только на одной выбранной числовой шине 7.

Введенный в устройство управляющий транзистор 4 не ограничен в размерах шагом накопителя 5 и имеет лишь одну связь с шиной, объединяющей истоки ключевых тра.нзисторов 2 дешифратора 1, поэтому он может быть вынесен на кристалле в удобное место за пределы дешифратора 1 и иметь необходимые размеры. Таким образом, обеспечено высокое быстродействие при минимальных затратах площади крИс-

талла.

Формула изобретения

Полупроводниковое запоминающее

устройство, содержащее накопитель, дешифратор , состоящий из ключевых транзисторов и транзисторов заряда числовых шин, при этом исток каждого транзистора заряда числовых шин соединен со стоками сЪответствующих ключевых транзисторов и с соответствующей числовой шиной накопителя, стоки подключены к источнику постоянного напряжения, а затвор - к первому источнику импульсного напряжения, второй источник импульсного напряжения и шину нулевого потенциала, отличающееся тем, что, с целью упрощения и повьш1ения быстродейс -вия, оно содержит управляющей транзистор, сток которого подключен к истокам ключевых транзисторов дешифратора, исток к пмне нулевого потенциала, а затворко второму источнику импульсного напряжения .

Источники информации, принятые во внимание при экспертизе

0 с. 73.

кл, G II С 17/00, 24.01.1979 (прототип).

.

/

/

Авторы

Даты

1981-11-07—Публикация

1979-12-20—Подача