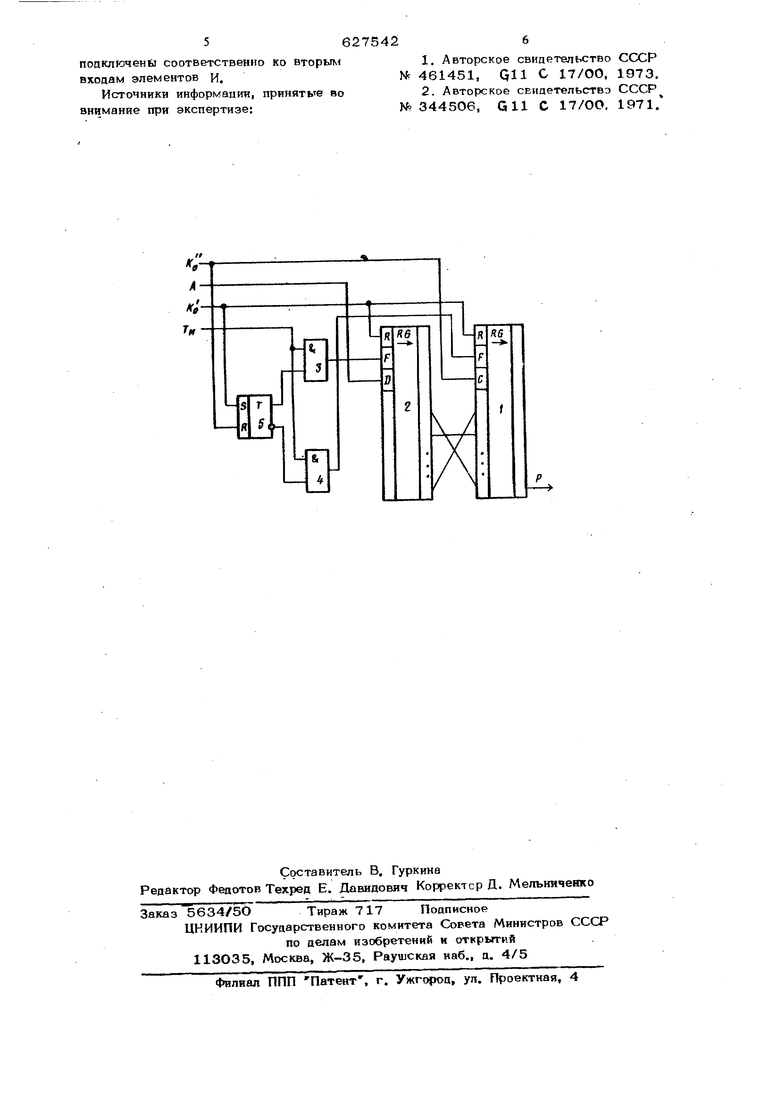

362 минающего устройства с фазо-импульсным представлением чисел. Устройство соперхшт блок местного управления (на чертеже не погсазан), числовой сдвигающий регистр 1, адресный сдвигающий регистр 2, элементы И 3,4, триггер 5. К- шина считывания, А - адресная шина, « - шина сброса, Ти - шина тактовых импульсов. Опишем работу постоянного запоминающего устройства при прямом кодировании числовой информации и при Я 1 где П - разрядность ПЗУ, а k - основа ние системы счисления. В это ПЗУ информация запис1 гвается коммутацией выходов разрядов адресного сдвигающего регистра 2 со входами соответствующих разрядов числового сдвигающего регистра 1. Для записи числа 1 ( 1 0,1, ... k-1) по адресу i { 0,1, , , . , , П -1) необходимо выход П- J -того разряда адресного сдв гающего регистра 2,подсоединить ко вхо K J-oro разряда числового сдвигающего регистра 1, Для считывания информации из ПЗУ по шине KQ на единичный вход & -триггера 5 и на нулевые входы числового и адресного сдвигаю щих регистров 1,2 подается сигнал сбр са. При этом оба регистра устанавлива ю ся в нуль, а триггер 5 переключается в единичное состояние. С началом опорного периода через элемент И 3 на вхо F цепи сдвига адресного регистра 2 поступают тактовые импульсы. В течение этого же опорного периода по шиие А на информационный вход Q адресного регистра 2 поступает единичный сигнал с фазой, соответствующей адресу считы ваемого сигнала. В дальнейиюм этот единичный сигнал с первого разряда адресного регистра 2 сдвигается тактовыми импульсами в сторону старших разрядов и в конце опорного периода фиксируется в П- j -этом разряде. . Перед началом следующего опорного периода по шине К, на нулевой вход 1 -тригг а 5 и на вход С (синхронизации) числового сдвигающего регистра 1 поступает сигнал, который переписывает единичный сигнал с П 3 -того разряда адресного сдвигающего регистра 2 на вход К-1-того раз ряда числового сдвигающего регистра 1 и переключает,триггер 5 в нулевое состояние. В этом случае через открыв шийся элемент И 4 тактовые импульсы поступают на вход F цепи сдвига числового сдвигающего регистра 1 и сдвигают записанный .в него единичный сигнал в сторону старших разрядов. После поступления тактового импульса с фазой i единичный сигнал сдвигается в К разряд числового сдвигающего регистра 1 и появляется на его выходе Р. Например, для записи числа i 8 по- адресу j -5 при 1 К 10 необходимо выход 5-го разряда адресного сдвигающего регистра 2 подсоединить ко входу 2-го разряда числового сдвигающего регистра 1, Если же И К или И К, для сдвига единичного сигнала в регистре с меньшей разрядностью используется меньшее число тактовых импульсов, т.е. опорный период в этом случае короче. В предлагаемом ПЗУ можно хранить одно многоразрядное число, представленное последовательны кодом, или И одноразрядных К -ичных чисел. Использование адресного и числового сдвигающих регистров для запоминания и считьюания информации позволяет значительно упростить и повысить надежность устройства. Формула изобретения Постоянное запоминающее устройство с фазо-импульсным представлением чисел, содержащее блок местного управления J выходы которого соединены соответственно с шинами считывания, сброса, адресной и тактовьтх импульсов, отличающееся тем, что, с целью его упрощения и повышения надёжности, в него введены адресный и числовой сдвигающие регистры, первые входы которых подключены к шине сброса, выход первого разряда адресного сдвигающего регистра подключен ко входу последнего разряда числового сдвигающего регистра, вход первого разряда которого подключён к выходу последнего разряда адресного сдвигающего регистра, все выходы других разрядов адресного сдвигающего регистра подключены соответственно Ко входам числового сдвигающего регистра, два элемента И, первые входы которых подключены к шине тактовых импульсов , а выходы - соответственно ко вторым входам адресного и числового сдвигающих регистров, третьи входы которых подключены соответственно к адресной шине и шине считывания, и триггер, единичный вход которого подключён к шине сброса, а нулевой - к шине считывания, в.ыходы-триггера

подключены соответственно ко вторык входам элементов и.

Источники информации, принятые во внимание при экспертизе:

1.Авторское свидетельство CCXlF № 461451. Q11 С 17/00. 1973.

2.Авторское свиаетельствэ СССР №344506, G11 С 17/ОО. 1971/

| название | год | авторы | номер документа |

|---|---|---|---|

| Постоянное запоминающее устройство | 1979 |

|

SU849303A1 |

| Запоминающее устройство | 1979 |

|

SU842967A1 |

| Постоянное запоминающее устройство | 1979 |

|

SU822292A1 |

| Устройство для упорядочения массива чисел | 1987 |

|

SU1494001A1 |

| Устройство для быстрого преобразования фурье | 1981 |

|

SU1018123A1 |

| Устройство для контроля блоков постоянной памяти | 1983 |

|

SU1125657A1 |

| Устройство для отображения информации на экране телевизионного приемника | 1988 |

|

SU1583967A1 |

| Запоминающее устройство | 1980 |

|

SU868835A1 |

| Аналого-цифровой преобразователь | 1985 |

|

SU1336237A1 |

| Устройство для сопряжения | 1983 |

|

SU1176337A1 |

Авторы

Даты

1978-10-05—Публикация

1976-11-03—Подача