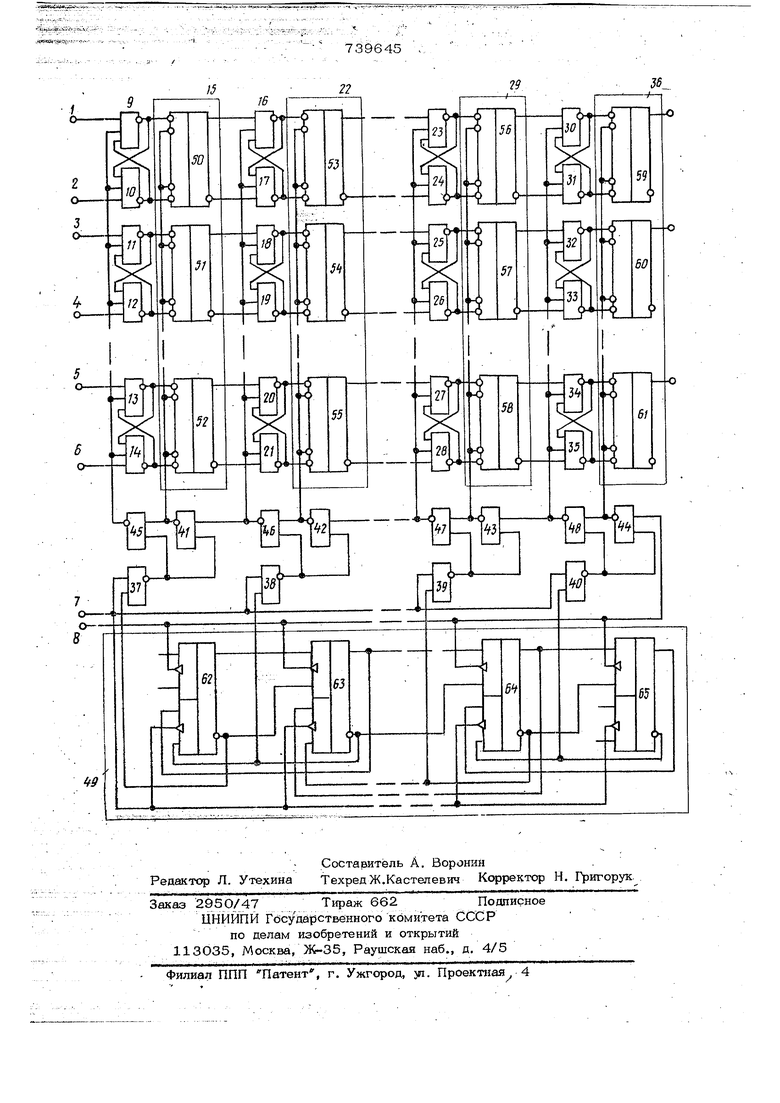

. . 1 Изобретение относится к области вьтчио лительной техники и может быть использовано при построении устройств для хр&нения даскретной информации. Известно буферное запоминающее уст ройство (БЗУ) , содержащее регистры хр&т нения чисел на PS-триггерах,одноименные разряды которых соединены последовательно, управляющий регистр сдвига, каждый разряд которого содержит основной и вспомогательный триггеры и элементы ИЛИ, И. НЕ 1 . Недостатком БЗУ является, низкое быс родействие, обусловленное тем, что управляющий регистр выполнен двухтактным. При этом для сдвига информации из одного регистра в другой требуется два разнесекных во времени синхроимпульса, а для за писй информации в п регистр требуется 2 п синхроимпульсов. Кроме того, управляющий регистр содержит большое количест во оборудования (два триггера и три эле-г мента И)..- . Наиболее блшким из известных по технической сущности к изобретеншо являе- ся устройство, которое содержит регистры хранения чисел на PS -триггерах, одно- име1шые разряды которых соединены последовательно через вентильные схемы И- НЕ, и управтающий реверсивный регистр сдвига 21. Недостатком устройства является низкое быстродействие, так как для записи информации в v регистр требуется последовательно разнесенных во времени синхроимпульсов. Кроме того, в устройстве использован дополнительный генератор синхросерий. Целью изобретения является повышение быстродействия устройства за счет записи и считывания информации в один такт. Поставленная цель достигается тем, , что в БЗУ, со держащее а информационных регистров и п групп первых элементов И-НЕ, причем один из входов в -го информационного регистра соединены с выходами первых элементов №-НЕ i группы 3 i , где n 1, 2, 3, ..., i . ...)t «дни из входов KOTOJpbix соединены выходами (i-i) информационного регистра, выходы информационного регистра соединены со входами первых элементов Н-НЕ (( + )-и группы, управляющий регистр, шину записи и шину считывания, в него введены п групп последовательно соединенных второго, третьего и четвертого элементов Й-НЕ один вход второго элемента И-НЕ каждой группы соединен с шиной записи и первым входом управляю. щего регистра, выходы которого подключе ны к другим входам вторых элементов . Второй кход управляющего регистра ., соединен с шиной считывания и входом третьего элемента И-НЕ последней гру№ пы. В каждой группе выход второго элеме та И-НЁ соединен с другим кходсм чеч вертого элемента И-НЕ. Выход третье го i элемента И-НЕ {-и группы соединен с другими входами i-ro информационного р&гистра, а выход четвертого элемента И-НЕ « группы соединен с входами первых элементов И-НЕ -М группы, Каждая пара первых элементов в каждо группе включена по триггерной схеме. На чертеже изображена функциональная схема устройства для случая и 4, Устройство содержит информационные шины 1-6, щину записи 7, шину считывания 8, первые элементы И-НЕ 9-14 первой грутюы для первого информацисданого регистра 15, первьте элементы 14-НЕ 16- 21 второй группы для второго инфqpмaционного регистра 22, первые элементы 23-28 третьей группы для третьего информационного регистра 29, первые элеме ты И-НЕ 30-35 четвертой группы для четвертого информационного регистра 36, вторые элементь; И-НЕ 37-4 О, третьи элементы И-НЕ 41-44, четвертые элемен ты 45-48 и управляющий регистр 49. Регистр 15 выполнен на триггерах 50-52, регистр 22 - на триггерах 53-55

регистр 29 - на триггерах 56-58, регистр 36 - на триггерах 59-61, а упра&лякхций регистр 49 - на триггерах .

Предлагаемое устройство работает сл&дующим образом.

В исходнс 4 состоянии триггеры 62-65 регистра 49 находятся в нулевсчи состояйии, триггеры регистров 15, 22, 29 и 36 могут находиться влюбом состоянии. Поступающий на шину 7 импульс записи инфсфмацин опрашивает элементы И-НЕ 37-4О. Так как триггеры 02-65 регистра 49 находятся в нулевом состояпереписывается во вспомсгательный триг гер, образованный первьши элементами №-НЁ, например, элементами И-НЕ 23-28 соседнего регистра- 29. По окончании импульса считыва1Ж& ;Внформация также последоватеяьно начиная со старшего разряда, переписывается из вспомогательных триггеров, образованных элементами И-НЕ 9-14, 16-21, 23-28 и 30-35 в информационные регистры 15, 22, 29, 36.

Однофеменно происходит сдвиг информации вправо в регистре 49, при этом триггер 62 устанавливается в нулевое со5НИИ, ТО на выходах элементов И-НЕ 3740 будет сигнал, равный логическому нулю, а на выходах элементов И-НЕ 41-48сигнал, равный .логической единице. Следовательно,элементь И-НЕ 9-14, 16-21, 23-28 и ЗО-35 открыты, и первое двоичное слово с информационных шин 1-6 записывается сначала в регистр 15, затем в регистр 22 и т.д. Таким образом, одним импульсом записи информация сразу же записывается в последний информационный регистр. По заднему фронту импульса записи происходит сдвиг информации влево в регистре 49. При этом триггер 65 регистра 49 установится в единичное состояние сигналом, равным логическому нулю, закроет элемент И-НЕ 40 и на его выходе появляется сигнал, равный логической единице. Поскольку импульс считывания на шине 8 отсутствует, то на эыходе элемента И-НЕ 44 сигнал также равен логической единице, а на выходе элемента И-НЕ 48 будет сигнал, равный логическому нулю, который закрывает элементы И-НЕ ЗО-35. Поэтому с приводом второго импульса записи второе двоичное слово запишется в регистр 29. По заднему фронту импульса записи опять происходит сдвиг регистра 49 влево, и его триггер 64 устанавливается в единичное состояние. Запись информации в остальные регис-рры происходит аналогично. Наличие сигнала, равного логической единице, на единичном выходе триггера 62 регистра 49 свидетельствует о том, что во все регистры 15, 22, 29 и 36 занесена информация и дальнейшее занесение ее невозможно... При считывании информации из запомийающего устройства на шину 8 подается импульс считывания, и инфqpмaция последовательно, начиная со старшего разряда. стояние, и регистр 15 готов к принятию очередаой информации. С приходом следующего импульса считывания снова происходит сдвиг информации из регистра в регистр, и триггер 63 регистра 49 устанавливается в нулевое состояние, что свидетельствует о готсвности регистра 22 к принятию очередной информации. С приходом следующих импульсов СЧ№« тывания информация выводится из устройства аналогично. Наличие сигнала, равного логическому нулю, на единичном выходе триггера 65 регистра 49 свидетельствует о том, что информация в БЗУ и считывание не требуется. Таким образом, повышенное быстродействие, предложенного устройства обусловлено тем, что запись и считывание информации происходят за один такт, причем не требуется дополнительных тактирующих им пульсов для упорядочения информации в устройстве после сигналов записи или считывания, что позволяет использовать уст ройство в быстродействующей аппаратуре, работающей в реальном масштабе времени. Формула изобретения Буферное запоминающее устройство, содержащее п информационных регистров и п групп первых элементов И-НЕ, причем одни из входов i-ro информационного регистра соединены с выходами первых элементов И-НЕ i-u группы ( п , где rt 1, 2, 3, ...., i ), одни из входов которых соединены с выходами (-i )-fo информационного регистра, выходы - ро информационного регистра соединены со входами первых элементов И-НЕ (i + 1)-й группы, управляющий регистр, шину записи и шииу считывания, отличающееся тем , что, с целью повышения быст родействия устройства за счет записи и считывания информации в один такт, в н&го введены п групп последовательно соединенных второго,третье го и четвертого элементов И-НЕ, причем один из нходоа второго элемента И-НЕ каждой группы соединен с шиной записи и первым входом управляющего регистра, выходы которого подключены к рругки входам вторых элементов И-НЕ, второй вход управляющего регистра соединен с щипой считывания и входом третьего элемента И-НЕ последней группы, в каждой группе выход второго элемента И-НЕ соединен с другим входом четвертого элемента И-НЕ, выход третьего элемента И-НЕ i-й группы соединен с другими входами i-re информационного регистра, а выход четвёртого элемента И-НЕ и группы соединен с другими входами nepBtix элементов И-НЁ i-w группьт, причем каждая пара первых элементов И-НЕ в каждой группе включена по триггерной схеме.. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР NO 407396, кл. С 19/60, 28.08.72. 2.Авторское свидетельство СССР по заявке № 2323403, кл. Q 11 С 19/00, 13.02.76 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Буферное запоминающее устройство | 1988 |

|

SU1583938A1 |

| Буферное запоминающее устройство | 1978 |

|

SU750568A1 |

| Буферное запоминающее устройство | 1978 |

|

SU942132A1 |

| Запоминающее устройство с обнаружением и исправлением ошибок | 1980 |

|

SU959167A1 |

| МНОГОКАНАЛЬНАЯ СИСТЕМА ДЛЯ РЕГИСТРАЦИИ ФИЗИЧЕСКИХ ВЕЛИЧИН | 1991 |

|

RU2037190C1 |

| Устройство для сопряжения электронных вычислительных машин | 1984 |

|

SU1257653A2 |

| Устройство для сопряжения процессора с памятью | 1982 |

|

SU1059560A1 |

| Многоканальное устройство для ввода аналоговых данных и буферная память | 1984 |

|

SU1238054A1 |

| Устройство для ввода информации | 1987 |

|

SU1432544A1 |

| Цифровой анализатор спектра | 1987 |

|

SU1413545A1 |

Авторы

Даты

1980-06-05—Публикация

1977-10-03—Подача