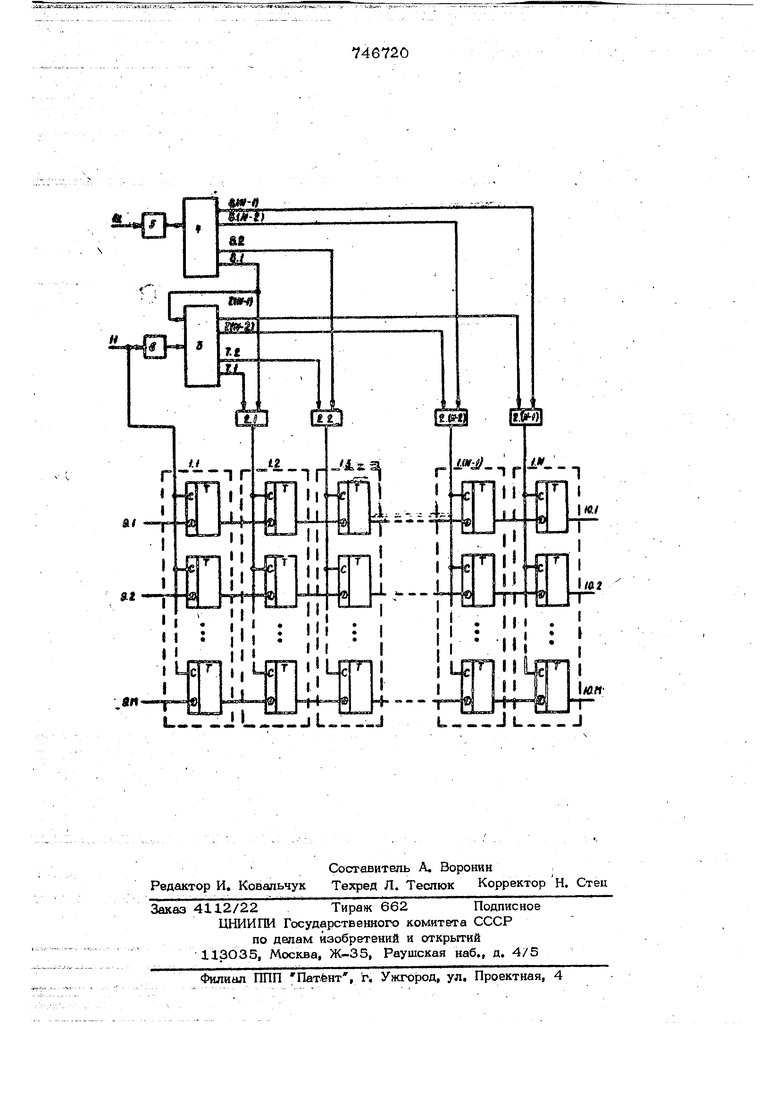

Изобретение откосится к вычислительной технике и может быть использовано при построении устройств хранения дис.кретной инфорКгации. Известно буферное запоминающее устройство, которое содержит регистры хранения чисел, одноименные разряды которы соединены последовательно, и схему управления Д Устройство характеризуется низким быстродействием и имеет низкую надежность функционирования, т.к. критично к длительности поступления входной информации. Наиболее близким из известных по т&хнической сущности является буферное запоминающее устройство, которое содержит регистры хранения чисел, одноименные разряды которых соединены через элементы И последовательно, и схему управления Последняя представляет собой управляющий двухтактный регистр сдвига, содержащий в каждом разряде основной и вспомогательный триггеры, соединенные через элементы И. Нулевой выход каждого основного триггера управляющего регистра сдвига , кроме первого, подключен к элементу И предыдущего разряда этого регистра. Выход элемента И каждого разряда управляющего регистру сдвига соединен с нулевым входом вспомогательного триг гера того же разряда, с единичным входом вспомогательного триггера предыдущего раз)ряда и со в.ходом соответствующих элвгментов И регистров хранения чисел 2 . Изобретение характеризуется низким быстродействием, которое определяется частотой поступления тактовых импульсов. Эта частота ограничена предельной частогтой переключения логических элементов. Целью изобретения является повышение быстродействия устройства. Для достижения этой цели в буферном запоминающем устройстве, содержащем регистры хранения чисел, регистр сдвига, шины записи и считывания, введены распределитель импульсов, элементы задерж- ки и элементы ИЛИ, выходы которых сое,3 ./74 динвны со входами записи всек регистров храаенйя чисел, кроме первого, одни из входов элементов ИЛИ подключены к. выходам регистра сдвига, а другие входы - к выходам распределителя импульсов, вход которого через первьй элемент задержки соединен с шиной считывания,, один из входов рёгис |)а сдвига через второй элемент зад ер шеи соединен с шиной записи и вхо Дом записи первого регистра хранения чисел, другой вход регистра сдвига соединен с другим входом первого элемента ИЛИ, На чертеже представлена функциональная схема устройства. Сно содержит регистры 1.1-1. N хранения чисел, элемен- ты 2.1-1.(Н-1) ИЛИ, регистр 3 сдвига, распределитель И импульсов, элементы 5 и 6 задержки, выходы 7.1-7(14-1) регистра 3 сдвига, выходы 8.1-8.(N-1) распределителя 4 импульсов, информационные входы .М устройства, выходы 10.1-1О.М устройства, шина 11 записи и шина 12 считывания. . Регистры 1.1-1.4 предназначены для Хранения информации и вьшолнены на триггерах) -типа. Элементы 2.1-2.() ИЛИ п{)едназначень1 для управления перезаписью информации Из младших регистров в старшие. Регистр 3 сдвига выполнен рёЬерсйвным и предназначен для определения числа незанятых регистров хранения чисел, а распредеятитепь импульсов 4-ддя организации сдвига информации после ее считывания. Устройство работает следующим образом. В исходном состоянии в рёверсййнЬм регистре 3 сдвига установлен код 11... 1 (единицы во асах разрядах). Для записи информации в устройство на шину 11 записи поступает импульс, по которому первое Mr-разрядное слово записывается в регистр 1.1. На входы записи регистров 1.2-1. Н поступают единицы 6 вьшэдов реверсивного регистра 3 сдвига через элемеш-ы 2..(н-1) ИЛИ. По этому информация с выходов регистра 1.1 запишется в регистр 1.2., оттуда - в регистр , 1.3Й так , через время, равное суммарному времени срабатывания вс регистров l.i-l.N , входная информация появится на выходах 1О.1-10.М устройства.; Си.гнал с шины 11 записи поступает также на один из тактовых входов регист ра 3 сдййга через элемент 5 задержки, сдвигая влево содергйимое регистра 3. В регистре 3 будет код 11. ..10. (ноль в 0.4 последнем разряде, т.е. на выходе 7.(N-f). Таким образом с шины записи 11 регистра 1. N снимается 1. При поступлении следующего слова оно записьюается по сигналу, поступающему по шине 11, в регистр 1.1 (поскольку регистры выполчены на триггерах Ъ -типа, сброс регистров перед записью новой .информации не требуется. Старая информация разрушается в момент записи новой). Из регистра 1.1 это слово запишется в ре гистры 1.2-1. (Н-1), т.к. на входах записи этих регистров находятся 1, Со входа записи регистра LN снята. Поэтому в регистр 1.N новое слово не записывается, а старое - сохраняется. Сигнал записи через элемент 5 задержки сдвигает содержимое регистра 3 влево. В регистре устанавливается код 11...1ОО (нули в последшЕХ двух разрядах - т.е. на выходах 7.()-7.(П-1). Таким образом, по мере заполнения устройства информацией количество нулей справа в разрядах регистра 3 увеличийается. При этом последовательно снимаются единицы со входов записи регистров хранения чисел (в направлении от старших регистров к младшим).. Общее количество слов, которое может Хранить устройство, равно Ы Информация с выходов Ю, 1-10,М поступает к абоненту, где происходит ее считьюаниё. При этом сигнал, которым абонент считывает информацию, подается на шину 12 считывания устройства. Сигнал считьшания через элемент 6 задержки поступает на нхоД распределителя 4 и запускает, его. Распределитель 4 формирует на своих выходах, начиная с выхода 8.(N-1), последовательность импульсов. Импульс с выхода В Л Nf -1) поступает через | элемент 2(N-1) ИЛИ на вход-записи регистра 1. М . При этом в регистр 1.Н переписывается информация из регистра l.(N-l). Затем аналогично импульс с вььхода 8.(N-2) распределителя 4 переписывает информацию в регистр 1.(Ы-1) из прёдьщущего, регистра и так далее. Таким образом, происходит сдвиг информации в сторону старцих регистров и к выходам 10.1-10.М подключается следующее слово. Сигнал с выхода 8,1 (последний выход распределителя 4) сдвигает вправо содержимое регистра сдвига 3. Количество нулей .справа в разрядах регистра 3 уменьшается на единицу.

Рассмотренные процессы записи и двига информации могут происходить в юбой последовательности. При этом количество нулей в разрядах регистра сдвига 3 равно разности числа импульсов за- j писи и считывания, т.е. равно количеству слов, хранимых устройством в данный момент времени.

Элемент 5 задержки разрешает переключение регистра 3 сдвига только после о того, как входное слово достигает старшего свободного регистров.

Элемент 6 задержки (величина его задержки не меньше, чем длительность импульса считывания) разрешает запуск рас- 5 пределителя 4 импульсов по окончании считывания информации абонентом. При заполнении устройства информацией скорость продвижения информации от младших регистров к старшим определяется 2о только временем срабатьшания этих ре1истров и не зависит от тактовьгх импульсов, что имеет место в прототипе. Сравнивая предложенное устройство с известным по быстродействию, следует отметить, 25 что после поступления .1-го входного слова оно появляется на выходе:

а)в предложенном устройстве - через

время Т NtcpCTB

б)в прототипе - через времязо T(N-l)tn,

где м -число регистров хранения чисел, ераГ срабатывания регистров, tf -период следования тактовых импульсов.35

-Ьр, определяется частотой поступления тактовьгх импульсов, которая по условиям устойчивой работы элементов не должна превышать предельной частоты переключения этИх элементов. В то же время для 40

всех серийно выпускаемых логических элементов предельная частота .ограничена таким образом, чтобы t в несколько раз превышало -t сраб.

Быстродействие предложенного устройства в несколько раз превьш1ает быстродействие известного.

Формула изобретения

Буферное запоминающее устройство, содержащее последовательно соединенные регистры хранения чисел, регистр сдвига и шины записи и считывания, отличающееся тем, что, с целью повышения быстродействия устройства, в него введены распределитель импульсов, элементы задержки и элементы ИЛИ, выходы которых соединены со входами записи всех регистров хранения чисел, кроме первого, одни из входов элементов ИЛИ подключены к вьгходам регистра сдвига, другие входы ихк выходам распределителя импульсов, вход которого через первый элемент задержки соединен с шиной считьтания,один из входов регистра сдвига через второй элемент задержки соединен с шиной записи и аходом записи первого регистра хранения чисел, другой вход регистра сдвига соединен с другим аходом первого элемёт-а ИЛИ.

Источники информации, принятые во внимание при экспертизе

1.Авторское свидетельство СССР № 375681, кл. Q 11 С 19/ОО, 06.08.70.

2.Авторское свидетельство СССР № 407396, кл. G 11 С 19/00, 28.08.72 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Буферное запоминающее устройство | 1982 |

|

SU1084896A1 |

| Устройство управления для доменной памяти | 1984 |

|

SU1265856A1 |

| Запоминающее устройство | 1985 |

|

SU1280454A1 |

| Буферное запоминающее устройство | 1977 |

|

SU739645A1 |

| Устройство для сопряжения с микроЭВМ | 1986 |

|

SU1709322A1 |

| Устройство для умножения @ -разрядных двоичных чисел | 1990 |

|

SU1783519A1 |

| Программируемая линия задержки | 1990 |

|

SU1723656A1 |

| Логическое запоминающее устройство | 1983 |

|

SU1124384A1 |

| Запоминающее устройство | 1979 |

|

SU842967A1 |

| Распределитель импульсов для многотактового запоминающего устройства на регистрах сдвига | 1978 |

|

SU752488A1 |

Авторы

Даты

1980-07-05—Публикация

1978-04-06—Подача