Изобретение относится к автоматике и может быть использовано при построении надежных устройств автоматического управления, осуществляющих логическую обработку информации.

В известных схемах мажоритарных элементов входные ячейки могут быть выполнены, например, на многоэмиттерных транзисторах. Сигналы, поданные на эмиттеры транзисторов входных ячеек, снимаются с их коллекторов на базы транзисторов цепей, осуществляющих логические операции ИЛИ и далее на выходной усилитель.

Однако известные мажоритарные элементы имеют недостаточную надежность.

Ввиду высокой концентрации примесей в эмиттерном переходе, напряжение пробоя перехода эмиттер - база в лучщем случае не превышает 7-8 в. При увеличении температуры это напряжение еще более снижается.

Таким образом, при подаче на вход многоэмиттерных транзисторов высокого уровня напряжения, соответствующего логической единице, которое в общем случае колеблется около 3 в, возникают условия, при которых эмиттерный переход может быть пробит. Такие условия возникают, например, при сочетании логических уровней на входных ячейках мажоритарного элемента, когда на одну входную клемму подается логический «О, а

на другую - соседнюю - логическая «1, при этом из-за пробоя эмиттерного перехода информация о поступивщей логической «1 теряется.

Целью изобретения является повыщение надежности мажоритарного элемента.

Для этого он содержит по числу входов входные ячейки на двух транзисторах, коллекторы которых объединены и подключены к соответствующему входу ячейки ИЛИ, а базы через резисторы соединены с источником питания, а эмиттеры соединены с эмиттерами транзисторов соседних по кольцу ячеек.

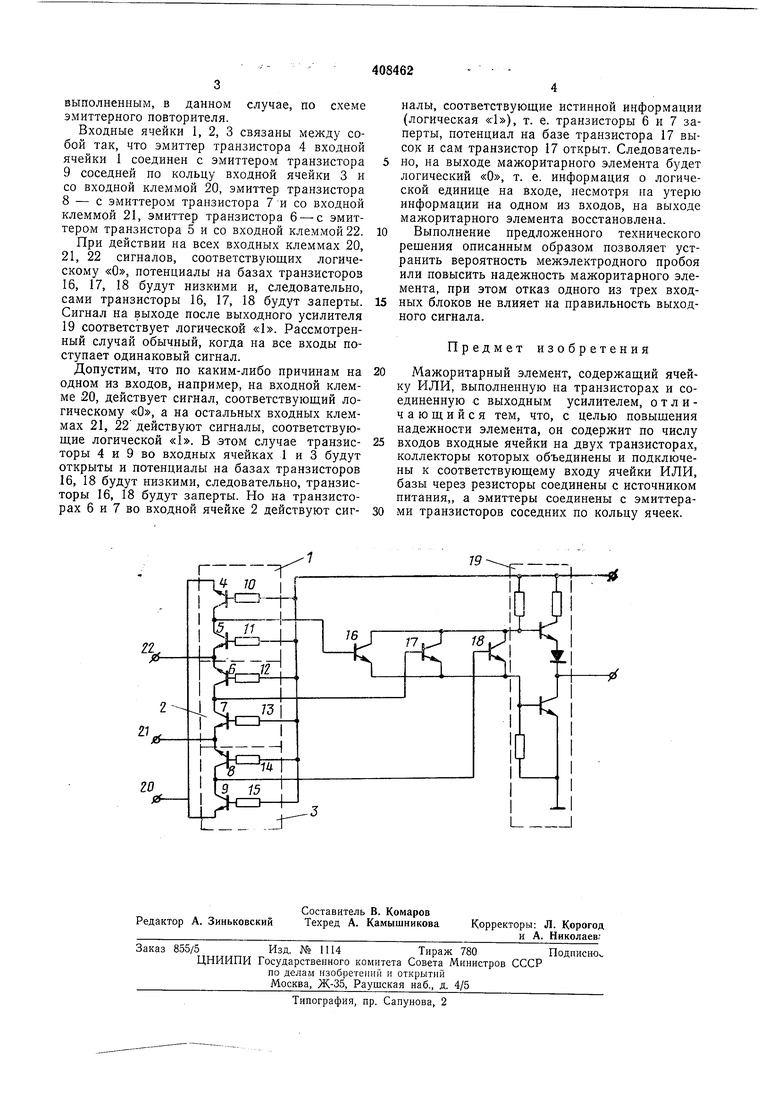

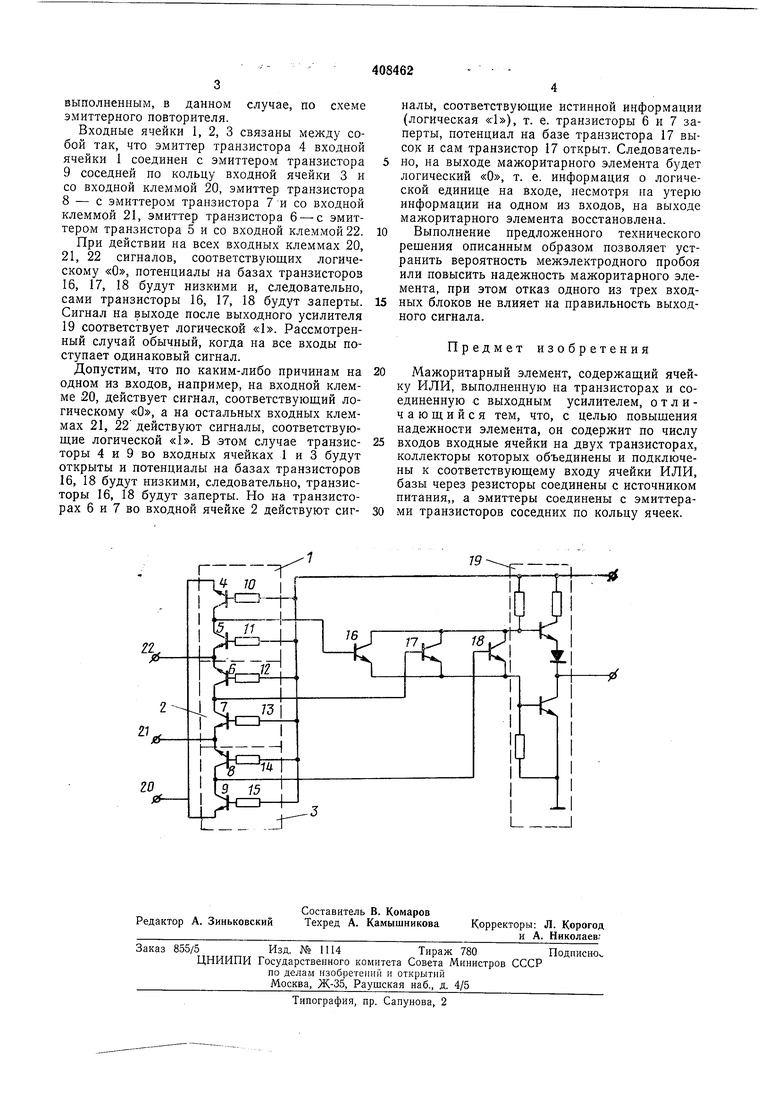

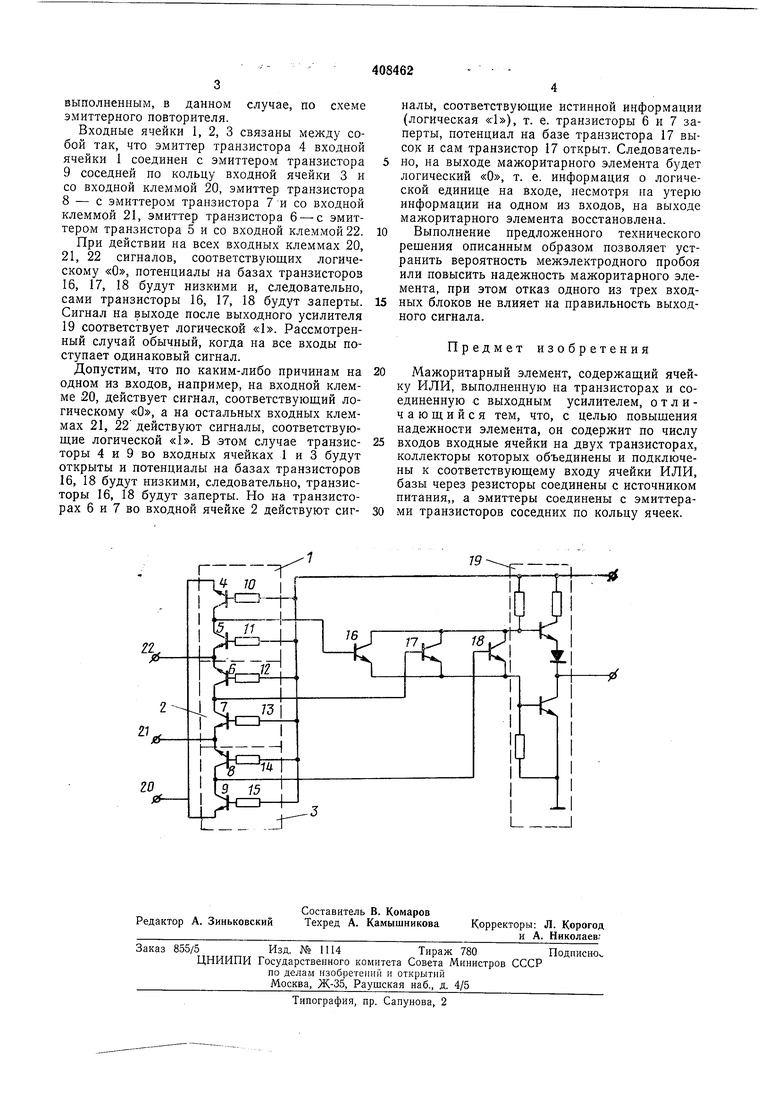

Изобретение пояснено чертежом.

На чертеже приведена принципиальная электрическая схема элемента.

Мажоритарный элемент содернсит входные ячейки 1, 2, 3, каждая из которых выполнена на двух транзисторах 4, 5, 6, 7, 8, 9. Все транзисторы 4, 5, ,6, 7, 8, 9 через резисторы 10, 11, 12, 13, 14, 16 подключены к одному из полюсов источника питания. Коллекторы транзисторов 4, 5, 6, 7, В, 9 соединены между собой и с базой одного из транзисторов 16, 17, 18, осуществляющих логическую операцию ИЛИ и включенных между собой параллельно. Кроме того, эти транзисторы 16, 17, 18 электрически связаны с выходным усилителем 19,

выполненным, в данном случае, по схеме эмиттерного повторителя.

Входные ячейки 1, 2, 3 связаны между собой так, что эмиттер транзистора 4 входной ячейки I соединен с эмиттером транзистора 9 соседней по кольцу входной ячейки 3 и со входной клеммой 20, эмиттер транзистора 8 - с эмиттером транзистора 7 и со входной клеммой 21, эмиттер транзистора 6--с эмиттером транзистора 5 и со входной клеммой 22.

При действии на всех входных клеммах 20, 21, 22 сигналов, соответствующих логическому «О, потенциалы на базах транзисторов 16, 17, 18 будут низкими и, следовательно, сами транзисторы 16, 17, 18 будут заперты. Сигнал на выходе после выходного усилителя 19 соответствует логической «1. Рассмотренный случай обычный, когда на все входы поступает одинаковый сигнал.

Допустим, что по каким-либо причинам на одном из входов, например, на входной клемме 20, действует сигнал, соответствующий логическому «О, а на остальных входных клеммах 21, 22 действуют сигналы, соответствующие логической «1. В этом случае транзисторы 4 и 9 во входных ячейках 1 и 3 будут открыты и потенциалы на базах транзисторов 16, 18 будут низкими, следовательно, транзисторы 16, 18 будут заперты. Но на транзисторах 6 и 7 во входной ячейке 2 действуют сигналы, соответствующие истинной информации (логическая «), т. е. транзисторы 6 и 7 заперты, потенциал на базе транзистора 17 высок и сам транзистор 17 открыт. Следовательно, на выходе мажоритарного элемента будет логический «О, т. е. информация о логической единице на входе, несмотря па утерю информации на одном из входов, на выходе мажоритарного элемента восстановлена.

Выполнение предложенного технического рещения описанным образом позволяет устранить вероятность межэлектродного пробоя или повысить надежность мажоритарного элемента, при этом отказ одного из трех входных блоков не влияет на правильность выходного сигнала.

Предмет изобретения

Мажоритарный элемент, содержащий ячейку ИЛИ, выполненную на транзисторах и соединенную с выходным усилителем, отличающийся тем, что, с целью повыщения надежности элемента, он содержит по числу

входов входные ячейки на двух транзисторах, коллекторы которых объединены и подключены к соответствующему входу ячейки ИЛИ, базы через резисторы соединены с источником питания,, а эмиттеры соединены с эмиттерами транзисторов соседних по кольцу ячеек.

| название | год | авторы | номер документа |

|---|---|---|---|

| Многопороговый логический элемент | 1982 |

|

SU1042183A1 |

| Многофункциональный пороговый модуль | 1973 |

|

SU493030A1 |

| Пороговый логический элемент | 1975 |

|

SU600711A1 |

| Быстродействующий помехоустойчивыйлОгичЕСКий элЕМЕНТ и-или/ и-или-HE | 1978 |

|

SU849488A1 |

| ЛОГИЧЕСКИЙ ЭЛЕМЕНТ ТРОИЧНОЙ ТРАНЗИСТОРНО-ТРАНЗИСТОРНОЙ ЛОГИКИ | 2022 |

|

RU2782474C1 |

| Устройство для сравнения напряжений | 1976 |

|

SU657406A1 |

| ЛОГИЧЕСКИЙ ЭЛЕМЕНТ ЦИКЛИЧЕСКОЙ ИНВЕРСИИ ТРОИЧНОЙ ТРАНЗИСТОРНО-ТРАНЗИСТОРНОЙ ЛОГИКИ (ВАРИАНТЫ) | 2024 |

|

RU2835664C1 |

| ТТЛ-элемент | 1985 |

|

SU1277382A1 |

| Многопороговый логический элемент | 1983 |

|

SU1132366A2 |

| ТРАНЗИСТОРНО-ТРАНЗИСТОРНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ | 1989 |

|

SU1679943A1 |

Даты

1973-01-01—Публикация