1

Данное изобретение относится к облас.И вычислительной техники.

Известны обратимые многоразрядные сумматоры с умножением на постоянный коэффициент, содержащие п одноразрядных обратимых сумматоров на операционных усилителях с последовательно включенными основными и вспомогательными двухполюсниками в цепи обратной связи.

С целью повышение точности обратимый многоразрядный сумматор содержит п резисторов и п функциональных преобразователей, входы которых соединены с входными клеммами устройства, а также с основными и вспомогательными двухполюсниками соответствующих одноразрядных обратимых сумматоров, а выходы нодключены через резисторы ко входам соответствующих операционных усилителей.

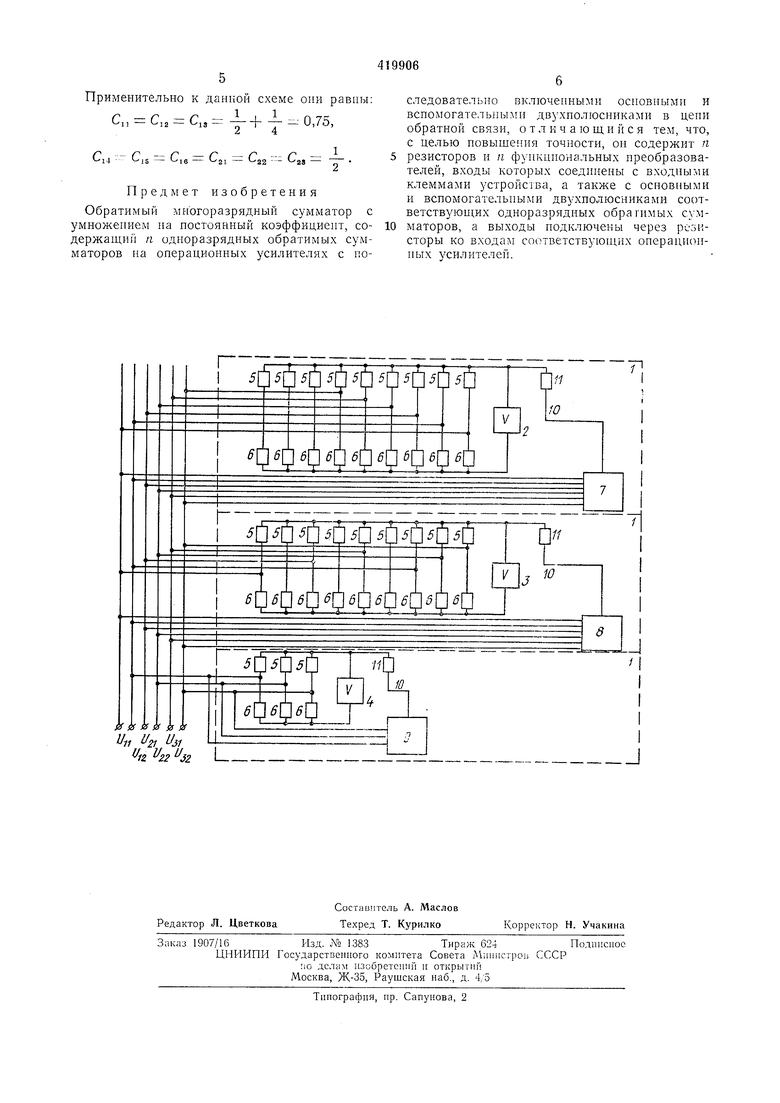

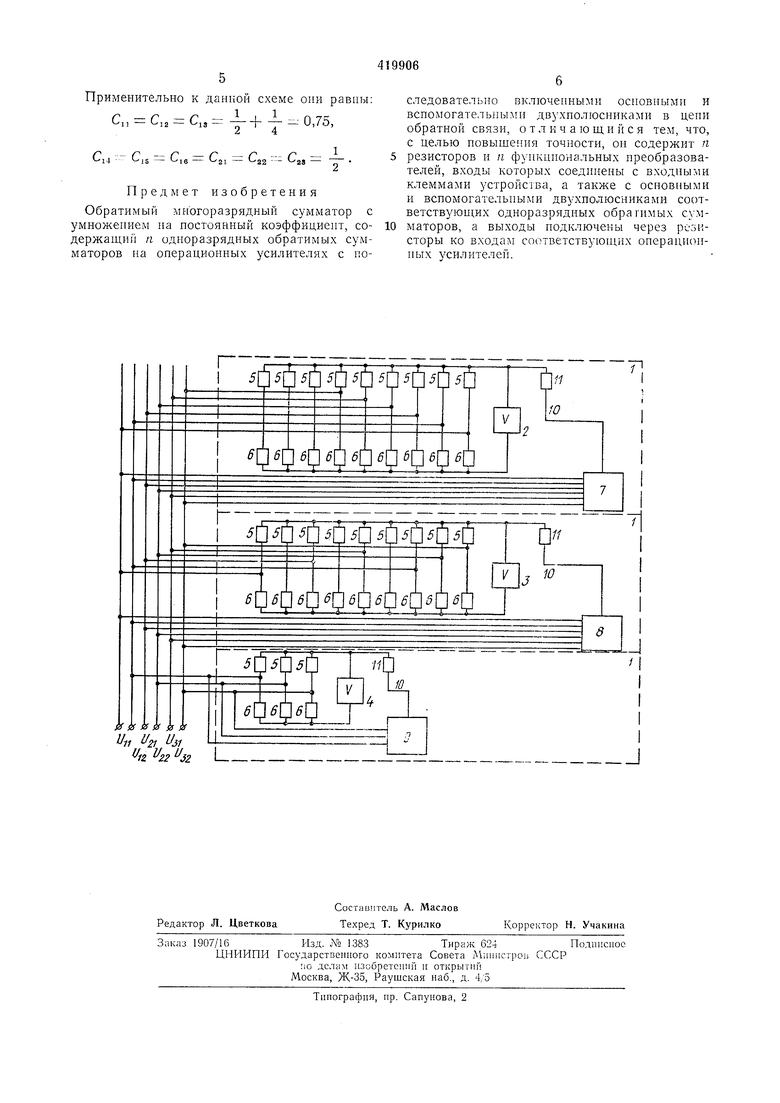

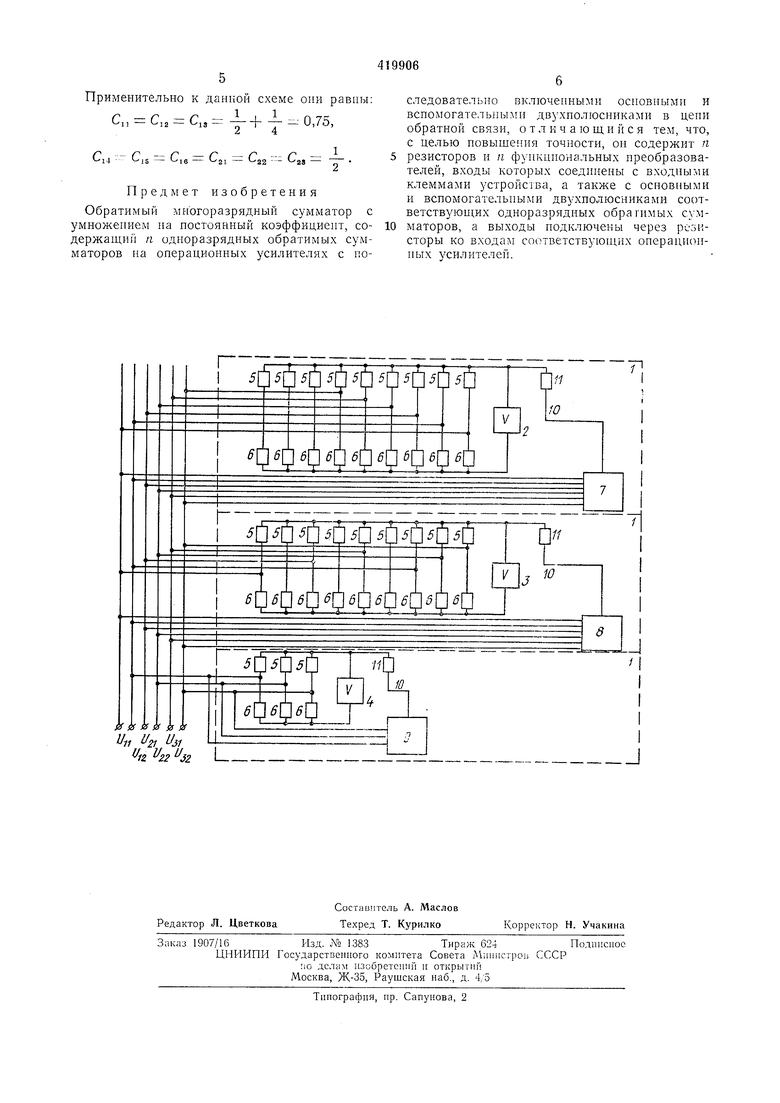

На чертеже приведен вариант схемы предлагаемого обратимого многоразрядного cy iматора.

Сумматор работает следуюним образом.

Входные (п-I) независимые переме Н1ые

1 -- Ч im

- ij imi Xn-l - n-l,l -Лп-,} . . -fCn-l, mi

ашине в виде векторов на.и,

. и

1 .и, и.

im

ч

Un-l Un-l, I ... л-1, у ... Un-l, т .

где п - общее количество входов и выходов обратимого многоразрядного сумматора, т - количество разрядов независимых машинных переменных, которые подаются на соответствующие входы одноразрядных обратимых сумматоров 1 по модулю системы счисления на п входов. Выработка единиц перепоса из младшего

одноразрядного обратимого сумматора 1 но модулю системы счисления на п входов в старши одноразрядный обратимый сумматор 1 по модулЕО системы счисления на п входов осуществляется непосредственно в старшем

одноразрядно.м обратимом сумматоре 1 по модулю снстемы счисления на « входов нутем подключения входных и выходных машинных неременных младшего разряда на вход одноразрядного обратимого сумматора 1 старшего разряда с одновременным их умножением

на коэффициент, равный -, где q - основание системы счисления.

В связи с тем, что одноразрядный обратимый сумматор 1 но модулю системы счисления выдает на выходе инверсное значение суммы по модулю системы счисления входных нанряжений, то общая сумма входных и выходных напряжений будет равна удвоенному значению переноса в старший разряд. Так, если мы имеем одноразрядный сумматор 1 но модулю «два на 6 входов и на любые 5 входов из этих шести подаются напряжения, моделирующие едннины в двоичной системе счисления, то на шестом свободном входе (который будет в даином случае выходом) ноявится нанряжение, равное сумме няти единиц но модулю «два, но нротивоположное но знаку. Если единица будет моделироваться напряжением -f- 10 в, то при ноступленин пяти единнц на выходе одноразрядного обратимого сумматора по модулю «два появится напряжение равное -10 в. Общая сумма напряжений на входах и выходе (в данном примере равная (+10 в) + (+10 в) + ( + 10 в) + (10 в) + -f (+10 в) + (-10)40 в будет соответствовать удвоенному количеству единиц переноса в старший разряд. Поэтому, если умножить все напряжения, моделируюшие младшие раз„1ряды, на коэффициент, равнын -, где q - ос

нование системы счисления, и нросуммировать их в обратимом одноразрядном сумматоре 1 старшего разряда, получим выработку единиц переноса непосредственно в сумматоре 1 старшего разряда. При этом следует учесть, что перенос из младшего разряда необходимо заводить не только в следуюн1ий старший разряд, но и в последующие старшие разряды, умножая при этом его на коэффициент, обратно пропорциональный весу более старшего разряда. Так, если мы будем суммировать с ниверсией по модулю системы счислепия трехразрядпые числа:

bi -- . где i - количество суммируемых чисел,

feji - первый, самый старший разряд,

bi-i- второй разряд,

biz - третий, младший разряд, то перепое от суммы младших разрядов б;, в разряд 3 будет равен:

п

2ь

о 1 1 J3-2 :

где q - основание системы счислепия,

а перенос из суммы младших разрядов в

разряд &л будет равен:

о1 1

Ьз-1 - -- , q

где 5з-2 -количество единиц переноса из третьего разряда во второй,

- количество единиц переноса из третьего разряда в первый.

На чертеже изображена в качестве примера схема для моделирования уравнения внда:

a Xi- -azXz+azXz Q,

где аь 02, аз - коэффрнлкенты, представленные двухразрядным двоичпым числом ai .

Я2Я21й 22,

2з (а;з1йз2;

Х, Хг, Х- - независимые машинные переменные, нредставленные двухразрядным числом

Xi XiiX{i, Xl XziXiz,

АЗ Аз1Лз2.

8машине этн переменные представлены в знаковом двоичном коде в виде вектора напряжений:Ui UiiUi2,

и2 Оз Ьз1сУз2Схема состоит из трех одноразрядных обрати.мых сумматоров 1 по модулю «два, собранных на усилителях 2, 3, 4 с основными и вспомогательными резисторнымн двухполюсниками 5 и 6 в обратной связи, моделирующих зпаченне коэффициента uij (, 2, 3; , 2 и коэффициент Сцг для выработки единиц нереноса из младшего разряда непосредственно в старший разряд, где: Кгпит 1п-п, т - количество разрядов независимых машинных неременных, п - количество независимых машинных неременных.

Коэффициенты а,-; (t-1, 2, 3; , 2) могут принимать только значения, равные либо «1, «О. Независимые машинные переменные L/a (, 2, 3; , 2) могут принимать дискретные значения -UQ Ь; О Ь; (, Ь, что соответствует в знаковом коде -1; 0; 1.

Работа каладого обратимого одноразрядного сумматора 1 по модулю «2 заключается в следующем: входы обратимого операциоиного усилителя 2, 3 или 4 подключены к функциональному преобразователю 7, 8 или 9, реализующему ступенчатую функцию. Выходы функциональных преобразователей 7, 8 и 9 подключены к .пополнительным необратимым входам 10 обратимого операционного усилнтеля через резисторы 11. При поступлении на вход функциональных преобразователей 7, 8,

9компонент векторов независимых мащинных переменных он их суммирует и вырабатывает ближайщее но абсолютному значению инверсное нанряжение, кратное основанию системы счисления. Таким образом, на выходе выделяется сумма но модулю системы счисления. Коэффициенты Си-Cia равны сумме коэффициентов для осуществления переноса из

третьего (младшего) и второго разрядов.

Коэффициенты Ci;-CiG равны коэффициентам для нереноса из второго разряда в третий, коэффициенты Czi-Czs равны коэффициентам для осуществления нереноса из

третьего разряда во второй.

Применительно к данной схеме они равны: C,j GU - j т -- и,75,

-- 18 - 21 -- 22 -- 28 --

Предмет изобретения

Обратимый многоразрядный сумматор с умножением на ностоянный коэффициент, содержащий п одноразрядных обратимых сумматоров на онерационных усилителях с последовательно включенными осповнымн и Бспомогательнымн двухнолюсниками в цени обратной связи, отличающийся тем, что, с целью новыщения точности, он содержит п резисторов и п функцнональных нреобразователей, входы которых соединены с входными клеммами устройства, а также с основными и вспомогательными двухиолюсникамн соответствуюнщх одноразрядных обратимых сумматоров, а выходы нодключены через резисторы ко входам соответствующих онерациониых усилителей.

| название | год | авторы | номер документа |

|---|---|---|---|

| Комбинационный сумматор | 1975 |

|

SU570896A1 |

| Устройство для извлечения квадратного корня с перестраиваемым основанием системы счисления | 1985 |

|

SU1363204A1 |

| ОБРАТИМЫЙ ОДНОРАЗРЯДНЫЙ СУММАТОР | 1971 |

|

SU430380A1 |

| Универсальное суммирующее устройство | 1990 |

|

SU1786484A1 |

| Устройство для суммирования нескольких Р-ичных чисел | 1983 |

|

SU1188730A1 |

| Накапливающий сумматор | 1976 |

|

SU577528A1 |

| Последовательный сумматор | 1977 |

|

SU696452A1 |

| Устройство для формирования остатков по модулю | 1986 |

|

SU1449986A1 |

| Комбинационный сумматор | 1985 |

|

SU1310808A1 |

| Сумматор кодов фибоначчи | 1976 |

|

SU732864A1 |

5

g g gg g g g u gg D

U U 0 u 00000 i 1/„ и, Z6, 1

ю

j

Даты

1974-03-15—Публикация

1971-12-09—Подача