(54) АМАЛОГОВОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналоговое запоминающее устройство | 1979 |

|

SU873279A1 |

| Аналоговое запоминающее устройство | 1979 |

|

SU864342A1 |

| Аналоговое запоминающее устройство | 1981 |

|

SU1015445A1 |

| Аналоговое запоминающее устройство | 1978 |

|

SU771729A1 |

| Дискретно-аналоговая линия задержки | 1982 |

|

SU1115230A1 |

| Аналого-дискретный интегратор | 1981 |

|

SU987632A1 |

| Аналоговое запоминающее устройство | 1980 |

|

SU943853A1 |

| Устройство считывания сигналов с фотоприемной матрицы инфракрасного излучения (варианты) | 2018 |

|

RU2688953C1 |

| Матричный накопитель для постоянного запоминающего устройства | 1988 |

|

SU1778790A1 |

| Аналоговое запоминающее устройство | 1978 |

|

SU832601A1 |

{

Изобретение относится к автоматике и вычислительной технике и может быть использовано в различных аналого-цифровых измерительных системах для исследования параметров быстр.опротекающих процессов.

Известно аналоговое запоминающее устройство, содержащее два накопительных элемента, .блоки записи виодзаряда, ключи, блок управления и согласующий усилитель Г2

Недостатком известного устройства является ограниченная область применения - оно используется только в однокацальной аппаратуре.

. Наиболее близким по технической сущности к изобретению является аналоговое запоминающее устройство, которое содержит ячейки памяти, каждая из которых содержит элемент заряда, элемент считывания и накопительный элемент, например конденсатор, одна из обкладок которых подключена .к щине нулевого потенциала, другая - к элементу заряда и к входу элемента считывания, управляющий генератор, вход которого является вхог домустройства, выходы управляющего генератора подключены к элементам заряда соответствующих ячеек памяти, тактовый генератор, выход которого подключен к входу регистра сдвига, выходы которого подключены к входам соответствующих злементов считыв 10ния, выходной сглаживающий элемент, выход которого является выходом устройства, генератор .фонового тока переключатель тбка, один из входов которого подключен к выходу генерато15ра фонового тока, другие - к выходам тактового генератора и выходной наког.: пительный элемент, например конденсатор, одна из обкладок которого подключена к шине нулевого ла, а другая - к выходу переключателя тока и к входу выходного согласуняце-л го элемента. В многоканальном аналоговом запоминающем устройстве величина

емкости накопительных элементов - коденсаторов определяется в зависимости от величины интеграла тока по времени существования входного моноимпульса j; (t). Так при обработке моноимпульсов с амплитудами порядка I мА, с длительностями около 50 НС, расчетная величина емкости на копителыа 1х элементов - конденсаторо составляет 51 пФ. При дальнейшем уменьшении амплитуд и длительностей входных моноимпульсов эта величина должна быть еще более уменьшена. Однако в известном устройстве подобное уменьшение ограничено, поскольку суммарная паразитная нелинейная емкость коллекторов транзисторовэлементов считывания, подключенных к выходному накопительному конденсатор при большом числе канапов обработки, оказыватеся сравнимой с величиной емкости выходного накопительного элемента-конденсатора. В известном устройстве в результате последовательного опроса накопительных элементов зафиксированная в них информация поступает в выходной накопительный элемент - конденсатор в виде совокупности п зарядов. А считывается с него с помощью выходного согласующего устройства, в виде последовательнсоти из п скачков напряжения, т.е. амплитудного распределения одновременно возникающих моноимпудьсных сигналов. Таким образом, на данном этапе обработки моноимпульсов происходит преобразование зарядов в напряжение. Причем размерным коэффициентом преобразования здесь является величина, складывающаяся из емкости выходного накопительного Элемента-конденсатора и соизмеримой с ней нелинейной суммарной царазитной емкости параллельно подключенных коллекторных переходов транзисторов - эл ементов считывания 2}

Однако нелинейность результируюг щей емкости приводит к снижению точности операции вывода информационных сигналов, и как следствие, к существенному ограничению количества используемых каналов обработки мононмпульсных сигналов.

Цель изобретения - повьш1ение точности аналогового запоминакицего устройства.

Поставленная цель достигается тем что в аналоговое запоминающее .устройство, содержащее накопитель, первые входы ячеек памяти которого соег динены со входами устройства, вторые и третьи входы ячеек памяти накопителя подключены к соответствующим выг ходам генератора управляющих импульсов, регистр сдвига, выходы которого соединены с четвертыми входами ячеек памяти накопителя, выход которого подключен к первому накопителынОму элементу, например к одной из обкладок конденсатора и к первому выходу переключателя тока, генератор тактовых сигналов, выходы которого соединены с первым и вторым входами переключателя тока, вход регистра сдвига подключен к одному из выходов генератора тактовых сигналов, другая обкладка первого конденсатора соединена со вторым выходом переключателя тока и с шиной нулевого потенциала, генератор фонового тока, выход которого подключен к третьему входу переключателя тока, элемент согласования, выход которого соединен с выходом устройства и шину питания, введен второй накопительный элемент, например конденсатор, элемент считывания и преобразователь уровня тактовых сигналов, вход которого соединен с одним из рыходов генератора тактовых сигналов, выход преобразователя уровня тактовых сигналов подключен к первому входу элемен- . та считывания, второй вход Которого подключен к первому выходу переключателя тока, а выход соединен со входом элемента согласования и с одной обкладкой второго конденсатора, другая обкладка которого соединена с шиной питания.

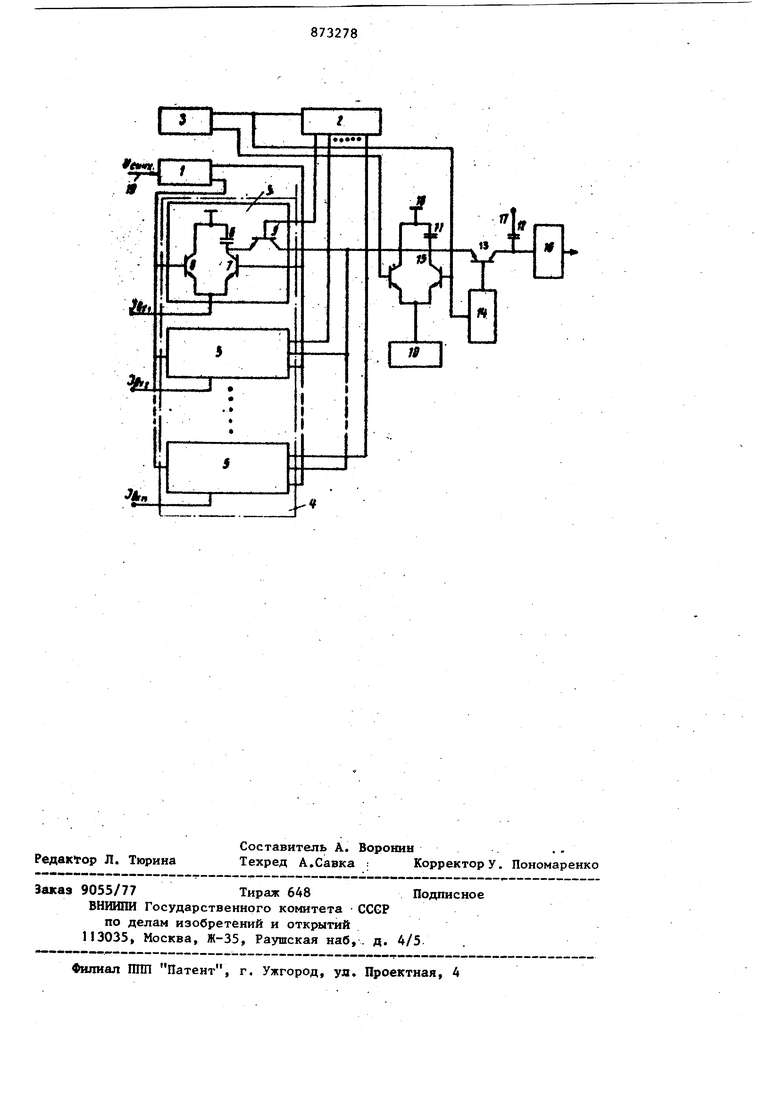

На чертеже представлена функциональная схема предложенного устройства.

Устройство содержит генератор управляющих импульсов I, регистр 2, сдвига, генератор 3 тактовых сигналов, накопитель 4, ячейки памяти 5 накопителя 4, накопительные элементы, напри.мер конденсаторы 6 ячеек памяти 5 (на чертеже показан конденсатор одной ячейки памяти), элементы7 и 8 заряда, элементы считывания 9 (показаны только одной ячейки памяти),генератор 10 фонового тока, накопительные элементы, например конденсаторы 11 и 12, элемент считывания 13, преобразователь 14 уровня тактовых сиг- .

налов, переключатель 15 тока, элемент согласования 16, шина питания 17, шина 18 нулевого потенциала, шина синхронизации 19.

Работа устройства состоит в следующем.

В исходном состоянии транзистор элемента заряда первой ячейки памяти 5 закрыт, а транзистор элемента заряда в открыты. При поступлении на вход генератора I сигнала синхронизации управляющий генератор 1 вырабатывает парафазные сигналы, один из которых закрывает транзистор элемента заряда 8, а другой открывает транзистор элемента заряда 7. С задержкой, равной времени переключения генератора I, на входы ячеек памяти 5 одновременно поступают п анализируемых моноимпульсных

сигналов. Накопительный элементконденсатор 6 ячейки памяти 5 заряжается за время, в течение которого транзистор элемента заряда 7 находится в открытом состоянии, равное или несколько превосходящее лительность входного импульса 3(t). В течение некоторого времени заряд хранится на накопительном элементеконденсаторе 6 и сохраняет свое значение с погрешностью, определяемой токами утечки запертых транзисторов. Транзистор элемента 9 считывания заперт в течение времени накоп-; ления и хранения. Режим считывания

осуществляется последовательной подачей отпирающих импульсов от регистра сдвига 2 на базы транзисторов элементов 9 считывания, причем частота переключения элементов считывания (от канала к каналу) опг ределяется частотой тактового генератора 3. С помощью элементов считывания 9 осуществляется последова-.. тельный перенос накопленных на накопительных элементах-конденсаторах 6. зарядов на конденсатор 1I, и таким образом, производится развертка во времени на накопительном элементеконденсаторе 1I совокупности информа ционных зарядов (с периодом, равным периоду тактового генератора). Далее вся последовательность зарядов переносится с помощью дополнительного элемента считывания 13 в накопительный элемент-конденсатор 12. Управление элементом считывания 13 осуществг: ляется от генератора тактовых сигналов 3 с помощью преобразователя уровня 14, которьгй смещает уровень управляющих импульсов на величину, необходимую для обеспечения активного режима работы транзистора элемента считывания 13. Считывание информации с линеаризирующего накопительного элемента 12 производится с по- мощью элемента согласования 16 в виде последовательности из п скачков

напряжения, т.е. амплитудного распределения п одновременно возникающих моноимпульсных сигналов. Поддержание готовности к работе накопительного элемента 11 и накопительного

элемента 12 осуществляется непрерывным прохождением через них фонового заряда, который подается в накопительный элемент 1I с помощью переключателя тока 12 от генератора 10 фонового тока, а затем переносится элементом считывания 13 в линеаризую(

щий накопительный элемент I5. Суммарная емкость, складывающаяся из емкости накопительного элемента I1

и параллельно подключенных к нему паразитных нелинейных емкостей коллектор1шх переходов транзисторовэлементов считывания 9 имеет нелинейный характер, проявляющийся в эависимости величины емкости от находящегося в ней заряда. Отсюда следует, что напряжение на этой емкости является нелинейной функцией от заряда. Однако элемент считывания 13 считывает с накопительного элемента 11 заряд, а не напряжение и переносит его в элемент 12, в котором теперь уже прог исходит преобразование . .заряда в напряжение. Накопительный элемент 12

отличается от накопительного элемента 11 высокой линейностью, поскольку к нему подключен лишь один коллекторный переход транзистора - элемента считывания 13, величиной емкости которого из-за малости пренебречь по сравнению с емкостью накопительного элемента 12, Введение еще одного переноса зарядов позволяет получить существенный выигрьш1 в точности обработки при большом числе каналов, так как устраняет искажающее влияние нелинейности результирующей емкости накопительного элемента 11 на обрабатываемые сигнсшы и не вносит практически дополнительных поуррь информации при переносе, поскольку при данном исполнении устройства,погрешность при одном, переносе составляет величину менее 1%. , Устранение влияния нелинейности результирующей емкости накопительно го элемента I1 на операцию цреобраз вания ааряда в напряжение позволяет существенно расширить число каналов многоканального аналогового запоминающего устройства. Таким образом, йведение дополнительного элемента считывания и допол|жтвльного накопительного элемент обеспечивает повышение линейности оп рации вывода информационного сигнала и,тем самым, позволяет повысить точность работы всего устройства,что в нечном счете приводит к возможности обрабатывать еще более короткие моноимпульсные сигналы и с меньшими амплитудами, Формула изобретения Аналоговое запоминающее устройство, содержащее накопитель, первые входы ячеек памяти которого сое динены со.входами устройства, вторы 1и третьи входы ячеек памяти накопителя подключены к соответствующим в ходам генератора управляющих импуль сов, регистр сдвига, выходы которог соединены с четвертыми входами ячеек памяти накопителя, выход которого подключен к первому накопительному элементу, например к одной из обкладок конденсатора и к первому выходу переключателя тока, генератор тактовых сигналов, выходы которого соединены.с первым и вторым входами переключателя тока, вход регистра сдвига подключен к одному из выходов генератора тактовых сигналов, другая обкладка первого конденсатора соединена со вторым выходом переключателя тока и с шиной нулевого потенциала, генератор фонового тока, выход которого подключен к третьему входу переключателя тока, элемент согласования, выход которого соединен с выходом устройства и шину питания, отличающееся тем, что, с целью повышения точности устройства, в него введен второй накопительный элемент, например конденсатор, элемент считывания и преобразователь уровня тактовых сигналов, вход которого соединен с одним из выходов генератора тактовых сигналов, выход преобразователя уровня тактовых сигналов подключен к первому входу элемента считывания, второй вход которого подключен к первому выходу переключателя тока, а выход соединен со входом элемента согласования и с одной обкладкой второго конденсатора, другая обкладка которого соединена с шиной питания Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № 562867, кл. G 11 С 27/00, 1977. 2.Авторское свидетельство СССР по заявке № 2699727/18-24, кл. G 11 С 27/00, 1978 (прототип).

Авторы

Даты

1981-10-15—Публикация

1979-12-17—Подача