(54) АНАЛОГОВОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналоговое запоминающее устройство | 1979 |

|

SU873278A1 |

| Аналоговое запоминающее устройство | 1979 |

|

SU873279A1 |

| Аналоговое запоминающее устройство | 1981 |

|

SU1015445A1 |

| Аналоговое запоминающее устройство | 1988 |

|

SU1535232A1 |

| Устройство фазовой автоподстройки частоты | 1991 |

|

SU1826135A1 |

| Устройство фазовой автоподстройки частоты | 1991 |

|

SU1811020A1 |

| СУММИРУЮЩАЯ ЛИНИЯ ЗАДЕРЖКИ | 1972 |

|

SU420095A1 |

| УСТРОЙСТВО ПОИСКА ПСЕВДОШУМОВЫХ РАДИОСИГНАЛОВ | 1990 |

|

RU2012138C1 |

| Дискретно-аналоговая линия задержки | 1982 |

|

SU1115230A1 |

| НАКОПИТЕЛЬ РАДИОЛОКАЦИОННЫХ СИГНАЛОВ | 1979 |

|

SU1840951A1 |

1

Изобретение относится к автоматике и вычислительной . технике и может быть использовано в различных аналогоцифровых измерительных системах для исследования параметров, быстропротекающих процессов.

Известно аналоговое запоминающее устройство, содержащее два накопительных элемента, блоки записи и подзаркда, КЛЮЧИ, блок управления и согласук щий усилитель til.

Однако известное устройство испол зуется ТОЛЬКО в одноканальной аппаратуре.

Наиболее близким к изобретению па технической сущности является аналоговое запоминающее аналоговое устройво, содержащее ячейки памяти, каждая из которых содержит элемент заряда, элемент считьшания и накопительный эле- мент, например конденсатор, одна из обкладок которого подключена к шине нулевого потенциала, а другая к эле- / менту заряда и к входу элемента счи«

2

тывания, управляющий генератор, вход которого является входом устройства, выходы управляющего генератора подключены к элементам заряда соответст- вукниих ячеек памяти, тактовый генератор , выход которого подключен к входу регистра сдвига, а выходы регистра сдвига подключены к выходам соответствующих элементов считьшання, выходной согласующий элемент, выход

10 последнего яртяется выходом устройства, генератор фонового тока, переключатель тока, один из входов которого подключен к выходу генератора фонового тока, другие - к выходам такто15вого генератора и выходной накопительный элемент, например конденсатор, одна из обкладок которого подключена к гяине нулевого потенциала, другая - к выходу переключателя тока и к входу вы20ходного согласующего элемента 23.

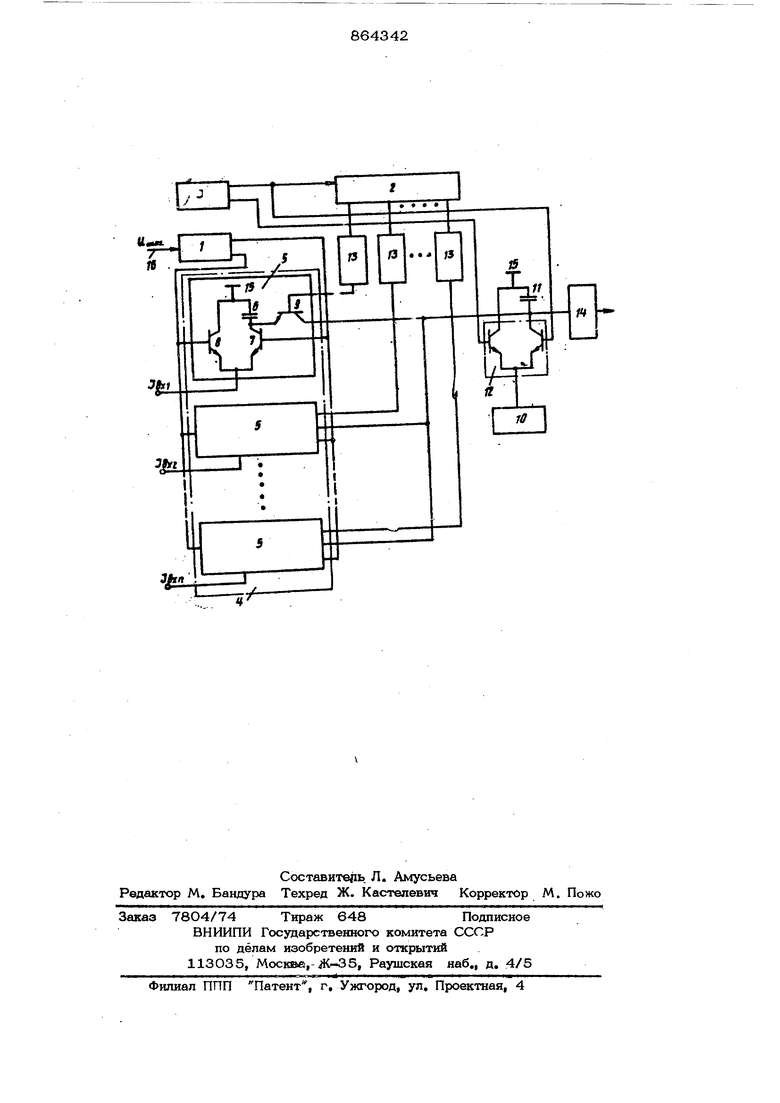

Одним из факторов, определяющих высокио точностные характеристики многоканального аналогового запоминающе3го устройства является использование метода переноса заряда для коммутации накопительных элементов - конденсаторо Пействительно, погрешность переноса заряда в известном устройстве, выполненном на дискретных элементах вызьшается потерями в базах транзисторов (активные потери) - элементов считывания и составляет величину около 1 при тактовых частотах до 10 мГц. С другой стороны, потенциально-достижимые точностные возможности многоканального аналогового запоминающего устройства не исчерпаны. Управление процессом считывания в известном устройстве осуществляется подачей отпирающих импульсов непосредственно от регистра сдвига на базы транзисторов - элементов считывания. Однако при скачкообразном переднем фронте тактового импульса в цепи разряда накопительного элемента в начальный момент времени возникает импуль большого тока. Цепь разряда накопитель ного элемента при этом является колебательным ко 1туром с малым затуханием, в которого происходит колебательный процесс с амтитудой, пропорциональной начальному напряжению на базе тран зистора - элемента считывания. Это пр1 водит к большим реактивным потерям заряда при считывании, или к недостаточной точности обработки мо- ноимпульсных сигналов, Цель изобретения - повышение точности аналогового запоминающего устройства. Поставленная цель достигается тем, что в аналоговое запоминающее устройство, содержащее основной накопитель, первые входы ячеек памяти которого со единены со входами устройства, зторые и третьи входы ячеек памяти основного накопителя подключены соответственно к выходам генератора управлякидих сигналов , вход которого соединен с щиной синхронизации, генератор тактовых импульсов, выходы которого соединены соответственно с первым и вторым входами переключателя тока, третий вход которого соедшен с выходом генератор фонового тока, первый выход переключа ля тока подключен к шине нулевого потенциала и к дополнительному накопител ному элементу, например, к одной из обкладок конденсатора , другая обкладка которого соединена со вторым выхояс;и переключателя тока, с выходами ячеек 2 памяти основного накопителя и со входом элемента согласования, выход которого соединен с выходом устройства, и регистр сдвига вход которого соединен с одним из выходов генератора тактовых импульсов, введены формирователи линейно-нарастающих импульсов, входы которых соединены с выходами регисгра сдвига, а выходы подключены к четвертым входам ячеек памяти основного накопителя. На чертеже изображена функциональная схема предложенного устройства. Устройство содержит генератор управляющих сигналов 1, регистр сдвига 2, генератор тактовьтх импульсов 3, основной накопитель 4, ячейки памяти 5 основного накопителя 4, каждая из которых выполнена на накопительном элементе, например конденсаторе 6, элементах заряда 7 и 8, элементе считывания 9, генератор фонового тока Ю, дополнительный накопительный элемент, например конденсатор 11, пе- реключатель тока 12, формирователи линейно-нарастающих импульсов 13, элемент согласования 14, шину нулевого потенциала 15 и Щ1ту синхронизации 16, Устройство работает следующим образом, При поступлении на вход генератора 1 сигнала синхронизации, генератор управляющих сигналов 1 вырабатьгоает сигналы, открывающие элемент заряда 7 и закрывающие элемент заряда 8, В это время конденсаторы 6 ячеек памяти 5 заряжаются входным током D ( t ). Элемент считьтания О заперт в течение времени накопления и хранения. Режим считывания осуществляется последовательной подачей отпирающих импу льсов от регистра сдвига 2 через формирователи линейно-нарастакмцих ик пульсов 13 на базы транзисторов элементов считывания 9, С помощью элемента счи- тьтания 9 осуществляется последовате/1ь- ный перенос накопленных на конденсаторах G зарядов в дополнительнь1Й конденсатор 11 и, таким образом, производится развертка во времени амплитудного распределения од1говременно возникающих анализируемых моноимпульсных сигналов. Поддержание готовности. к работе конденсатора 11 осуществляется непрерывным прохождением через него фонового заряда, который подается в него с помощью переключателя тока 12

от генератора фоновогхэ тока 10 с частотой, определяемой генератором тактовых импульсов 3.

Ограничение скорости нарастания переднего фронта тактовых импульсов, посредс гвом которых производится управление процессом считывания информационных зарядов, позволяет уменьшить реактивные потери заряда при переносе.

Минимальные реактивные потери заряда при переносе достигаются при использовании в качестве тактовых импульсов с линейно-нарастающей амплитудой. При такой форме тактовых .импульсов, разряд накопительных элементов производится постоянным током без колебательного процесса.

Таким образом, использование в предложенном устройство дополнительно введенных формирователей линейно-на- растающик импульсов, позволяет получить оптималы ый режим работы элементов считывания при переносе, и тем самым, повысить точность работы все - го устройства.

Формула изобретения

Аналоговое запом1шающее устройство, содержащее основной накопитель, пе|жые входы ячеок памяти которюго соединены . со входами устройства, вторые и третьи рходы ячеек памяти основного накопителя подключены соответственно к выходам генератора управляющих сигналов, вход которого соединен с шиной синхронизации , генератор тактовых импульсов, выходы которого соединены соот

ветственно с первьп и вторым входами переключателя тока, третий вход которого соединен,, с выходом генератора фонового тока, первый выход переклн чателя тока подключен к шине нулевого потенциала и к дополнительному накопительному элементу, например, к одной из обкладок конденсатора, другая обкладка которого соединена со вторым выходом переключателя тока, с выходами ячеек

памяти основного накопителя и со входом элемента согласовани, выход которого соединен с выходом устройства, и регистр сдвига, вход которого соединен с одним из выходов генератора

тактовых импульсов, о тли чаюшее с я тем, что, с целью повышения точности устройства, в него введены формирователи линейно-нарастакяцих импульсов, входы которых соединены с

выходами регистра сдвига, а выходы подключены к четвертым входам ячеек памяти основного накопителя.

Источники информации, принятые во внимание при экспертизе

2,Авторское свидетельство СССР по заявке № 2699727/18-24 , кл.«;11 С 27/00, 1978 (прототип

Авторы

Даты

1981-09-15—Публикация

1979-12-25—Подача