1

Изобретение относится к запоминающим устройствам.

Известно буферное запоминающее устройство, содержащее адресный накопитель, к выходным щинам которого подключен вход первого счетчика, а к входным - входы второго счетчика и реверсивного счетчика, узел управления.

Недостатком известного устройства является малая надежность его работы.

Описываемое буферное запоминающее устройство отличается от известного тем, что оно содержит дещифратор нулевого состояния первого счетчи.ка. Причем входы дещифратора подключены к выходам первого счетчика, а выходы - к выходам второго счетчика и ко входам реверсивного счетчика.

Это позволяет повысить надежность работы устройства.

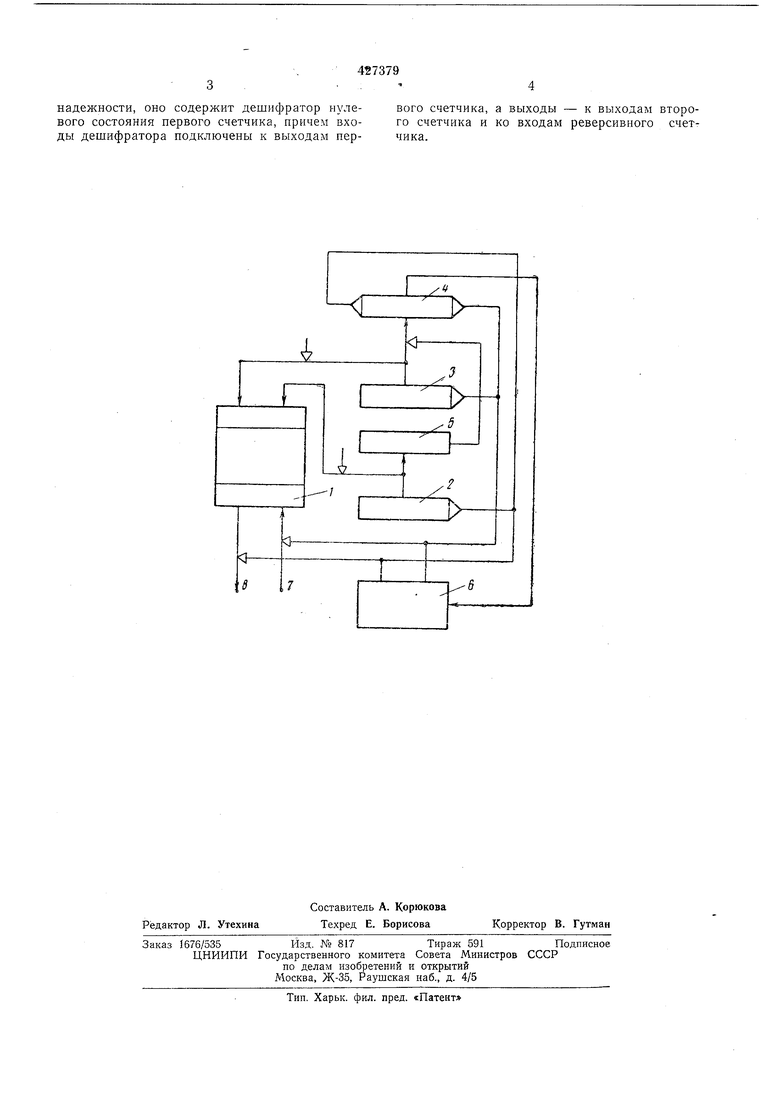

На чертеже изображена блок-схема буферного ЗУ.

ЗУ содержит адресный накопитель 1, счетчик 2, счетчик 3, реверсивный счетчик 4, дещифратор 5 нулевого состояния счетчика 2, узел управления 6, входные 7 и выходные 8 щины адресного накопителя J.

Устройство начинает работать при произвольном состоянии его блоков.

При поступлении очередного сообщения

на щины 7 адресного накопителя 1 оно записывается в накопитель по адресу, равному содержимому счетчика 3. При этом содержимое -счетчиков 3 и 4 увеличивается на единицу.

Считывание очередного сообщения из адресного накопителя на выходные щины 8 производится ио адресу, равному содержимому счетчика 2. После считывания очередного сообщения содержимое счетчика 2 увеличивается на единицу, а содержимое реверсивного счетчика 4 уменьщается на единицу. Дещифратор 5 производит анализ значения счетчика 2 и, если оно равно нулю, содержимое счетчика 3 переписывается в реверсивный счетчик 4.

Всеми операциями управляет узел управления 6.

После первой переписи содержимого счетчика 3 в реверсивный счетчик 4 буферное ЗУ продолжает работать аналогично.

Предмет изобретения

Буферное запоминающее устройство, содержащее адресный накопитель, к выходным щинам которого подключен вход первого счетчика, а к входным - входы второго счетчика и реверсивного счетчика, узел управления, отличающееся тем, что, с целью повышения

надежности, оно содержит дешифратор HVvieвого состояния нервого счетчика, причем входы дешифратора подключены к выходам первого счетчика, а выходы - к выходам второго счетчика и ко входам реверсивиого счетчика.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения вычислительной машины с каналами связи | 1986 |

|

SU1363224A1 |

| Буферное запоминающее устройство | 1978 |

|

SU767836A1 |

| Устройство согласования потока сжатых приоритетных сообщений с каналом связи | 1973 |

|

SU492042A1 |

| Устройство для управления системой контроля цифровых схем | 1975 |

|

SU560226A1 |

| ЛОГИЧЕСКОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1972 |

|

SU428450A1 |

| Мультипроцессорная система | 1983 |

|

SU1156088A1 |

| Буферное запоминающее устройство | 1985 |

|

SU1261012A1 |

| Устройство для управления оперативным накопителем | 1977 |

|

SU656106A1 |

| Буферное запоминающее устройство | 1984 |

|

SU1226530A1 |

| Устройство для приема дискретной информации в системах с решающей обратной связью | 1986 |

|

SU1478361A1 |

Даты

1974-05-05—Публикация

1971-12-10—Подача