Изобретение относится к вычислительной технике и может быть использовано при построении буферных запоминающих устройств (БЗУ) для каналов ввода измерительной информации в системы обработки данных.

Цель изобретения - увеличение эффективной емкости накопителя.

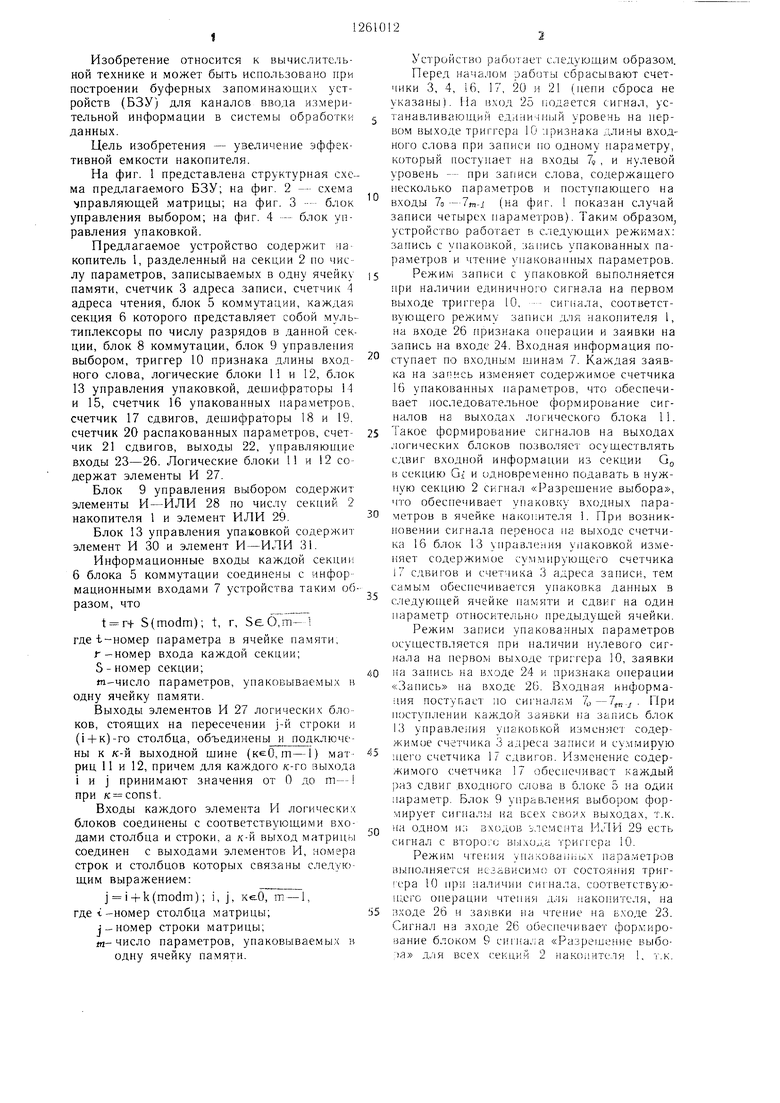

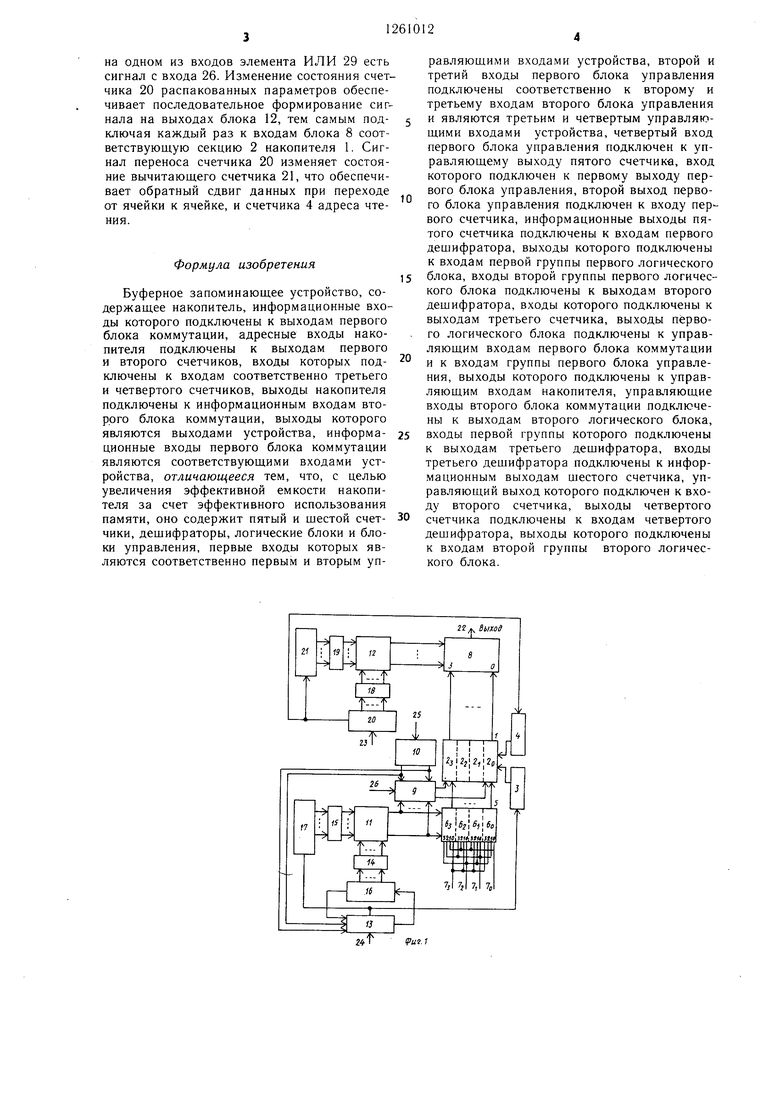

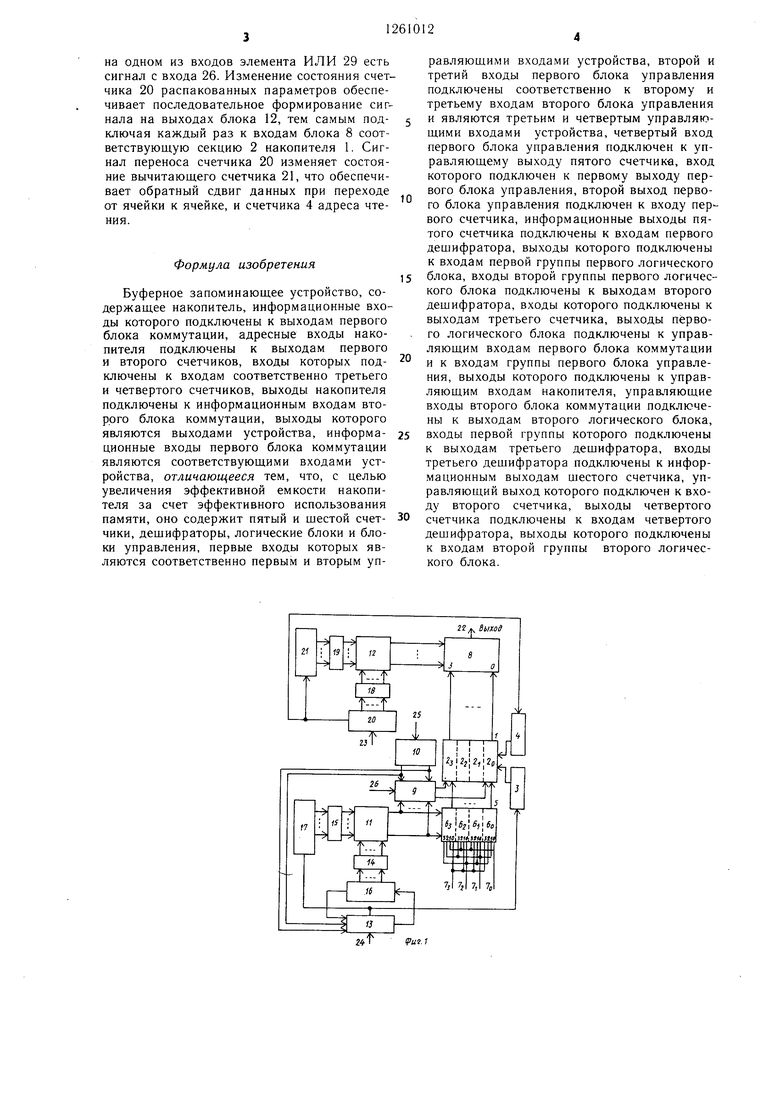

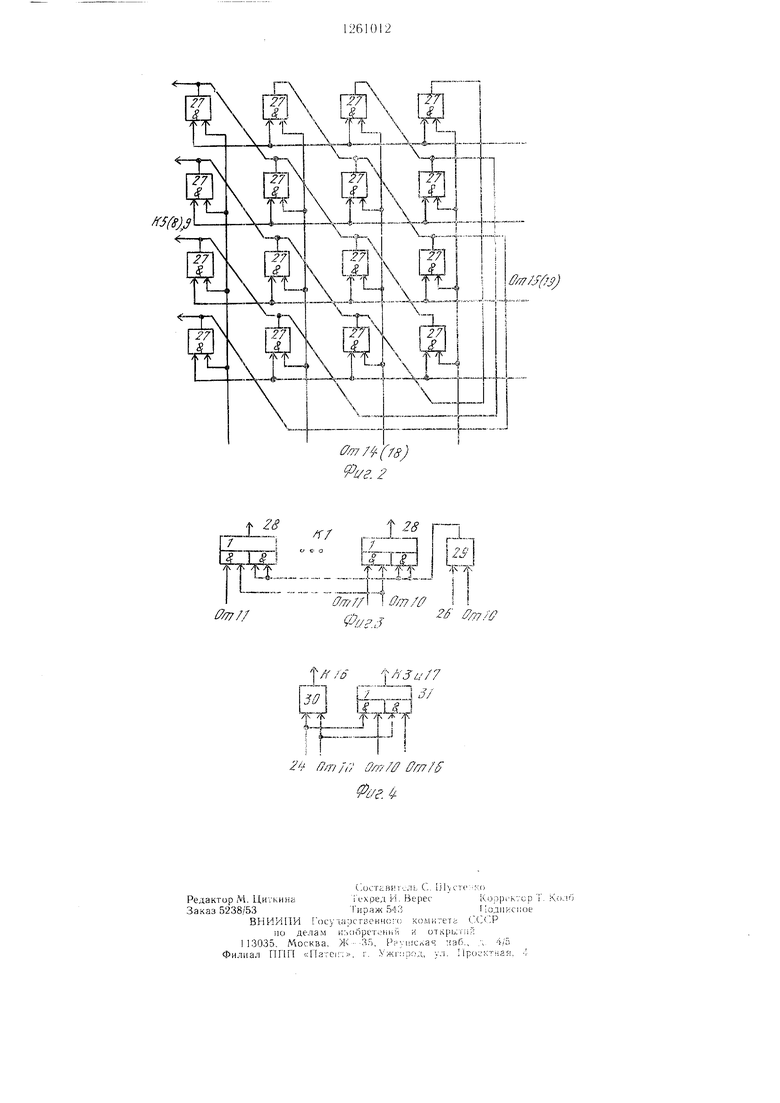

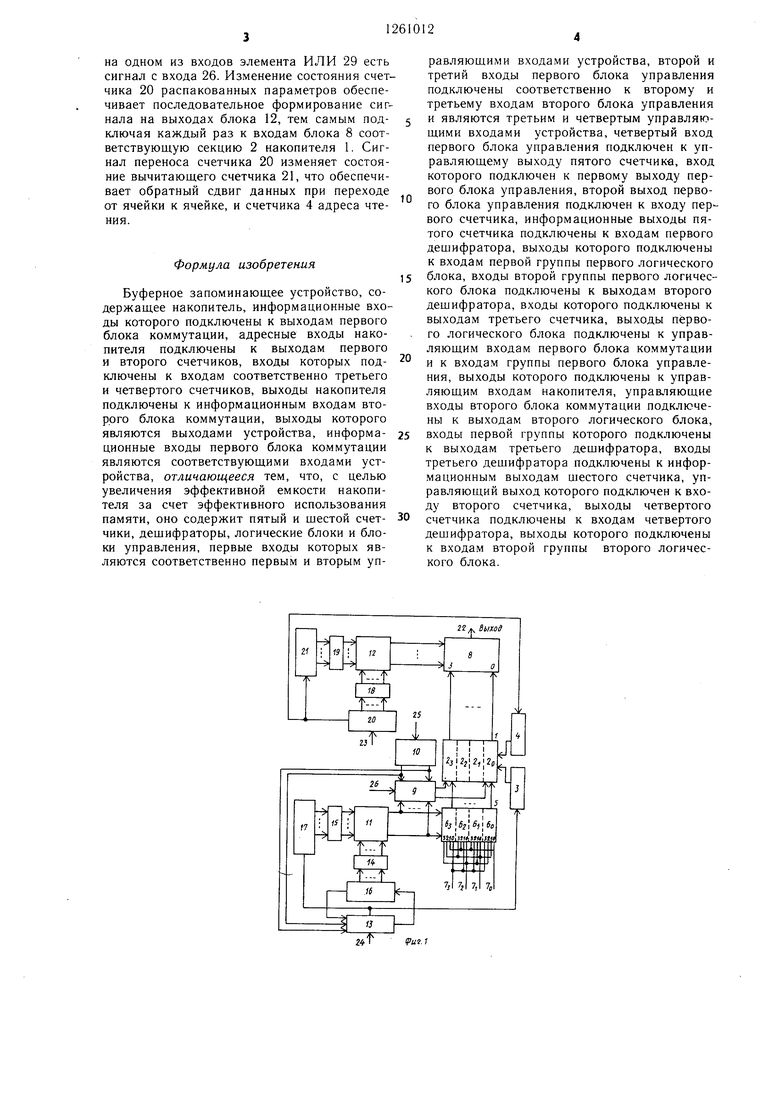

На фиг. 1 представлена структурная схема предлагаемого БЗУ; на фиг. 2 - схема управляющей матрицы; на фиг. 3 - блок управления выбором; на фиг. 4 - блок управления упаковкой.

Предлагаемое устройство содержит sia копитель 1, разделенный на секции 2 по чис лу параметров, записываемых в одну ячейку памяти, счетчик 3 адреса записи, счетчик 4 адреса чтения, блок 5 коммутации, каждая секция 6 которого представляет собой мультиплексоры по числу разрядов в .аанной секции, блок 8 коммутации, блок 9 управления выбором, триггер 10 признака длины вход ного слова, логические блоки 11 и 12, блок 13 управления упаковкой, дешифраторы 14 и 15, счетчик 16 упакованных параметров, счетчик 17 сдвигов, дешифраторы 18 и 19. счетчик 20 распакованных параметров, счетчик 21 сдвигов, выходы 22, управляющие входы 23-26. Логические блоки 1 и 12 со держат элементы И 27.

Блок 9 управления выбором содержит элементы И-ИЛИ 28 по числу секций 2 накопителя 1 и элемент ИЛИ 29.

Блок 13 управления упаковкой содержит элемент И 30 и элемент И-ИЛИ 31.

Информационные входы каждой секции 6 блока 5 коммутации соединены с инфор мационными входами 7 устройства таким образом, что

t r+ S(modm); t, г, SeO.m- 1 гдei-нoмep параметра в ячейке памяти,

г-номер входа каждой секции;

S-номер секции;

т-число параметров, упаковываемы;; н одну ячейку памяти.

Выходы элементов И 27 логических бло ков, стоящих на пересечении j-й строки и (i+K)-ro столбца, объединены и подключе- вы к /с-й выходной щине (кеО, m-i) матриц И и 12, причем для каждого к-го выхода i и j принимают значения от О до m- J при /c const.

Входы каждого элемента И логических блоков соединены с соответствующими входами столбца и строки, а к-й выход матрицы соединен с выходами элементов И, номера строк и столбцов которых связаны следующим выражением:

j j..fk(modm); i, j, к&б, т - 1, где -номер столбца матрицы; j..-номер строки матрицы; от- число параметров, упаковываемых в одну ячейку памяти.

5

0

5

0

5

Устройстно работает следующим образом.

Перед началом работы сбрасывают счетчики 3, 4, 16, 17, 20 и 21 (цепи сброса не указаны), iia и.ход 25 подается сигнал, ус- танавливаюпх.ий единичный уровень на первом выходе триггера 10 признака длины входного слова при записи по одному 1араметру, который поступает па входы 7, , и нулевой уровень -- при заг1иси слова, содержащего несколько параметров и поступающего на входы 7о -7rr, i (на фиг. 1 показан случай записи четырех пара.метров). Таким образом, устройство работает в следующих режимах: запись с упаковкой, :1а11ись упакованных параметров и чтение упакованных параметров.

Режим записи с упаковкой выполняется при наличии единичног О сигнала на первом выходе триггера 10, -- сигнала, соответствующего режиму записи для накопителя 1, на входе 26 признака операции и заявки на запись па входе 24. Входная информация поступает по входным щина.м 7. Каждая заявка па заги- сь изменяет содержимое счетчика

16упакованных параметров, что обеспечивает последовательное формирование сигналов на выходах логического блока 11. Такое формирование сигналов на выходах логических блоков позволяет осуществлять сдвиг входной информации из секции Gg в секцию Gi и одновременно подавать в нужную секцию 2 сигнал «Разрещепие выбора, что обеспечивает упаковку входных параметров в ячейке накопителя 1. При возникновении сигнала переноса па выходе счетчика 16 блок 13 упразле:ния упаковкой из.че- няет содержимое су.ммируиащего счетчика

17СДВИ1-ОВ и счетчика 3 адреса записи, тем самы.м обеспечивается у 1аковка данных в следующей ячейке памяти и сдвиг на один параметр отиосителычо предыдущей ячейки.

Режим записи упакованных параметров осуществляется при наличии нулевого сигнала на первом выходе триггера 10, заявки lia запись па входе 24 и признака операции «Запись на входе 26. Входная информа- 1ия поступает ио сигналя.м ,;, -7, . При ноступлепии каясдой заявки па зап:ись блок 13 уг1равле1 ия упаковкой изменяет содержимое счетчика 3 адреса записи и су.ммирую щего счетчика 17 сдвигов. Измспение содержимого счетчика 17 обеспечивает каждый раз сдвиг .входного слова в блоке 5 на одип параметр. Блок 9 управлепия выбором фор- : лирует сигналы на всех своих :выходах, т.к. па oдlioм и;; входов лсмемта ИЛИ 29 есть сигпал с второго выхо..ла триггера 10.

Режим чтения унаковапиых параметров вьпюлняется независимо от состояния триг- Хфа 10 при наличии сигнала, соответствующего операции чтепия дли :г1акоиитсля, па входе 26 и заявки на чтение на входе 23. Сигнал на входе 26 обеспечивает формирование блоком 9 еи1 на.ча «Разрешение выбо- для всех секций 2 накопителя 1, т.к.

на одном из входов элемента ИЛИ 29 есть сигнал с входа 26. Изменение состояния счетчика 20 распакованных параметров обеспечивает последовательное формирование сигнала на выходах блока 12, тем самым подключая каждый раз к входам блока 8 соответствующую секцию 2 накопителя 1. Сигнал переноса счетчика 20 изменяет состояние вычитающего счетчика 21, что обеспечивает обратный сдвиг данных при переходе от ячейки к ячейке, и счетчика 4 адреса чтения.

Формула изобретения

Буферное запоминающее устройство, содержащее накопитель, информационные входы которого подключены к выходам первого блока коммутации, адресные входы накопителя подключены к выходам первого и второго счетчиков, входы которых подключены к входам соответственно третьего и четвертого счетчиков, выходы накопителя подключены к информационным входам второго блока коммутации, выходы которого являются выходами устройства, информационные входы первого блока коммутации являются соответствующими входами устройства, отличающееся тем, что, с целью увеличения эффективной емкости накопителя за счет эффективного использования памяти, оно содержит пятый и шестой счетчики, дешифраторы, логические блоки и блоки управления, первые входы которых являются соответственно первым и вторым уп

равляющими входами устройства, второй и третий входы первого блока управления подключены соответственно к второму и третьему входам второго блока управления и являются третьим и четвертым управляющими входами устройства, четвертый вход первого блока управления подключен к управляющему выходу пятого счетчика, вход которого подключен к первому выходу первого блока управления, второй выход первого блока управления подключен к входу первого счетчика, информационные выходы пятого счетчика подключены к входам первого дешифратора, выходы которого подключены к входам первой группы первого логического блока, входы второй группы первого логического блока подключены к выходам второго дешифратора, входы которого подключены к выходам третьего счетчика, выходы первого логического блока подключены к управляющим входам первого блока коммутации и к входам группы первого блока управления, выходы которого подключены к управляющим входам накопителя, управляющие входы второго блока коммутации подключены к выходам второго логического блока, входы первой группы которого подключены к выходам третьего дешифратора, входы третьего дешифратора подключены к информационным выходам шестого счетчика, управляющий выход которого подключен к входу второго счетчика, выходы четвертого счетчика подключены к входам четвертого дешифратора, выходы которого подключены к входам второй группы второго логического блока.

| название | год | авторы | номер документа |

|---|---|---|---|

| Буферное запоминающее устройство | 1986 |

|

SU1363308A1 |

| Буферное запоминающее устройство | 1987 |

|

SU1439681A1 |

| Буферное запоминающее устройство | 1982 |

|

SU1049968A1 |

| Буферное запоминающее устройство | 1984 |

|

SU1163358A1 |

| Адаптивная система обработки данных | 1985 |

|

SU1312596A1 |

| Устройство для преобразования Хо изображения | 1990 |

|

SU1785004A1 |

| Адаптивная система обработки данных | 1987 |

|

SU1455342A1 |

| Программируемое устройство для контроля цифровых систем | 1986 |

|

SU1439588A1 |

| Устройство для обработки элементов сканерных изображений | 1983 |

|

SU1134945A1 |

| Буферное запоминающее устройство | 1985 |

|

SU1297115A1 |

Изобретение относится к области вычислительной техники и может быть использовано при построении буферных запоминающих устройств для каналов ввода измерительной информации в системы обработки данных. Цель изобретения - увеличение эффективной емкости накопителя. Устройство позволяет совместить функции упаковки и распаковки данных с распределением отказов между каналами измерительной системы. Цель достигается осуществлением установки данных в режиме записи информации из одного канала по формату, характерном для режима работы устройства с несколькими каналами, и последующей распаковкой данных на выходе устройства. Блок коммутации осуществляет запись последовательных данных одного канала в секции накопителя по одному адресу до полного заполнения одной информационной ячейки. Алгоритм работы блока коммутации задается с помощью блока управления, дешифраторов, счетчиков и логического блока. Распаковка данных осуществляется блоком коммутации, обеспечивающим последовательную выдачу информационных слов на выход устройства из одной ячейки памяти накопителя. Режим работы блока коммутации задается логическим блоком, дещифраторами, счетчиками. Адреса записи и считывания задаются счетчиками. 4 ил. (Л ю О5

Риг.1

тз

(fS)

±1.

/г/

r-r-T-

H

Ur...

b

-ir f

.„. -м.,-,.„„,„.,..«.4;.,..„ ff/77/ff i I

,- ff/77/ff

t 28

r-r-T-

-ir f

„,„.,..«.4;.,..„ ff/77/ff

bP

L..Jl-....j.;.-L,,,j

/14 /fr/ A™ /fr

,...J I I

I ...

2 amj i; ffm/ff I} rf7/ff fe

| Буферное запоминающее устройство | 1979 |

|

SU809358A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Разборный с внутренней печью кипятильник | 1922 |

|

SU9A1 |

Авторы

Даты

1986-09-30—Публикация

1985-03-15—Подача