1

Изобретение относится к области техники, занимающейся вопросами разработки быстродействующих преобразователей аналоговых сигналов в двоичный код.

Известен аналого-цифровой преобразователь считывания, содержащий блок сравнивающих устройств, блок эталонных уровней, п-разрядный триггерный регистр, блок считывания, состоящий из () схем «И, генератор п последовательных во времени тактовых импульсов и устройство управления.

Однако для запоминания состояний сравнивающих устройств требуется иметь, напр.имер, дополнительный триггерный регистр, содержащий () триггеров в случае преобразования аналогового сигнала в «-разрядный двоичный код.

Предлагаемый преобразователь отличается тем, что, в нем () схем «И блока считывания, имеющих (п-/г-|-2) входа, соединены первыми входами с выходами сравнивающих устройств, выходами подсоединены к единичному входу k-ro триггера регистра, вторые входы схем «И соединены с fe-ым выходом генератора тактовых импульсов, а остальные (п-k входов каждой из схем «И соединены с выходами всех (п-fe) старщих триггеров регистра.

Это упрощает конструкцию устройства и исключает погрешности преобразования из-за неоднозначности выходных сигналов сравнивающих устройств.

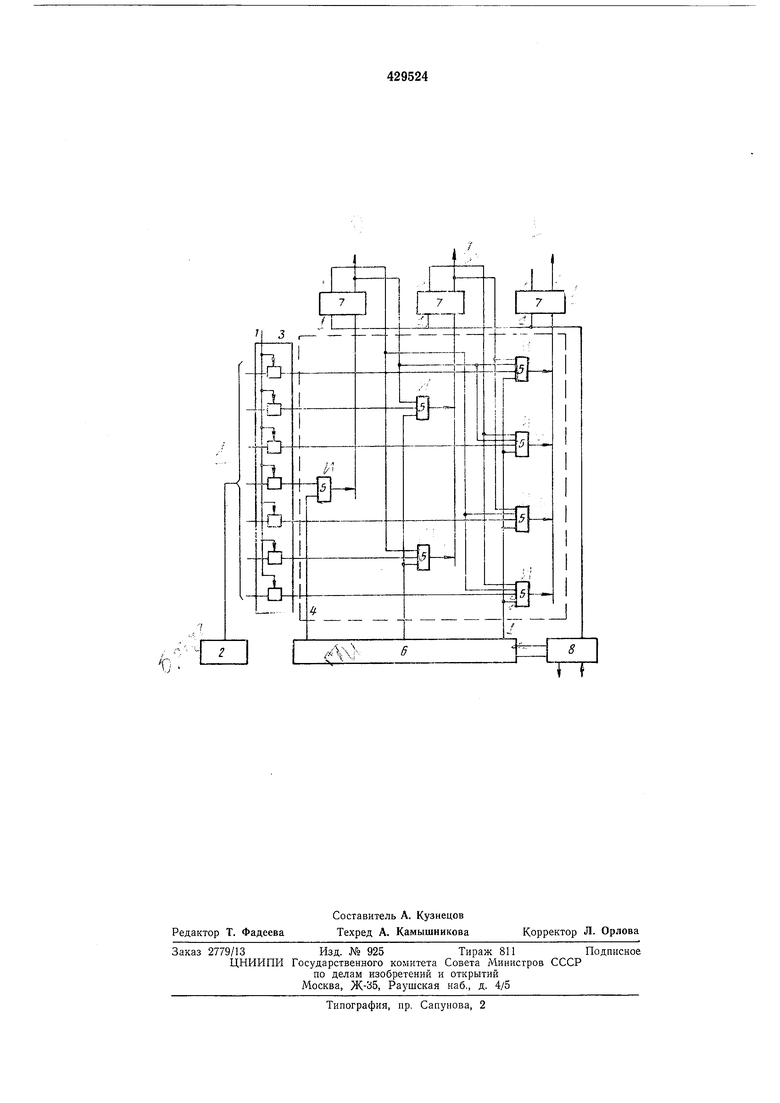

На чертеже изображена блок-схема трехразрядного аналого-цифрового преобразователя считывания.

Устройство работает следующим образом. В результате совместного действия преобразуемого аналогового снгнала 1 и эталонных сигналов сравнения, формируемых блоком эталонных уровней 2, на выходах блока сравниваюи,их устройств 3 образуется унитарный код. С выходов блока сравнивающих усгройств 3 сигналы подаются на входы блока считывания и записи 4, который выполнен на схемах «И 5. Кроме того, блок считывания и записи 4 соединен с выходными сигналами триггерного регистра, в котором фиксируется код результата аналого-цифрового преобразования после промежуточного преобразования унитарного кода в двоичный.

На входы схем «И 5 блока считывания и записи 4 подаются также сигналы с введенного в схему преобразователя генератора тактовых импульсов 6. В общем случае для п-разрядного преобразователя блок считывания и записи 4 содержит () схем «И 5, т. е. их количество равно количеству сравнивающих устройств блока 3. Все схемы «И 5 блока считывания и записи 4 разделены на п групп но 2 (п-k) схем «И в fe-ой группе, каждая схема «И имеет (п-й+2) входов. Выходы схем «И в k-ои группе объединены и соединены с 1-ым 5 входом /е-ого триггера 7 триггерного регистра. Перед началом считывания и записи результата преобразования триггеры 7 триггериого регистра устанавливаются в исходное состояние по сигналу, поступающему из уст- Ю ройства управления 8, который запускает также и генератор последовательных во времени тактовых импульсов 6. Первым по времени появляется импульс на я-ом выходе генератора тактовых импуль- 15 сов 6, последним - на первом выходе. Первые входы схем «И 5 й-ой группы объединены и соединены с й-ым выходом генератора тактовых импульсов 6. Второй вход любой из схем «И 5 соединен индивидуально с выхо- 20 дом соответствующего сравнивающего устройства блока 3. Остальные (п-k) входов схем «И 5 д-ой группы блока считывания и записи 4 соединены с соответствующими выходами (п-/г) старщих триггеров 7 регистра. 25 В результате указанных взаимосвязей с появлением импульса на fe-ом выходе генера тора тактовых импульсов 6 в k-ъш триггер 7 триггерного регистра записывается информация, в соответствии с выходным сигналом 30 того сравнивающего устройства, для которого становится открытой схема «И 5, подсоединенная к 1-му входу этого k-то триггера 7 триггерного регистра. Таким образом, последним выходным импульсом генератора такто- 35 вых импульсов 6 в триггерный регистр занишется код, эквивалентный преобразуемому унитарному коду. В схеме исключается неоднозначность преобразования унитарного кода в двоичный и 40 последующей записи его в регистр. Объясняется это тем, что «граничное сравнивающее устройство, имеющее неустойчивый выходной уровень или уровень промежуточный между нулевым и единичным, не влияет на запись кода в последующие младшие триггеры регистра, так как записью кода в них управляют выходные сигналы предыдущих старщих триггеров регистра, имеющие устойчивые уровни. Предлол енная взаимосвязь схем «И с выходами сравнивающих устройств, триггерным регистром и генератором тактовых импульсов не допускает общей погрешности преобразования, превыщающей единицу младщего разряда, поскольку в каждом такте запись кода в триггер регистра производится только через одну схему «И группы, подключенную к сравнивающему устройству, эквивалентный код уровня сравнения которого отличается от эквивалентного кода сравнивающего устройства, участвующего в предыдущем такте записи, не менее чем на 2 единицы младщего разряда, за исключением последнего такта записи, Предмет изобретения Аналого-цифровой преобразователь считывания, содержащий блок сравнивающих устройстз, блок эталонных уровней, л-разрядный триггерный регистр, блок считывания, состоящий нз () схем «И, генератор п последовательных во времени тактовых импульсов и устройство управления, отличающийся тем, что, с целью его упрощения и исключения погрешности преобразования из-за неоднозначности выходных сигналов сравнивающих устройств, в нем () схем «И блока считывания, имеющих (п-А;- -2) входа, соединены первыми входами с выходами сравнивающих устройств, выходами подсоединены к единичному входу k-ro триггера регистра, вторые входы схем «И соединены с -ым выходом генератора тактовых импульсов, а остальные (п-k) входов каждой из схем «И соединены с выходами всех (п-k) старших триггеров регистра.

| название | год | авторы | номер документа |

|---|---|---|---|

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 1972 |

|

SU428547A1 |

| Аналого-цифровой преобразователь | 1971 |

|

SU447825A1 |

| Многоканальное аналого-цифровое устройство задержки | 1983 |

|

SU1256150A1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ СО СТАТИСТИЧЕСКОЙ ОБРАБОТКОЙ РЕЗУЛЬТАТОВ | 1973 |

|

SU389623A1 |

| УНИВЕРСАЛЬНАЯ ЦИФРОВАЯ УПРАВЛЯЮЩАЯ МАШИНА | 1965 |

|

SU170218A1 |

| Устройство для преобразования малокадрового телевизионного стандарта | 1985 |

|

SU1256245A1 |

| Устройство для дискретного преобразования Фурье | 1984 |

|

SU1188751A1 |

| Аналого-цифровой преобразователь | 1986 |

|

SU1325696A1 |

| Устройство для регистрации информации | 1985 |

|

SU1304170A1 |

| ПАРАЛЛЕЛЬНО-ПОСЛЕДОВАТЕЛЬНЫЙ ТРЕХТАКТНЫЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 1973 |

|

SU399061A1 |

Даты

1974-05-25—Публикация

1971-07-13—Подача