1

Изобрегеиме отиосится к области автОматики, вычисл.итель юй техники и измерительной техники.

Из1вест 1ы аиалого-цифрО|Вые преобразователи, содержащие л-разряднып триггеряый регистр и циф;роаналоговый иреобразователь, сра-вниеающее устройство с инверсным и иеинверсиым выходами, блок формирования уровней сравнения и блок управления.

С целью Знач ительиого снижения требоваиий к оонювиым характеристикам и упроще}|ия с.хемкой реализаиии сравнивающего устройства, повышения быстродействия и досто ер1иости иреобразования в иредла1-аемое устройство введены цифроуиравляемый резистор, (n-j-l) управляющие входы которого соединены с соответствующи-ми тактовыми выходами блока управления, два дополнительных, анал-огичных основио.чу,сравнивающих устройств, iiepBbie входы которых объединены и соединены Свыходами цифроаиалогового преобразователя и цифроуправляемого резистора, вторые входы индивидуально соединены с соответствующИ.ми выходами блока формирования уровней сразнения, и схемы «И на два входа, а также триггерНый регистр выполнен в виде реверсивного счетчика с входами ш вычитания в каждом разряде и имеет на этих входах одинаковые для кал ;дого разряда логические блоки, содержанию ио четыре схемы

«И и «ИЛИ, ири это. входы иервой и второй схем «ИЛИ логического блока К-го разряда соединены соответственно с единичны:, и и иулевыми выходами триггеров К старщих разрядов регистра, первые входы иервой, второй, третьей и четвертой схем «И соединены иидивидуальио с инверсным и иеииверсным выходами основного, инверсным выходом первого и иеннверсным выходом второго дополнйПельных сравнивающнх устройств соответственно, вторые входы первой и третьей схем «И соединены с выходо.м иервой схемы «ИЛИ, вторые входы второй н четвертой схем «И соединены соответственно с выходо.м

второй схемы «ИЛИ и выходом схемы «И на два входа, который также соединен с четвертым входом первой схемы «И, третьи входы иервой н второй схем «И н третьей и четвертой схем «И попарно объединены и соединены соответственно с К-мн ()-м тактовыми выходами блока унравлеиия; выходы иервой и третьей схем «И и второй 31 четверToii схе.м «И соединеиы соответственно с входами третьей и четвертой схем «ИЛИ,

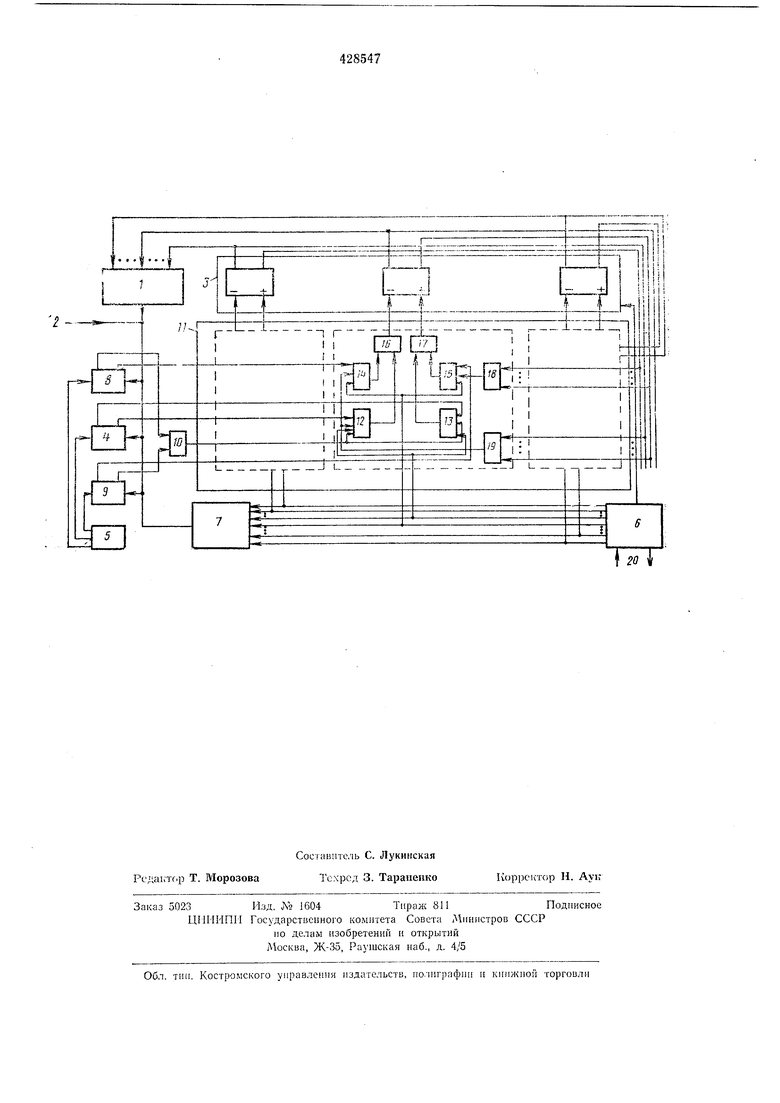

выходы которых подключены щщивидуально к нходам вычитания и сложения К-го разряда регистра, а неинверсный выход первого и инверсный выход второго дополннтельных сравнивающнх устройств соедине)1ы с входами схемы «И на два входа. На чертеже представлена блок-схема прсхт,лагаемого аналого-цифрового преобразователя. Устройство содержит цифроаналоговый преобразователь 1 типа код-ток, выход которого соединен с входом 2, предназначенным для подключения аналогового сигнала тока, триггерный регистр 3 формирования кода результата преобразования, сравнивающее устройство 4, блок 5 формирования уровней сравнения, блок 6 управления, вырабатывающий необходимые для поразрядного кодирования тактовые сигналы, цифроуправляемый резистор 7, два дополнительных сравнивающих устройства 8 и 9, схему «И 10 на два входа и логический блок 11. Триггерный регистр 3 выполнен в виде реверсивного счетчика с входами сложения и выч1итания в каждом разряде. Логический блок 11 для каждого из п-разрядов регистра содержит схемы «И 12-15 и схемы «ИЛИ 16-19 и вход 20. В предлагаемом преобразователе сравнивающее устройство 9 имеет верхнюю границу порога срабатывания /вх. макс-У, а 1 нижнюю -(), где /EX. млкс - максимальная величина входного сигнала, а R - величина сопротивления цифро-управляемого резистора 7 в первом такте преобразования, Сравнивающее устройство 4 имеет соответственно вернюю границу () нижнюю границу ); сравнивающее устройст(- Еиакс) и во 8 имеет верхнюю границу нижнююграницу ( макс /комц. макс-), где /1СОМП. маис - максимальная величина комненсирующего сигнала обратной связи, вырабатываемого схемой цифроаналогового преобразователя /. Причем I-Емакс I I Maiic I И, следовательно, |/комп- маис : |/вх. макс I . предлагаемый аналого-цифровой преобразователь работает следующим образом. По сигналу, поступающему от устройства более высокого ранга на вход 20, блок 6 унравления вырабатывает оигнал, устанавливающий триггеры регистра 3 в «нулевое состояние. В блоке 6 вырабатывается сигнал первого такта, который устанавливает величину сопротивления в цифроуправляющем резисторе 7, равную R. На первых входах сравнивающих устройств образуется сигнал нанряжения /их-/. От блока 5 на вторые входы сравнивающих устройств 4, 8 к 9 постоянно нодаются уровни сравнения, номинальные зна22ЧеНИЯ которых равны О, и -j-.T-ZTnanc оJ Сигнал первого такта воздействует также через схемы логического блока 11 на входы регистра 3 п в зависимости от состояния сравнивающих устройств либо устанавливает триггер старшего разряда в «единичное состояние, либо оставляет его в «нулевом состоянии. После этого в блоке 6 вырабатывается сигнал второго такта. Во втором такте преобразования величина сопротивления цифроуправляющего резистора 7 устанавливается равной 2/. На объединенных входах сравнивающих устройств образуется сигнал, равный (/их- -/помп) 2R, где /комп - компенсирующий сигнал обратной связи, образованный в первом такте и равный либо нулю, либо величине /вх. макс/2. в зависимости от состояния триггера старшего .разряда регистра 3 и выходных сигналов сравнивающих устройств во втором такте может быть выработан сигнал сложения или вычитания, постзпающий в предыдущий (в данном случае старший) разряд регистра 5. Сигнал сложения вырабатывается в том случае, если все сравнивающие устройства 9, 4 н 8 находятся в «единичных состояниях, а один из предыдущих (в данном случае старший) разрядов регистра 3 - в «нулевом. Сигнал вычитания вырабатывается, если все сравнивающие устройства Р, 4 и 8 находятся в «нулевых состояниях, и хотя бы один из предыдущих (в данном случае старший) разрядов регистра 3 в «единичном, нричем при помощи схемы «И 10 на два входа запрещается подача сигналов сложения или вычитания во второй разряд регистра 3. Если же сравнивающие устройства 9, 4 и 8 находятся соответственно в состояниях 011 или 001, то вырабатываются сигналы сложения (011) или вычитания (001), поступающие в разряд регистра 3, соответствующий данному такту. При этом сигнал вычитания вырабатывается только в том случае, если один из предыдущих разрядов регистра 3 находится в «единичном состоянии. (За «единичное состояние сравнивающего устройства принимается такое состояние, когда на его неинверсиом выходе имеется уровень, открывающий схему «И). Для К-го разряда в К-ом такте сигнал на сложение или вычитание через схемы «И /5 и 12 и схемы «ИЛИ 17 и 16 поступает только в том случае, если сравнивающие устройства находятся в состояниях 011 или 001, так как в других случаях (сравиивающие устройства находятся в состояниях 000 или 111), сигнал, вырабатываемый схемой «И 10 на два входа, на вход которой присоединены «инверсный выход и «неинверсный выход сравиивающих устройств 9 и 8 соответственно, закрывает схемы «И 13 и 12. В то же время, если предыдущие старшие (К-1) разряды находятся в «нулевом состоянии, то схема «ИЛИ 19, на вход которой поступают «единичные выходы со всех предыдущих К триггеров регистра 3, запрещает прохождение сиг5:Налов вычитания через схему «И 12 и схему «ИЛИ 16, при этом запрет на сигнал сложения не нужен, так как начальное состояние К-го разряда регистра 3 в К-м такте «нулевое, и -поэтому он не может быть переполнен. В (К+1)-ом такте в случае, если сравнивающие устройства находятся в одном из двух состояний 000 или 111, вырабатываются через схемы «И 14 и 15 и схемы «ИЛИ 16 и 17 сигналы вычитания или сложения в К-й разряд регистра 3. Причем, если все /С предыдущих разрядов регистра 3 находятся в «нулевом, либо в «единичном состоянии, то благодаря наличию схем «ИЛИ 19 и 18 (входы схемы «ИЛИ 18 подсоединены к «нулевым выходам триггеров старщих К-разрядов репистра 3), прохождение этих сигналов через схемы «И 14 и 15 запрещается. Поскольку сонротивление цифроуправляемого резистора 7 в каждом такте увеличивается в два раза, уровень сигнала на объединенном входе сравнивающих устройств определяется выражением, К (,вх комп ) А , 1 где к-1, 2, п, (), ai - двоичная цифра i-ro разряда трцггерного регистра, принимающего значения О или «1, что обеспечивает постоянство динамического диапазона работы сравнивающих устройств. В то же время в данном аналого-цифровом преобразователе имеется возможность на последующих тактах исправить ощибки, возникающие раиее, в частности те, которые вызываются «грубостью сравнивающих устройств. Таким образом, требования к прецизионности сравнивающих устройств и блока формировання уровней сравнения значительно сиижаются, так как зона нечувствительности до самого последнего такта каждого из сравнивающих устройств может иметь величину, равЛуЮ :г- макс I . о Предмет изобретения Аналого-цифровой преобразователь, содержащий п-разрядный триггерный регистр и цифро-аналоговый преобразователь, сравнивающее устройство с инверсным и неинверс42иым выходами, блок формирования уровней сравнения и блок управления, отличающийся тем, что, с целью значительного снижения требований к основным характеристикам и упрощения схемной реализации сравнивающего устройства, новыщения быстродействия и достоверности преобразования, в него введены цифроуправляемый резистор, (п+1) управляющие входы которого соединены с соответствующими тактовыми выходами блока управления, два дополнительных, аналогичных основному, сравнивающих устройств, первые входы которых объединены и соединены с выходами цифро-аналогового преобразователя и цифроунравляемого резистора, вторые входы индивидуально соединены с соответствующими выходами блока формирования уровней сравнения, и схема «И на два входа, а триггерный регистр выполнен в виде реверсивиого счетчика с входами сложения и вычитания в разряде и имеет на этих входах одинаковые для каждого разряда логические блоки, содержащие по четыре схемы «И и «ИЛИ, при этом входы первой и второй схем «ИЛИ логического блока К-го разряда соединены соответственно с единичными и нулевыми выходами триггеров К, старших разрядов регистра, первые входы первой, второй, третьей и четвертой схем «И соединены индивидуально с инверсным и неинверсным выхода.ми основного, инверсным выходом первого и неинверсным выходом второго донолнительных сравнивающих устройств соответственно, вторые входы первой и третьей схем «И соединены с выходом первой схемы «ИЛИ, вторые входы второй и четвертой схем «И соединены соответственно с выходом второй схемы «ИЛИ и выходом схемы «И на два входа, который также соединен с четвертым входом первой схемы «И, третьи входы первой и второй схем «И и третьей и четвертой схем «И попарно объединены и соединены соответственное К-ым и (К+1)-ым тактовыми выходами блока управления; выходы первой н третьей схем «И и второй и четвертой схе.м «И соединены соответственно с входами третьей и четвертой схем «ИЛИ, выходы которых подключены индивидуально к входам вычитания и сложения К-го разряда регистра, а неинверсный выход первого и инверсный выход второго дополнительных сравнивающих устройств соединены с входами схемы «И на два входа.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для интегрированияпиКООбРАзНыХ фуНКций | 1978 |

|

SU813453A1 |

| СПОСОБЫ ВЫПОЛНЕНИЯ ЭЛЕМЕНТАРНЫХ ВЫЧИСЛИТЕЛЬНЫХ ОПЕРАЦИЙ (ЭВО) И УСТРОЙСТВО ИХ ОСУЩЕСТВЛЕНИЯ | 2013 |

|

RU2553221C2 |

| Аналого-цифровой преобразователь | 1974 |

|

SU1005305A1 |

| ДВОИЧНО-ДЕСЯТИЧНЫЙ НАКАПЛИВАЮЩИЙ СУММАТОР | 1971 |

|

SU293241A1 |

| Аналого-цифровой преобразователь с коррекцией динамических погрешностей | 1976 |

|

SU744968A1 |

| Аналого-цифровой преобразователь с самоконтролем | 1980 |

|

SU886236A2 |

| Преобразователь кода системы остаточных классов в позиционный код | 1986 |

|

SU1388997A1 |

| Арифметическое устройство | 1976 |

|

SU664171A1 |

| Устройство для отображения графической информации на экране электронно-лучевой трубки | 1982 |

|

SU1091177A1 |

| Устройство для контроля аналоговых объектов | 1986 |

|

SU1397941A1 |

Даты

1974-05-15—Публикация

1972-01-27—Подача