1

Изобретение относится к области техники, занимающейся вопросами разраборки быстродействующих аналого ци$ровых преобразователей с повышенной достоверностью результатов преобразования.

Известны аналого цифроБые преобразователи считывания, содержащие п разрядный триггерный регистр, выход которого соединен с дешифратором, а вход - с блоком поразрядной записи, блок из () сравнивающих устройств, который соединен с блоком эталонных уровней и с первыми входами () схем И, и блок управления. Однако в таких преобразователях могут возникнуть ошибки, значительно превышающие величину одного кванта неоднозначности считывания

В аналого цифровых преобразователях считывания количество используемых сравнивающих устройств превышает число разрядов результирующего кода, что увеличивает вероятность сбоя или выхода из строя

I какого либо сравнивающего устройства, В этом случае в схемах пре образования унитарного кода в двоичный погрешность преобразования

может достигать значительных величин. Например, в схеме с выделением наиболее старшего из сработавших сравнивающих устройств при их последовательном опросе ошибка

может достигать 100 преобразуемой величины. Кроме того, в схеме лоразрядного считывания может быть значительная погрешность преобразования, возникащая сбоя

или отказа сравнивающего устройства.

Предложенный аналого цифро;аой преобразователь отличается тем, что для повышения надежности он

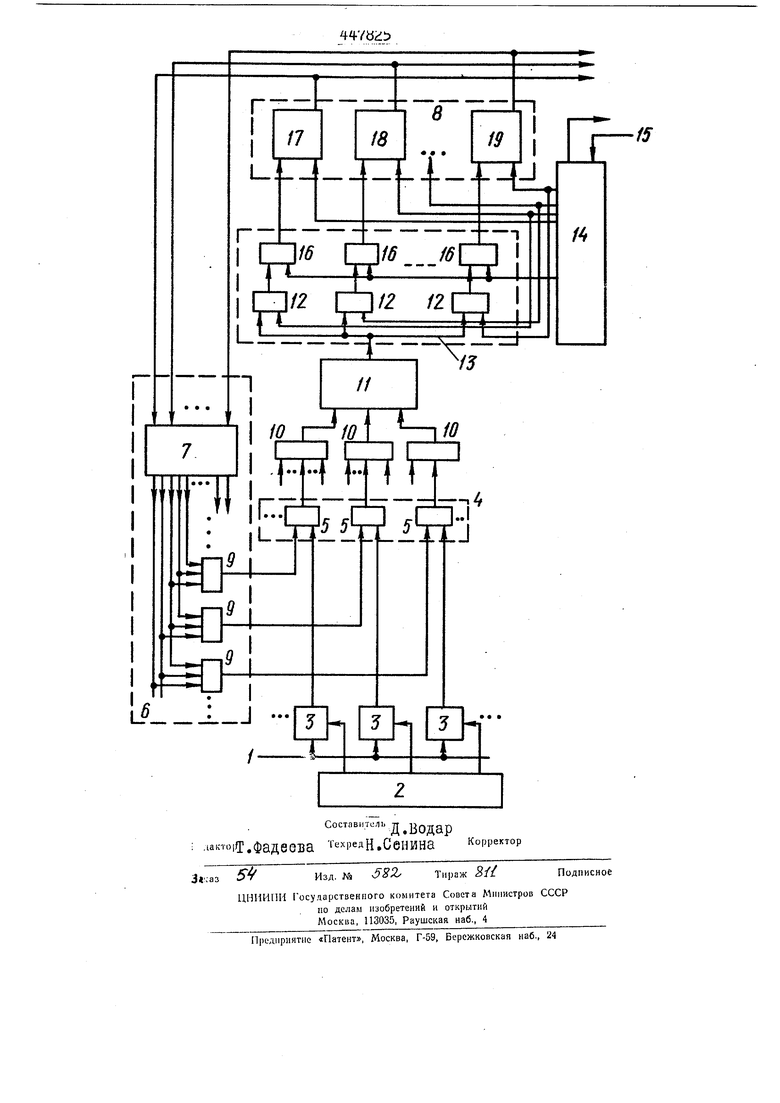

содержит мажоритарный элемент, ко входу которого подключены схемы ИЛИ, а выход мажоритарного элемента подключен ко входу блока поразрядной записи, и () схем ИЛИ, при этом каждый выход дешифратора соединен со входами трех 34 из этих схем МИ, у которых выходы соединены со вторыми входами схем И, а выходы этих схем И соединены со входавш ШИ мажоритарного элемента. На чертеже изображена схема предлагаемого преобразователя. В резрьтате совместного действия преобразуемого аналогового сигнала 1 и эталонных сигналов сравнения, формируемых блоком эталонных уровней 2, на выходах сравнивающих устройств 3 образуется параллельный унитарный код. Выходные сигналы сравнивающих устройств подаются на первые входы () схем И 5 блока считывания 4. На вторые входы этих схем подаются выходные сигналы устройства 6 выбора в блоке 4 группы из трех соседних схем И. Это устройство состоит из дешифратора 7, осуществляющего преобразование а разрядного двоичного кода с выходов регистра 8 в позиционный код, и ) трехвходовых схем ИЛИ 9. Причем, если на один из входов схемы 5 подсоедшен выход сравнивающего устройства, име ющего тот же номер, что и схема 5,.то на другой вход этой схемы подсоединен выход схемы 9 устройства б, на вход которой поданы выходы дешифратора 7, тюющие одноименный со схемой 5 номер, а также на единицу меньший и больший номера. Таким образом, каждый из выходов дешифратора выбирает группу из трех соседних схем И в блоке 4. Выходы этих схем индивидуально подсоединены ко входам трех схем МИ 10. Причем к каждой из них подсоединены выходы схем И, имеющие соответственно номера ЗК, ЗК-f 1 и 3IC+2 (ку- целое число). Общее число входов всех этих схем ИЛИ не превышает (). Выходы схем 10 индивидуально подсоединены на три входа мажоритарного элемента 11, осуществляющего выработку выходного сигнала по числу наибольших совпадений сигналов на выходах, т.е. так называвши выбор из трех. Сигнал с выхода элемента И подан на общий вход схем И 12 блока 13 поразрядной записи в регистр 8. Блок управления 14, начиная работу по внешнему сигналу 15, поступающему на его вход от устройства более высокого ранга, вырабатывает сигнал установки всех триггеров регистра 8 в нулевое состояt4uA. Этот сигнал поступает на об- дий вход схем ИЛИ 16 блока 13i другой вход которых индивидуально подсоединен на нулевой вход триггеров регистра 8. Затем блок упкавления выпабатывает последовательность тактовых сигналов, общее число которых равно /и-1. Сигнал первого такта устанавливает триггер 17 старшего разряда регистра 8 в единичное состояние. В результате этого после дешифрации кода регистра 8 в блоке 4 будут выбраны схемы И, на вход которых поступают сигналы от сравнивающих устройств, эквивалентных кодам/-, ,. Сигнал на выходе мажоритарного элемента 11 указывает на наличие либо отсутствие необходимости установки триггера старшего разряда регистра 8 в нулевое состояние во втором такте. Происходит так называемое взвешивание. В этом же такте триггер 18 следующего за старшим разряда безусловно устанавливается в единичное состояние. В зависимости от старшего разряда после дешифрации кода регистра выбирается новая тройка сравнивающих устройств, эквивалентная либо кодам и f -1, либо кодам , + 1 и f - 1. Этот процесс будет повторяться до тех пор, пока не будет закончено взвешивание самого младшего разряда (триггер 19) регистра 8. - При таком способе преобразования унитарного кода в двоичный в силу того, что в каждом такте осуществляется выбор трех соседних сравнивающих устройств с последующим выделением двух из трех, выход из строя какого либо одного из них не приводит к появлению дополнительной погрешности, превышающей величину одного кванта. Действительно, если величина входного сигнала 1 тйкова, что выбранные сравнивающие устройства должны иметь единичное состояние, т.е. код I I 1,.то выход из строя любого из них не повлияет на выодной сигнал мажоритарного элемента и, следовательно, на код, формируемый в регистре 8. Если же сравнивающие устройства должны иметь код ОН, то легко увидеть, то выход из строя сравнивающего

устройства, которое должно быть в единичном состоянии, приведет к ошибке, не превышающей одного кванта, невависимо от того, в каком такте считывания это сравнивающее устройство подключается к мажоритарному элементу.

Выход из строя сравнивающего устройства, которое должно быть в нулевом состоянии, как и в первом случае приводит к ошибке в результате преобразования, не превышающей одного кванта, легко показать то же самое и для других кодов, которые должны формироваться на выходах сравнивающих устройств: 000 и 001.

Если же предложенные меры отсутспвуют, неисправность сравнивающего устройства может привести к ошибке в любом разряде, определяемом этим устройством. Например, при минимальном или максимальном входном сигнале и выходе из строя сравнивающего устройства, соответствующего коду (старший разряд регистра), погрешность результата преобразования может составлять i.0. Это объясняется тем, что ложно записанная информация в старший разряд, например i вместо О или О вместо 1, не может быть скорректирована, если не принимать специальных мер.

Таким образом, в предложенном преобразователе с рассмотренными

взаимосвязями вновь введенных узлов исключается влияние на результат преобразования неправильной работы любого сравнивающего устройства. При этом не зависимо от места расположения этого сравнивающего устройства дополнительная погрешность преобразования не может превышать величину одного

кванта.

ПРЕДМЕТ ИЗОБРЕТЕНИЯ Аналого цифровой преобразователь, содержащий /г разрядный триггерный регистр, выход которого соединен с дешифратором, а вход с блоком поразрядной записи, блок из ( -1) сравнивающих устройств, который соединен с блоком эталонных уровней и с первыми входами (2.--1) схем И, и блок управления, отличающийся тем, что, с целью повышения надежности, он содержит мажоритарный элемент, ко входу которого подключены схемы ИЛИ , а выход мажоритарного элемента подключен ко входу блока поразрядной записи, и () схем ИЛИ, при этом каждый выход дешифратора соединен со входами трех из

ЭТИХ схем МИ, у которых выходы соединены со вторыми входами схем И, а выходы этих схем И соедийены со входами ИЛИ мажоритарного элемента.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство аналого-цифрового преобразования | 1982 |

|

SU1045378A1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ СЧИТЫВАНИЯ | 1971 |

|

SU429524A1 |

| Аналого-цифровой преобразователь двухтактного считывания | 1972 |

|

SU447828A1 |

| Мажоритарно-резервированный аналого-цифровой преобразователь | 1987 |

|

SU1444946A1 |

| Аналого-цифровой преобразователь | 1974 |

|

SU630743A1 |

| Устройство аналого-цифрового преобразования | 1986 |

|

SU1343551A1 |

| Программируемый аналого-цифровой преобразователь | 1987 |

|

SU1732469A1 |

| Способ многоканального аналого-цифрового преобразования и многоканальный аналого-цифровой преобразователь | 1986 |

|

SU1451858A1 |

| Многоканальный аналого-цифровой преобразователь | 1977 |

|

SU726664A1 |

| Аналого-цифровой преобразователь поразрядного кодирования | 1985 |

|

SU1325701A1 |

Авторы

Даты

1974-10-25—Публикация

1971-11-25—Подача