дом умножителя, информационные входы двоичных счетчиков группы являются информационным входом преобразователя, вход пуска которого соединен с входом пуска распределителя импульсов, второй выход умножителя соединен с входом вычитания первого двоично-десятичного счетчика грзшпы. 2. Преобразователь по п.1, о т ли чающийся тем, что в нем умножитель содержит счетчик, элемент И-НЕ, элемент НЕ, элемент И и элемент ИЛИ, входы которого являют:ся группой входов умножителя, а вы{ход элемента ИЛИ соединен с входом I сброса счетчика, выход старшего разряда которого через элемент НЕ соединен с первым входом элемента И, второй вход которого является тактовым входом умножителя, выходы которого являются выходами элементов И-НЕ и И соответственно, выход элемента И соединен с синхровходом счетчика .и первым входом элемента И-НЕ, второй вход которого соединен с выходом младшего разряда счетчика.

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь двоично-десятичного кода в двоичный | 1979 |

|

SU877521A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1987 |

|

SU1444958A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1984 |

|

SU1280702A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1981 |

|

SU1013942A1 |

| Преобразователь двоично-десятичной дроби в двоичную дробь | 1979 |

|

SU860053A1 |

| Преобразователь двоично-десятичных чисел в двоичные | 1982 |

|

SU1048469A1 |

| ПРЕОБРАЗОВАТЕЛЬ ДВОИЧНО-ДЕСЯТИЧНОЙ ДРОБИ В ДВОИЧНУЮ ДРОБЬ | 1979 |

|

SU826335A1 |

| Преобразователь двоичных чисел в двоично-десятичные числа | 1980 |

|

SU941990A1 |

| Преобразователь последовательного двоичного кода в параллельный двоично-десятичный код | 1982 |

|

SU1084780A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1985 |

|

SU1283979A1 |

1. ПРЕОБРАЗОВАТЕЛЬ ДВОИЧНОГО КОДА В ДВОИЧНО-ДЕСЯТИЧНЫЙ, содержащий группу двоичных счетчиков, первую группу элементов И, распределитель импульсов, генератор импульсов, первую группу элементов ИЛИ, элемент задержки, умножитель, группу дв.оично-десятичньк счетчиков, разрядные выходы которых являются выходами преобразователя, выход переноса i-ro двоично-десятичного счетчика группы (h-1)J, где (п+1) - число разрядов выходного кода, соединен с первым входом i-ro элемента ИЛИ первой группы, выход которого соединен с входом сложения (.п+1)-го двоично-десятичного счетчика группы, выход переноса п-го двоично-десятичного счетчика группы соединен с входом сложения (п+1)-го двоично-десятичного счетчика группы, выходы распределителя импульсов соединены с первыми входами соответствующих элементов И первой группы, выходы которых соединены со счетными входами соответствующих двоичных счетчиков группы, выход

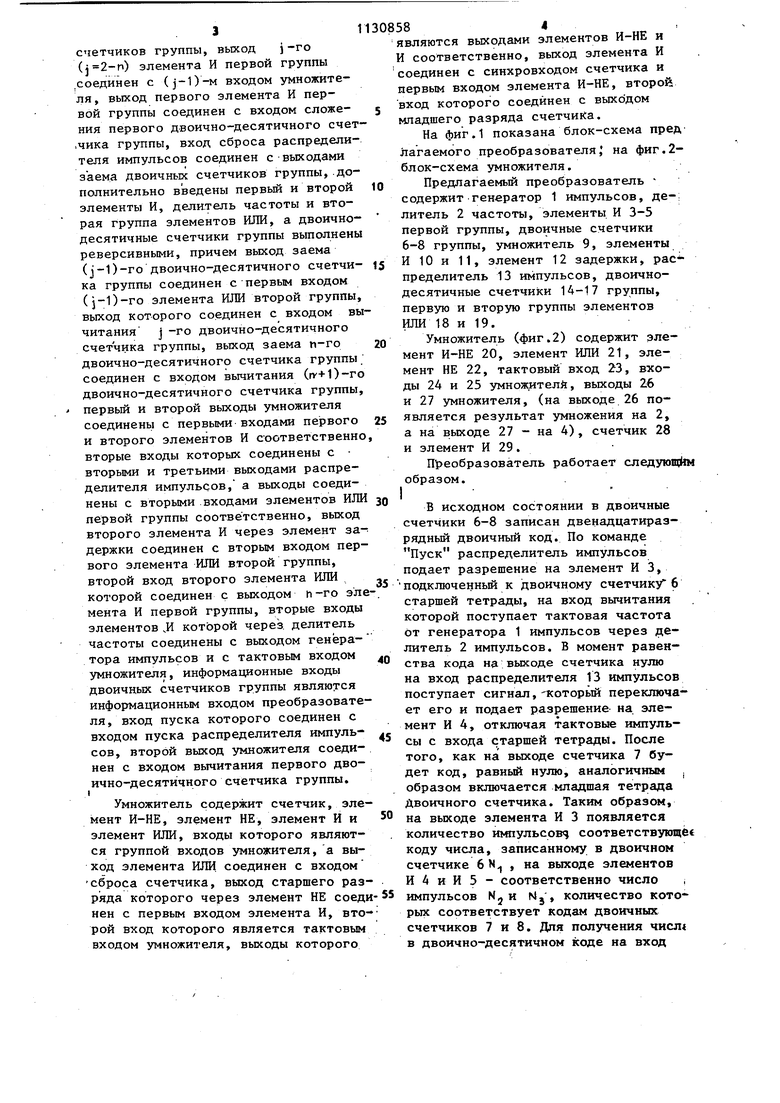

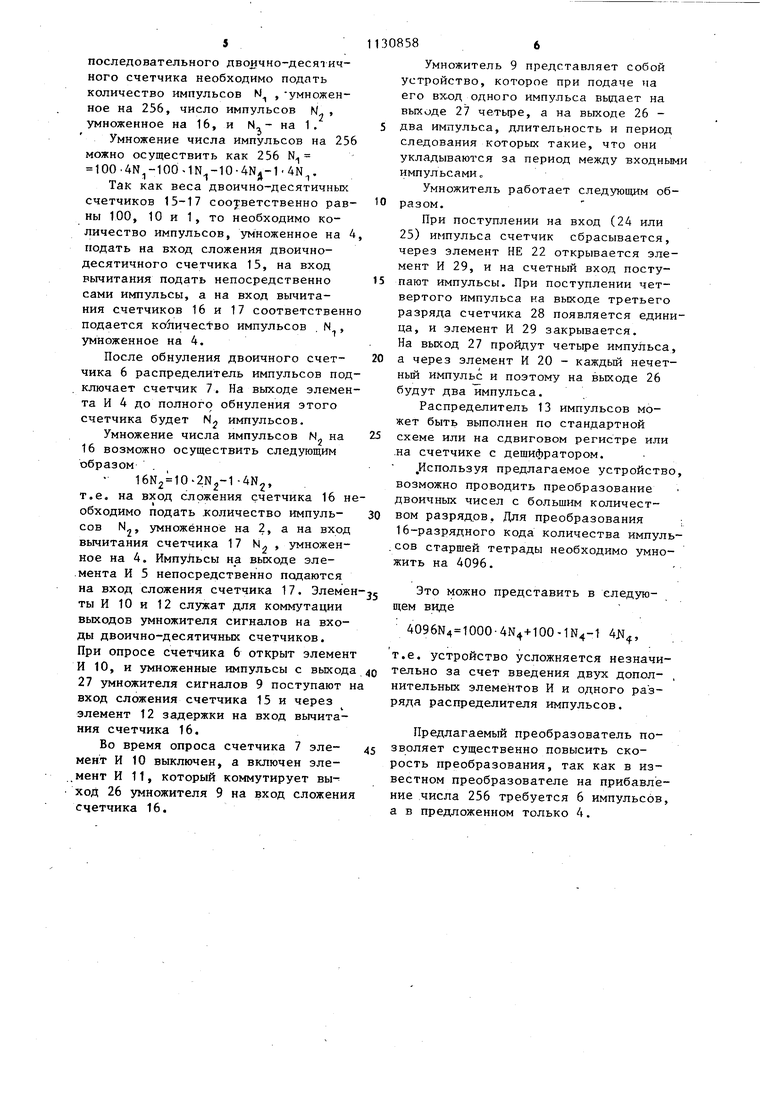

Изобретение относится к вычислительной технике и может быть использрвано при построении устройств для обработки дискретной информации. Известно устройство для преобразования двоичного кода в двоично-, десятичньй, содержащее двоичный и де сятичный счетчики, разбитые на секции, собирательные схемы перевода весовых значений граничных разрядов каждого двоичного кода в соответствующее весовое значение десятичного разряда, элементы И и элементы ИЛИ, дешифраторынуля двоичного счетчика C1 3, Однако этот преобразователь имеет большое время преобразования, :которое определяется временем последовательного преобразования младших разрядов. Наиболее близким к изобретению по технической сущности и схемному построению.является преобразователь двоичного кода в двоично-десятичный, содержащий последовательный десятичный декадньй счетчик, двоичные счетчики, распределитель импульсов, группу элементов И, группу элементов ИЛИ, умножитель, элемент за-держки, причем элементы ИЛИ ключены на входы старшей, средней и младшей декад двоично-десятичного счетчика, соответственно первые входы элементов И подключены к соответствующим выходам распределителя импульсов, а вторые входы элементов И подключе ны к генератору тактовых импуль сов 2;.Недостатком известного преобразователя является относительно низкое ; быстродействие, связанное с тем, что десятичный эквивалент граничных разрядов двоичного кода представляется только положительными числами. Цель изобретения - повьшение быстродействия. Поставленная цель достигается тем, что в.преобразователь двоичного кода в двоично-десятичный, с,одержащий группу двоичных счетчиков, первую группу элементов И, распредели-, тепь импульсов, генератор импульсов, первую группу элементов ИЛИ, элемент задержки, умножитель, группу двоично-десятичных счетчиков, разрядные выходы которых являются выходами преобразрвателя, выход переноса .i-ro двоично-десятичного счетчика гоуппы ((n-1), где (h+1)-го - число разрядов выходного кода, соединен с первым входом 1-го элемента ИЛИ первой группы, выход которого соединен с входом сложения (i+1)-ro двоично-десятичного счетчика группы,выход переноса п-го двоично-десятичного счетчика группы соединен с входом сложения (п+1)-го двоично-десятичного счетчика группы, выходы распределителя импульсов соединены с первыми входами соответствующих элементов И первой группы, выходы которых соединены со счетными входами соответствующих двоичных счетчиков группы, выход j-го () элемента И первой группы .соединен с (j-1)-M входом умножителя, выход первого элемента И первой группы соединен с входом сложения первого двоично-десятичного счет ,чика группы, вход сброса распределителя импульсов соединен с выходами заема двоичных счетчиков группы,.дополнительно введены первый и второй элементы И, делитель частоты и вторая группа элементов ИЛИ, а двоичнодесятичные счетчики группы выполнены реверсивными, причем выход заема (j-1)-го двоично-десятичного счетчика группы соединен с первым входом (j-1)-го элемента ИЛИ второй группы, выход которого соединен с входом вы читания j -го двоично-десятичного счетчика группы, выход заема п-го двоично-десятичного счетчика группы соединен с входом вычитания (гу+1)-го двоично-десятичного счетчика группы первый и второй выходы умножителя соединены с первыми входами первого и второго элементов И соответственно вторые входы которых соединены с вторыми и третьими выходами распределителя импульсов, а выходы соединены с вторыми .входами элементов ИЛИ первой группы соответственно, выход второго элемента И через элемент задержки соединен с вторым входом первого элемента ИЛИ второй группы, второй вход второго элемента ИЛИ которой соединен с выходом h-ro эл мента И первой группы, вторые входы элементов ,И которой через, делитель частоты соединены с выходом генератора импульсов и с тактовым входом умножителя, информационные входы двоичных счетчиков группы являются информационным входом преобразовате ля, вход пуска которого соединен с входом пуска распределителя импульсов, второй выход умножителя соединен с входом вычитания первого двоично-десятичного счетчика группы. Умножитель содержит счетчик, эле мент И-НЕ, элемент НЕ, элемент И и элемент ИЛИ, входы которого являются группой входов умножителя, а выход элемента ШШ соединен с входом Сброса счетчика, выход старшего раз ряда которого через элемент НЕ соед нен с первым входом элемента И, вто рой вход которого является тактовым входом умножителя, выходы которого 584 являются выходами элементов И-НЕ и И соответственно, выход элемента И соединен с синхровходом счетчика и первым входом элемента И-НЕ, второй вход которого соединен с выходом младшего разряда счетчиКа. На фиг.1 показана блок-схема пред лагаемого преобразователя, на фиг.2блок-схема умножителя. Предлагаемый преобразователь содержит-генератор 1 импульсов, де-; литель 2 частоты, элементы. И 3-5 первой группы, двоичные счетчики 6-8 группы, умножитель 9, элементы И 10 и 11, элемент 12 задержки, рас пределитель 13 импульсов, двоичнодесятичные счетчики 14-17 группы, первую и вторую группы элементов ИЛИ 18 и 19. Умножитель (фиг.2) содержит элемент И-НЕ 20, элемент ИЛИ 21, элемент НЕ 22, тактовый вход 23, входы 24 и 25 умножители, выходы 26 и 27 умножителя, (на выходе 26 появляется результат умножения на 2, а на выходе 27 - на 4), счетчик 28 и элемент И 29. Преобразователь работает следующим образом. В исходном состоянии в двоичные счетчики 6-8 записан двенадцатираз- рядный двоичный код. По команде Пуск распределитель импульсов подает разрешение на элемент ИЗ, подключенный к двоичному счетчику 6 старшей тетрады, на вход вычитания которой поступает тактовая частота от генератора 1 импульсов через делитель 2 импульсов. В момент равенства кода навыходе счетчика нулю на вход распределителя 13 импульсов поступает сигнал,-который переключает его и подает разрешение на элемент И 4, отключая тактовые импульсы с входа старшей тетрады. После того, как на выходе счетчика 7 будет код, равный нулю, аналогичным . образом включается младшая тетрада Двоичного счетчика. Таким образом, на выходе элемента И 3 появляется количество иштульсрв соответствующе коду числа, записанному в двоичном счетчике 6 N , на выходе элементов И 4 и И 5 - соответственно число импульсов количество которых соответствует кодам двоичных счетчиков 7 и 8. Для получения числ в двоично-десятичном коде на вход последовательного двоично-деся1ичного счетчика необходимо подать количество импульсов И , -умноженное на 256, число импульсов N , умноженное на 16, и N,- на 1. Умножение числа импульсов на 25 можно осуществить как 256 N 100..1N -10-4N -1 ,.,, Так как веса двоично-десятичных счетчиков 15-17 соответственно рав ны 100, 10 и 1, то необходимо количество импульсов, умноженное на подать на вход сложения двоичнодесятичного счетчика 15, на вход вычитания подать непосредственно сами импульсы, а на вход вычитания счетчиков 16 и 17 соответственн подается Ko}iH4ec,tBo импульсов . N , умноженное на 4. После обнуления двоичного счетчика 6 распределитель импульсов под ключает счетчик 7. На выходе элемен та И 4 до полного обнуления этого счетчика будет Nj импульсов. Умножение числа импульсов N на 16 возможно осуществить следующим образом . 16N2 10-2N2-1-4N2, т.е. на вход сложения счетчика 16 н обходимо подать .количество импульсов N, умноженное на 2, а на вход вычитания счетчика 17 Мл , умноженное на 4. ИмпуЛьсы выходе эле.мента И 5 непосредственно подаются на вход сложения счетчика 17. Элеме ты И 10 и 12 слзгжат для коммутации выходов умножителя сигналов на входы двоично-десятичных счетчиков. При опросе счетчика 6 открыт элемен И 10, и умноженные импульсы с выход 27 умножителя сигналов 9 поступают вход сложения счетчика 15 и через элемент 12 задержки на вход вычитания счетчика 16. Во время опроса счетчика 7 элемент И 10 выключен, а включен эле.мент И 11, который коммутирует выход 26 умножителя 9 на вход сложени счетчика 16. Умножитель 9 представляет собой устройство, которое при подаче ча его ВХ.ОД одного импульса ньдает на выходе 27 четыре, а на выходе 26 два импульса, длительность и период следования которых такие, что они укладываются за период между входными импульсами о Умножитель работает следующим образом. При поступлении на вход (24 или 25) импульса счетчик сбрасывается, через элемент НЕ 22 открывается элемент И 29, и на счетный вход поступают импульсы. При поступлении четвертого импульса ка выходе третьего разряда счетчика 28 появляется единица, и элемент И 29 закрывается. На вьсход 27 пройдут четыре импульса, а через элемент И 20 - каждый нечетный импульс и поэтому на выходе 26 будут два импульса. Распределитель 13 импульсов может быть выполнен по стандартной схеме или на сдвиговом регистре или .на счетчике с дешифратором. .Используя предлагаемое устройство, возможно проводить преобразование двоичных чисел с большим количеством разрядов, Для преобразования 16-разрядного кода количества импульсов старшей тетрады необходимо умножить на 4096. Это можно представить в следзтав;ем виде 4096N4 1000-4N4 + 100-1N4-t i, т.е. устройство усложняется незначительно за счет введения двух допол- , нительных элементов И и одного разряда распределителя импульсов. Предлагаемый преобразователь позволяет существенно повысить скорость преобразования, так как в известном преобразователе на прибавление числа 256 требуется 6 импульсов, а в предложенном только 4.

Входнейг од

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для преобразования кодов | 1973 |

|

SU468236A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Патент ФРГ № 1269655, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| ПРИБОР ДЛЯ ЗАПИСИ И ВОСПРОИЗВЕДЕНИЯ ЗВУКОВ | 1923 |

|

SU1974A1 |

Авторы

Даты

1984-12-23—Публикация

1983-07-26—Подача