1

Изобретение относится к вычислительной технике и, в частности, к организации диагностического контроля при неустойчивых отказах.

Известны устройства для диагностического контроля нроцессора, содержащие блок оиераций, блок управления, блок сопряжения, блок прерывания, блок контроля, блок повторения микрокоманд, регистр отказов, диагностический блок.

Недостатком известных устройств для диагностического контроля процессора являются трудности диагностирования неустойчивых отказов.

Целью изобретения является сокращение оборудования путем локализации области неустойчивых отказов.

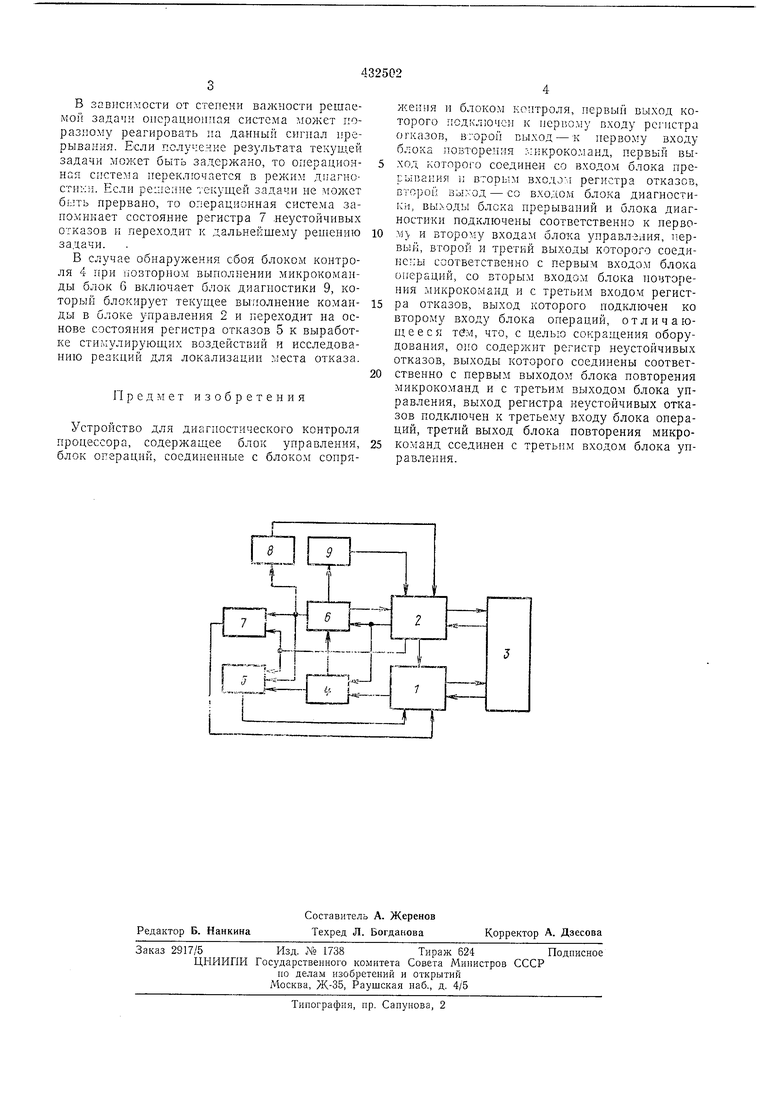

Сущность изобретения заключается в том, что в устройство введен регистр неустойчивых отказов, выходы которого соединены соогветственно с первым выходом блока повторения микрокоманд и с третьим выходом блока управления; выход регистра неустойчивых отказов подключен к третьему входу блока операций, третий выход блока повторения микрокоманд соединен с третьим входом блока управления.

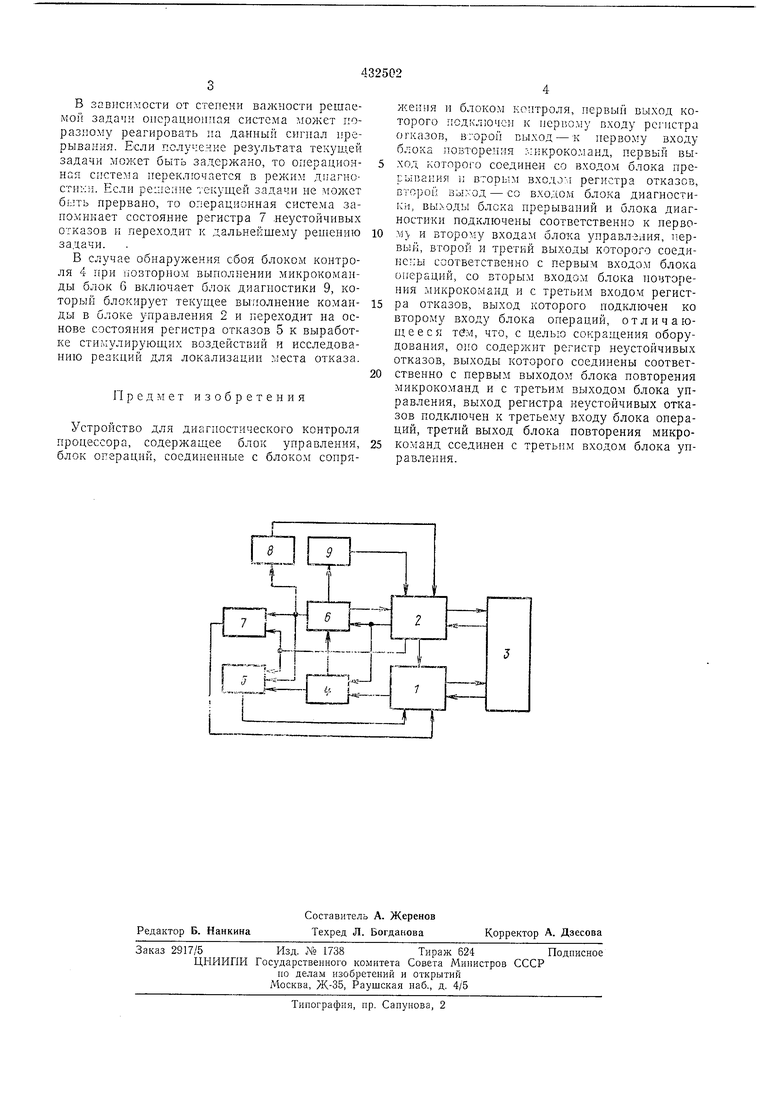

На чертеже представлена схема предлагаемого устройства: блок операций 1, блок управления 2, блок сопряжения 3, блок контроля 4, регистр отказов 5, блок 6 повторения микрокоманд, регистр 7 неустойчивых отказов, блок прерывания 8, блок диагностики 9.

Обработка информации производится в блоке операций 1 процессора под управлением блока управления 2. Связь с оперативной памятью и внешними устройствами производится с помощью блока сопряжения 3.

Функционирование блока 1 и блока управления 2 проверяется блоком контроля 4. который при наличии сбоев фиксирует их в регистре отказов 5, каждый разряд которого запоминает определенный вид сбоя.

При фиксации сбоя блок контроля 4 запускает блок 6 повторения микрокоманд, I;OTOрый запускает в блоке управления 2 повторное выполнение микрокоманды, в которой был обнаружен сбой. Если при иовторном выиолнении микрокоманды блок контроля 4 не обнаруживает сбоя, то блок б передает содержимое регистра отказов 5 в регистр 7 неустойчивых отказов, гасит регистр отказов 5 и возбуждает блок прерывания 8.

При этом блок управленпя 2 продолжает нормальное выполнение команды. Блок прерывания 8 после окончания выполнения текущей команды прерывает нормальную последовательность, сообщая операционной системе о наличии неустойчивого отказа. В зависимости от степени ва кности решаемой задачи операционная система .южет иоразкому реагировать иа данный сигнал прерывания. Если получение результата текущей задачи может быть задержано, то оиерационнал система переключается в режим дпагности:-;:5. Если решение текущей задачи не может быть прервано, то олерационная система запоминает состояние регистра 7 неустойчивых отказов и переходит к дальнейшему реншнию за,цачи. В случае обнаружения сбоя блоком контроля 4 при повторном выполнении микрокоманды блок 6 включает блок диагностики 9, который блокирует текущее выполнение команды Б блоке управления 2 и переходит на основе состояния регистра отказов 5 к выработке стимулирующих воздействий и исследованию реакций для локализации места отказа. Предмет изобретения Устройство для диагностического контроля процессора, содерл :ащее блок управления, блок операций, соединенные с блоком сонряжения и блоком контроля, первый выход которого подключен к первому входу peincTpa отказов, вгорой выход-к первому входу блока повторения микрокоманд, первый выход которого соединен со входо.м блока прерывания 1 вторым входом регистра отказов, BTopoLi выход - со вхо,цом блока диагностики, выходы блока прерываний и блока диагностики подключены соответственно к нервом и второму входам блока управления, первый, второй и третий выходы которого соединены соответственно с первым входом блока операций, со вторым входом блока повторения микрокоманд и с третьим входом регистра отказов, выход которого подключен ко второму входу блока операций, отличающееся тем, что, с целью сокращения оборудования, оно содержит регистр неустойчивых отказов, выходы которого соединены соответственно с первым выходом блока повторения микрокоманд и с третьим выходом блока управления, выход регистра неустойчивых отказов подключен к третьему входу блока операций, третий выход блока повторения микрокоманд соединен с третьим входом блока управления.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для управления каналами связи вычислительной системы | 1975 |

|

SU525095A1 |

| Устройство для контроля и восстановления вычислительного процесса | 1988 |

|

SU1605233A1 |

| Двухканальное устройство для контроля и восстановления процессорных систем | 1986 |

|

SU1397917A1 |

| Устройство для восстановления работы процессора | 1987 |

|

SU1476467A2 |

| Внешнее устройство управления | 1978 |

|

SU736100A1 |

| Устройство для сопряжения оперативной памяти с внешними устройствами | 1981 |

|

SU993237A1 |

| Устройство для восстановления процессора после сбоя | 1979 |

|

SU857999A1 |

| Устройство для восстановления работы процессора | 1984 |

|

SU1191910A1 |

| Процессор | 1984 |

|

SU1246108A1 |

| Устройство для восстановления информации цифровых вычислительных машин | 1982 |

|

SU1027728A1 |

Авторы

Даты

1974-06-15—Публикация

1972-03-29—Подача