1

Изобретение относится к области электронной вычислительной техники.

Известно оперативное запоминающее устройство (ОЗУ) с компенсацией разрушающих магнитных полей тока считывания, содержащее накопитель и многоступенчатый дещифратор.

При построении такого ОЗУ каждый запоминающий элемент (ЗЭ) в накопителе образуется на пересечении двух щин: числовой щины и разрядной щины. Числовые шины прокладываются параллельно направлению оси легкого намагничивания пленки, разрядные щины - перпендикулярно числовым щипам. Каждая числовая шина объединяет ЗЭ, принадлежащее одному числу, а разрядная шина - ЗЭ, принадлежащие одному разряду. Числовые щины, расположенные конструктивно рядом, подключены к выходам дешифратора инверсно (т. е. подключены начала четных щин и концы нечетных). Каждый выход дещифратора соединен с соседним через резистор, а последовательно с числовой щиной включен другой резистор. В режиме считывания в соответствующую числовую щину поступает импульс тока считывания. По рядом расположенным числовым шинам протекают компенсирующие токи, которые обеспечивают компенсацию разрущающих магнитных полей импульса тока считывания.

Наличие больщого количества дополнительных элементов (по два резистора на каждую числовую щину) и паек и необходимость дополнительного рассеяния мощности транзистором последней ступени дешифратора усложняют устройство, так как через транзистор кроме тока считывания протекают компенсирующие токи. С целью упрощения устройства выходы дещифратора предпоследней ступени соединены с соседними выходами через соответствующие резисторы и с соответствующими входами дешифратора последней ступени - через последовательно соединенные резисторы и диоды.

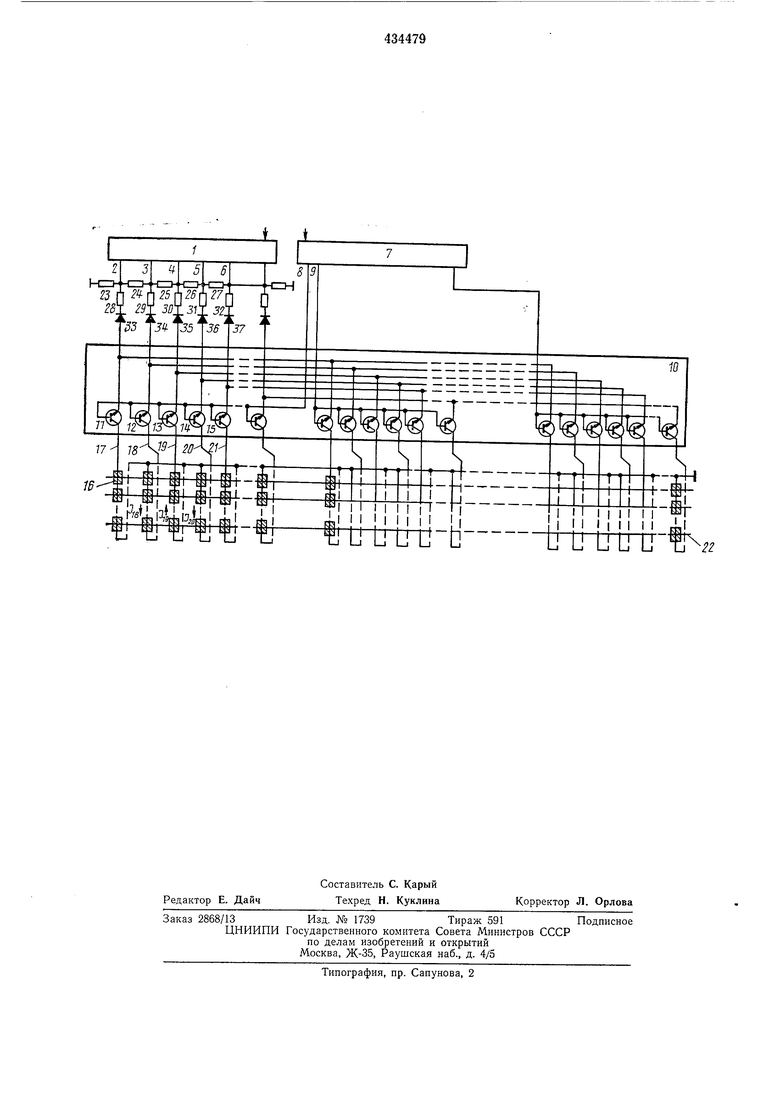

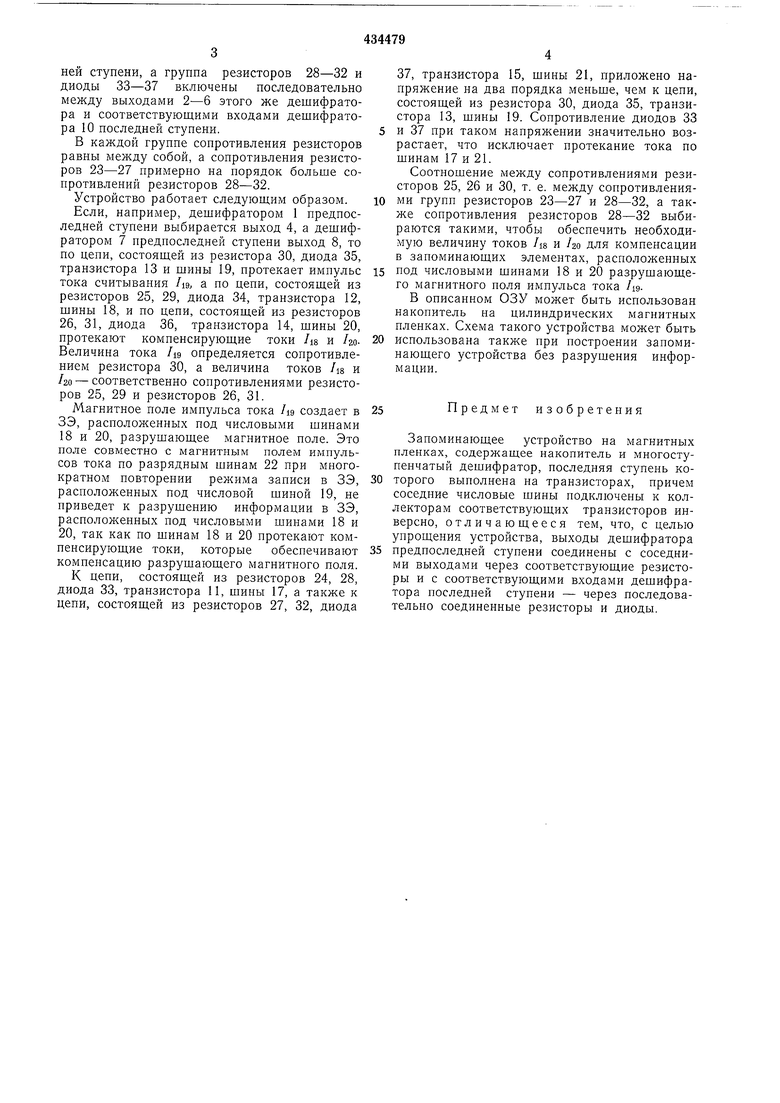

На чертеже представлена схема устройства. Оно состоит из дещифратора 1 предпоследней ступени с выходами 2-6, дешифратора 7 предпоследней ступени с выходами 8, 9 и дешифратора 10 последней ступени на транзисторах 11 -15, а также накопителя с ЗЭ 16 на плоских магнитных пленках. Накопитель имеет систему числовых шин 17-21 и систему разрядных шин 22. Устройство также содержит две группы резисторов 23-27 и 28-32

и диоды 33-37.

Числовые шины 17-21, расположенные конструктивно рядом, подключены к коллекторам соответствующих транзисторов 11 -15 инверсно. Группа резисторов 23-27 включена между выходами 2-6 дешифратора 1 предпоследней ступени, а группа резисторов 28-32 и диоды 33-37 включены последовательно между выходами 2-6 этого же дешифратора и соответствующими входами дешифратора 10 последней ступени.

В каждой группе сопротивления резисторов равны между собой, а сопротивления резисторов 23-27 примерно на порядок больше сопротивлений резисторов 28-32.

Устройство работает следуюш;им образом.

Если, например, дешифратором 1 предпоследней ступени выбирается выход 4, а дешифратором 7 предпоследней ступени выход 8, то по цепи, состояш,ей из резистора 30, диода 35, транзистора 13 и шины 19, протекает импульс тока считывания Iig, а по цепи, состоящей из резисторов 25, 29, диода 34, транзистора 12, шины 18, и по цепи, состоящей из резисторов 26, 31, диода 36, транзистора 14, шины 20, протекают компенсирующие токи /le и /гоВеличина тока /19 определяется сопротивлением резистора 30, а величина токов /is и /20 - соответственно сопротивлениями резисторов 25, 29 и резисторов 26, 31.

Магнитное поле импульса тока /ig создает в ЗЭ, расположенных под числовыми шинами 18 и 20, разрушающее магнитное поле. Это поле совместно с магнитным полем импульсов тока по разрядным шинам 22 при многократном повторении режима записи в ЗЭ, расположенных под числовой шиной 19, не приведет к разрушению информации в ЗЭ, расположенных под числовыми шинами 18 и 20, так как по шинам 18 и 20 протекают компенсирующие токи, которые обеспечивают компенсацию разрушающего магнитного поля.

К цепи, состоящей из резисторов 24, 28, диода 33, транзистора 11, шины 17, а также к цепи, состоящей из резисторов 27, 32, диода

37, транзистора 15, щины 21, приложено напряжение на два порядка меньше, чем к цепи, состоящей из резистора 30, диода 35, транзистора 13, щииы 19. Сопротивление диодов 33

и 37 при таком напряжепии значительно возрастает, что исключает протекание тока по шинам 17 и 21.

Соотношение между сопротивлениями резисторов 25, 26 и 30, т. е. между сопротивлениями групп резисторов 23-27 и 28-32, а также сопротивления резисторов 28-32 выбираются такими, чтобы обеспечить необходимую величину токов Дв и /2о для компенсации в запоминающих элементах, расположенных

под числовыми шипами 18 и 20 разрушающего магнитного поля импульса тока /19.

В описанном ОЗУ может быть использован накопитель на цилиндрических магнитных пленках. Схема такого устройства может быть

использована также при построении запоминаюшего устройства без разрушения информации.

Предмет изобретения

Запоминающее устройство на магнитных пленках, содержащее накопитель и многоступенчатый дешифратор, последняя ступень которого выполнена на транзисторах, причем соседпие числовые шины подключены к коллекторам соответствующих транзисторов инверсно, отличающееся тем, что, с целью упрощения устройства, выходы дещифратора

предпоследней ступени соединены с соседними выходами через соответствующие резисторы и с соответствующими входами дешифратора последней ступени - через последовательно соединенные резисторы и диоды.

| название | год | авторы | номер документа |

|---|---|---|---|

| ОПЕРАТИВНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С ЧИСЛОВОЙ ВЫБОРКОЙ | 1972 |

|

SU424232A1 |

| Запоминающее устройство | 1976 |

|

SU597006A1 |

| ЬИЬЛИО', ЕКА | 1973 |

|

SU365707A1 |

| ПЬЕЗОТРАНСФОРМАТОРНОЕ ЗАПОЛИШАЮЩЕЕ УСТРОЙМТ?|11е0-1ЕЛКГ1:: | 1972 |

|

SU331421A1 |

| Запоминающее устройство | 1976 |

|

SU690564A1 |

| Постоянное запоминающее устройство | 1982 |

|

SU1112411A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1972 |

|

SU344506A1 |

| Трансформаторное постоянное запо-МиНАющЕЕ уСТРОйСТВО | 1979 |

|

SU841048A1 |

| Постоянное запоминающее устройство | 1977 |

|

SU637870A1 |

| Оперативное запоминающее устройство | 1983 |

|

SU1101890A1 |

Даты

1974-06-30—Публикация

1972-07-31—Подача