Известно запоминающее устройство, содержащее элементы памяти, размещенные в перекрестиях адресных и разрядных шин, подключенных соответственно к дешифратору адреса и усилителям считывания, входные резисторы которых подсоединены к общей щине.

В таком устройстве малое отношение минимального сигнала «1 к максимальному сигналу «О при одинаковой полярности Считанных сигналов «1 и «О усложняет схему усилителей считывания и приводит к ненадежной работе запоминающего устройства.

Предложенное запоми.нающее устройство отличается от известного тем, что его адресные шины через диоды соединены с общей щиной.

Это позволяет повысить надежность работы устройства.

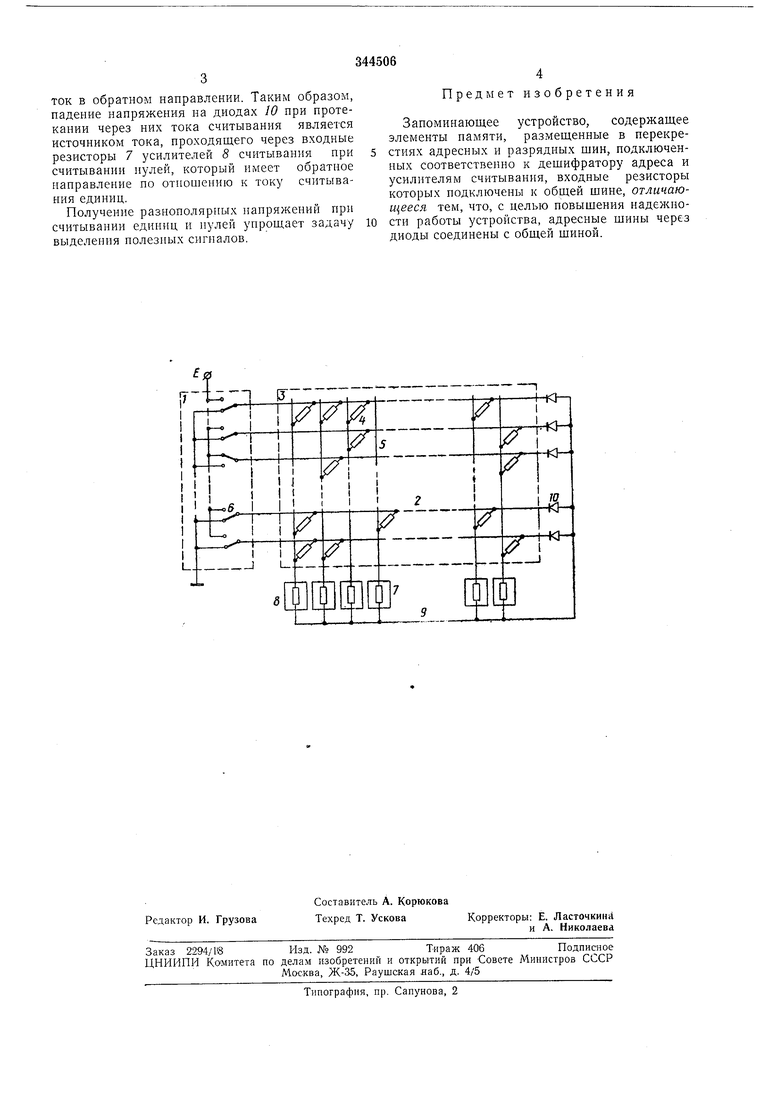

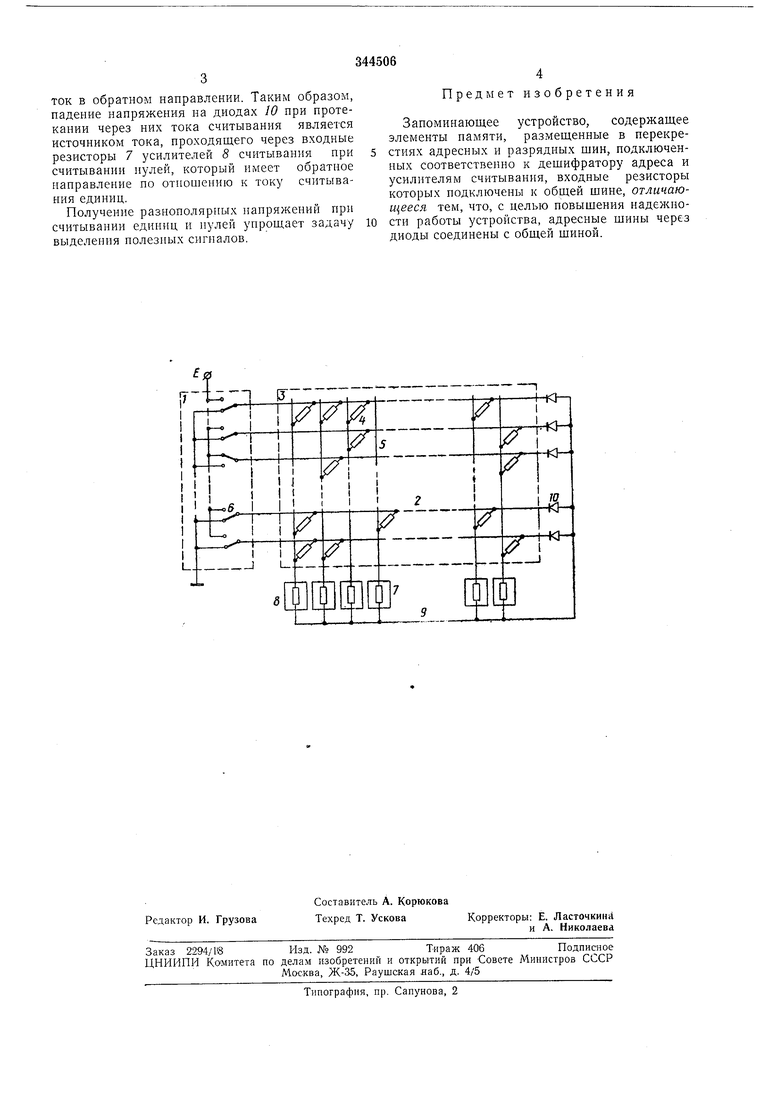

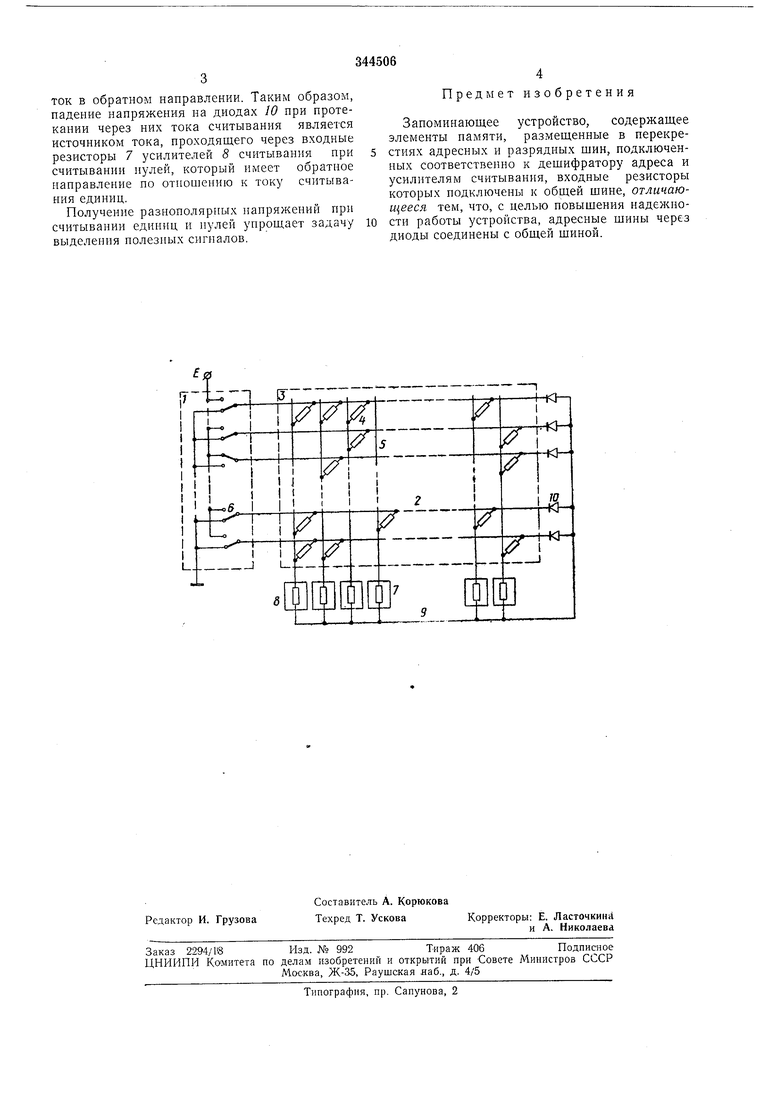

На чертеже показана схема запоминающего устройства.

Выходы дешифратора / адреса подключены к адресным щинам 2 матрицы 3 элементов 4 памяти. В качестве элементов памяти использованы резисторы, размещенные в перекрестиях адресных 2 и разрядных 5 шин при записи единиц. Переключатели 6 дещифратора адреса соединяют соответствующею адресную шину 2 с источником питания Е при считывании информации или с корпусом устройства. В любой момент времени считывание проводится только с одной адресной шины 2. Входные резисторы 7 усилителей 8 считывания соединены с общей щиной 9, а она через диоды 10 - с адресными щинами 2.

Принцип действия запоминающего ус1ройства состоит в следующем. Если выбранная адресная щина 2 соединена с определенной

разрядной шиной 5 через элемент 4 памяти, то ток считывания из адресной шины 2 проходит в разрядную шину 5, протекает через входной резистор 7 усилителя 8 считывания, создавая падение напряжения U, являющееся

сигналом единицы, и через диоды 10, невыбранные адресные шины 2 и переключатели 6 замыкается на корпус устройства. При использовании в качестве переключателей транзисторов на них возникает остаточное напряжение UOCT, мало зависящее от протекающего через транзистор тока. Таким образом, все невыбранные адресные щины 2 находятся под одним потенциалом /7остОбщая щина 9 имеет потенциал более высокий, чем Uocf за счет падения напряжения на прямом сопротивлении диодов 10 при протекапии через них тока считывания. Поэтому через входные резисторы 7 усилителей 8 считывания, разрядные шины 5 которых не соеток в обратном направлении. Таким образом, падение напряжения на диодах 10 при протекании через них тока считывания является источником тока, проходящего через входные резисторы 7 усилителей 8 считывания при считывании нулей, который имеет обратное направление по отношению к току считывания единиц.

Получение разнополярных напряжений при считывании единиц и нулей унронщает задачу выделения нолезных сигналов.

Предмет изобретения

Запоминающее устройство, содержащее элементы памяти, размещенные в перекрестиях адресных и разрядных шин, подключенных соответственно к дешифратору адреса и усилителям считывания, входные резисторы которых подключены к общей шине, отличающееся тем, что, с целью повышения надежности работы устройства, адресные щины через диоды соединены с общей шиной.

| название | год | авторы | номер документа |

|---|---|---|---|

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1973 |

|

SU385314A1 |

| Матрица для накопителя полупостоянного запоминающего устройства | 1976 |

|

SU595793A1 |

| Полупостоянное запоминающее устройство с электрической перезаписью информации | 1983 |

|

SU1088068A1 |

| Постоянное запоминающее устройство | 1982 |

|

SU1112411A1 |

| Оперативное запоминающее устройство | 1988 |

|

SU1575234A1 |

| Запоминающее устройство | 1976 |

|

SU690564A1 |

| Запоминающее устройство | 1968 |

|

SU842961A1 |

| ПЬЕЗОТРАНСФОРМАТОРНОЕ ЗАПОЛИШАЮЩЕЕ УСТРОЙМТ?|11е0-1ЕЛКГ1:: | 1972 |

|

SU331421A1 |

| Запоминающее устройство | 1976 |

|

SU597006A1 |

| Полупроводниковое запоминающее устройство | 1973 |

|

SU654197A3 |

Авторы

Даты

1972-01-01—Публикация