1

Изобретение относится к области запоминающих устройств (ЗУ).

Известно устройство для контроля ферритовых матриц запоминающих устройств, содержащие блок управления, регистр адреса, управляющий дешифратором адреса, коммутирующим импульсы тока, вырабатываемые блоком генераторов тока с дискретно управляемой ам:плитудой, блоки считывания и контроля. Для управления ам плитудой тока известное устройство имеет несколько блоков коммутаторов. Число блоков равно числу изменяемых координатных токов (например, в ЗУ системы 2,БД это число равно двум).

Каждый коммутатор блока управляет определенной амплитудой тока. Оператор может вручную установить любую амплитуду тока в определенных пределах с установленной дискретностью. При проверке матриц оператор устанавливает заданную амплитуду одного координатного тока и, устанавливая заданные значения (мияимальное и максимальное) амплитуды другого координатного тока, определяет соответствие области хранения информации матрицы заданной, а потом, аналогично установив заданную амплитуду второго координатного тока, изменяет амплитуду первого координатного тока. Таки-м образом, при проверке матрицы оператор вынужден вручную менять положение коммутаторов, устанавливая по существу несколько заданных амплитуд токов.

Это существенно снижает скорость работы устройст1ва.

Описываемое устройство отличается от известного тем, что оно содержит дополнительные дешифраторы и дополнительные коммутаторы по числу блоков коммутаторов, схему блокировки и счетчик. Вход и один из выходов последнего подключены к блоку управления, другие выходы - к первым входам соответствующих дополнительных дешифраторов, вторые входы которых подсоединены к выходам дополнительных коммутаторов, третьи - к блоку управления, а выходы - ко входам соответствующих блоков коммутаторов. Вход схемы блокировки соединен со входом счетчика и с одни-м из выходов блока управления, а выход-с одним из входов блока

управления.

Это позволяет устанавливать необходимые амплитуды токов как вручную, так и автоматически, что существенно повышает быстродействие устройства.

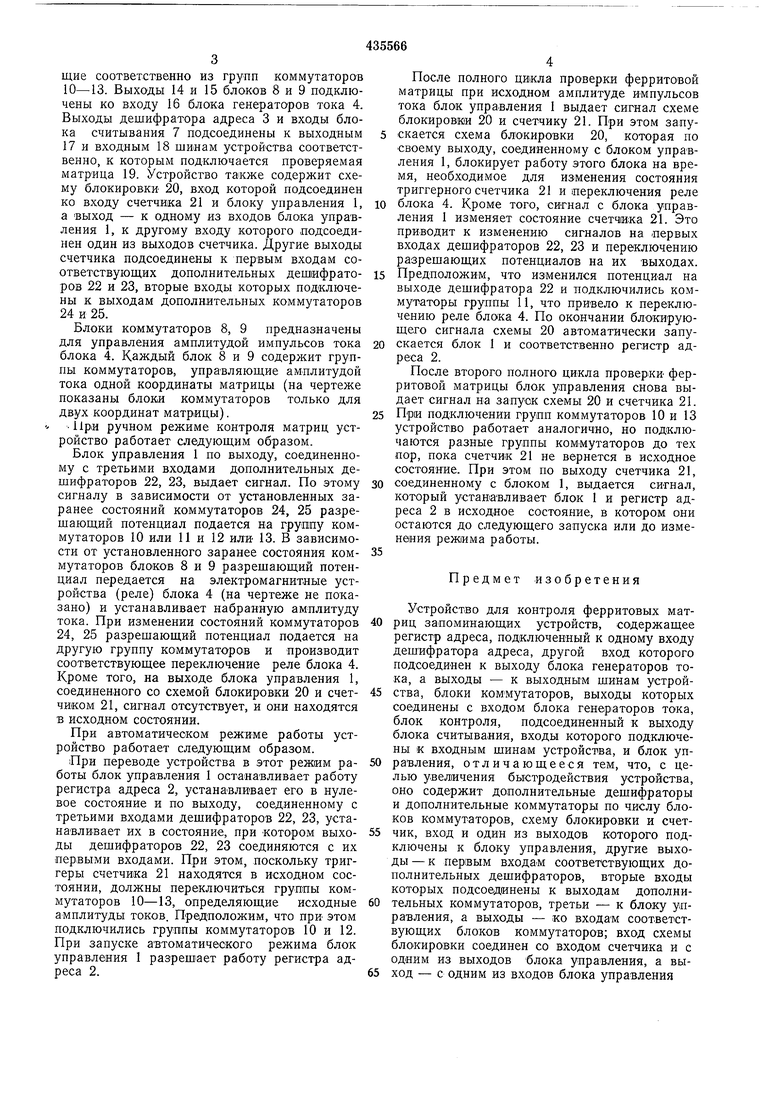

Схема устройства изображена на чертеже.

Устройство содержит блок управления 1, регистр адреса 2, дешифратор адреса 3, блок генераторов импульсов тока 4, блок контроля 5, вход 6 которого подключен к блоку считывания 7, блоки коммутаторов 8 и 9, состоящие соответственно из групп коммутаторов 10-13. Выходы 14 и 15 блоков 8 и 9 подключены ко входу 16 блока генераторов тока 4. Выходы дешифратора адреса 3 и входы блока считывания 7 подсоединены к выходным 17 и входным 18 шинам устройства соответственно, к которым подключается проверяемая матрица 19. Устройство также содержит схему блокировки 20, вход которой подсоединен ко входу счетчика 21 и блоку управления 1, а ВЫХОД - к одному из входов блока управления 1, к другому входу которого подсоединен один из выходов счетчика. Другие выходы счетчика подсоединены к первым входам соответствующих дополнительных дешифраторов 22 и 23, вторые входы которых подключены к выходам дополнительных коммутаторов 24 и 25.

Блоки коммутаторов 8, 9 предназначены для управления амплитудой импульсов тока блока 4. Каждый блок 8 и 9 содержит группы коммутаторов, упра-вляюшие амплитудой тока одной координаты матрицы (на чертеже показаны блоки коммутаторов только для двух координат матрицы).

При ручном режиме контроля матриц устройство работает следующим образом.

Блок управления 1 по выходу, соединенному с третьими входами дополнительных дешифраторов 22, 23, выдает сигнал. По этому сигналу в зависимости от установленных заранее состояний коммутаторов 24, 25 разрешающий потенциал подается на группу коммутаторов 10 или 11 и 12 ИЛИ 13. В зависимости от установленного заранее состояния коммутаторов блоков 8 и 9 разрешающий потенциал передается на электромагнитные устройства (реле) блока 4 (на чертеже не показано) и устанавливает набранную амплитуду тока. При изменении состояний коммутаторов 24, 25 разрешающий потенциал подается на другую группу коммутаторов и производит соответствующее переключение реле блока 4. Кроме того, на выходе блока управления 1, соединенного со схемой блокировки 20 и счетчиком 21, сигнал отсутствует, и они находятся в исходном состоянии.

При автоматическом режиме работы устройство работает следующим образом.

При переводе устройства в этот режим работы блок управления 1 останавливает работу регистра адреса 2, устанавливает его в нулевое состояние и по выходу, соединенному с третьими входами дешифраторов 22, 23, устанавливает их в состояние, при котором выходы дешифраторов 22, 23 соединяются с их первыми входами. При этом, поскольку триггеры счетчика 21 находятся в исходном состоянии, должны переключиться группы коммутаторов 10-13, определяющие исходные амплитуды токов. Предположим, что при этом подключились группы коммутаторов 10 и 12. При запуске автоматического режима блок управления 1 разрешает работу регистра адреса 2.

После полного цикла проверки ферритовой матрицы при исходном амплитуде импульсов тока блок управления 1 выдает сигнал схеме блокировки 20 и счетчику 21. При этом запускается схема блокировки 20, которая по своему выходу, соединенному с блоком управления 1, блокирует работу этого блока на время, необходимое для изменения состояния триггерного счетчика 21 и переключения реле

блока 4. Кроме того, сигнал с блока управления 1 изменяет состояние счетчика 21. Это приводит к изменению сигналов на первых входах дешифраторов 22, 23 и переключению разрешающих потенциалов на их выходах.

Предположим, что изменился потенциал на выходе дешифратора 22 и подключились коммутаторы группы 11, что привело к переключению реле блока 4. По окончании блокирующего сигнала схемы 20 автоматически запускается блок 1 и соответственно регистр адреса 2.

После второго полного цикла проверки ферритовой матрицы блок управления снова выдает сигнал на запуск схемы 20 и счетчика 21.

При подключении групп коммутаторов 10 и 13 устройство работает аналогично, но подключаются разные группы коммутаторов до тех пор, пока счетчик 21 не вернется в исходное состояние. При этом по выходу счетчика 21,

соединенному с блоком 1, выдается сигнал, который устанавливает блок 1 и регистр адреса 2 в исходное состояние, в котором они остаются до следующего запуска или до изменения реж1има работы.

Предмет изобретения

Устройство для контроля ферритовых матриц запоминающих устройств, содержащее регистр адреса, подключенный к одному входу дешифратора адреса, другой вход которого подсоединен к выходу блока генераторов тока, а выходы - к выходным шинам устройства, блоки коммутаторов, выходы которых соединены с входом блока генер аторов тока, блок контроля, подсоединенный к выходу блока считывания, входы которого подключены к входным шинам устройства, и блок управления, отличающееся тем, что, с целью увеличения быстродействия устройства, оно содержит дополнительные дешифраторы и дополнительные коммутаторы по числу блоков коммутаторов, схему блокировки и счетчик, вход и один из выходов которого подключены к блоку управления, другие выходы - к первым входам соответствующих дополнительных дешифраторов, вторые входы которых подсоединены к выходам дополнительных коммутаторов, третьи - к блоку управления, а выходы - ко входам соответствующих блоков коммутаторов; вход схемы блокировки соединен со входом счетчика и с одним из выходов блока управления, а выход - с одним из входов блока управления

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля запоминающих матриц | 1979 |

|

SU875468A1 |

| Устройство для контроля ферритовых сердечников запоминающих матриц | 1984 |

|

SU1280460A1 |

| Устройство для контроля параметров ферритовых сердечников запоминающей матрицы | 1984 |

|

SU1200346A1 |

| Устройство для контроля параметров ферритовых сердечников запоминающей матрицы | 1981 |

|

SU963110A1 |

| Устройство для контроля матриц на ферритовых сердечниках | 1977 |

|

SU622177A1 |

| Устройство для контроля матриц на ферритовых сердечниках | 1977 |

|

SU658601A1 |

| Устройство для считывания графической информации | 1981 |

|

SU983731A1 |

| Устройсто для проверки ферритовых матриц | 1974 |

|

SU548893A1 |

| Устройство для поиска минимального значения интенсивности размещения в тороидальных системах при направленной передаче информации | 2016 |

|

RU2628329C1 |

| Программное временное устройство | 1990 |

|

SU1762298A1 |

Даты

1974-07-05—Публикация

1972-08-22—Подача