Изобретение относится к ЕЫЧИСЛИ- тельной технике и может быть использовано для контроля ферритовых запоминающих устройств в процессе их производства.

Целью изобрет ния является повышение быстродействия устройства,

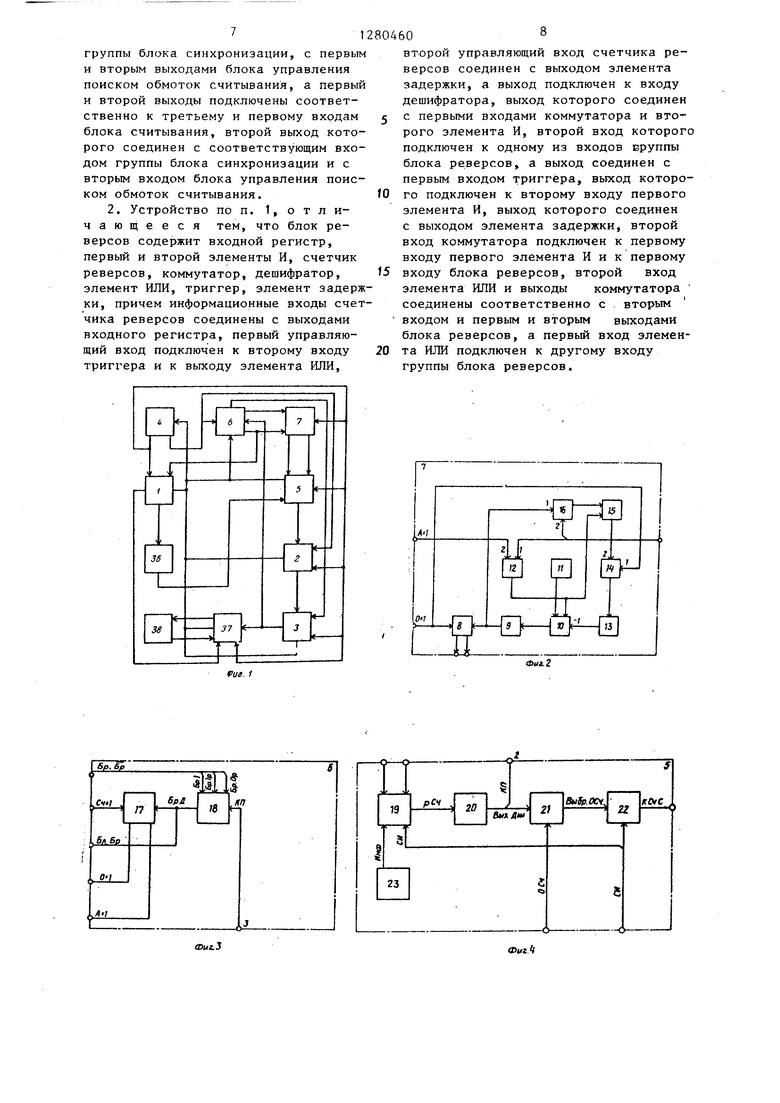

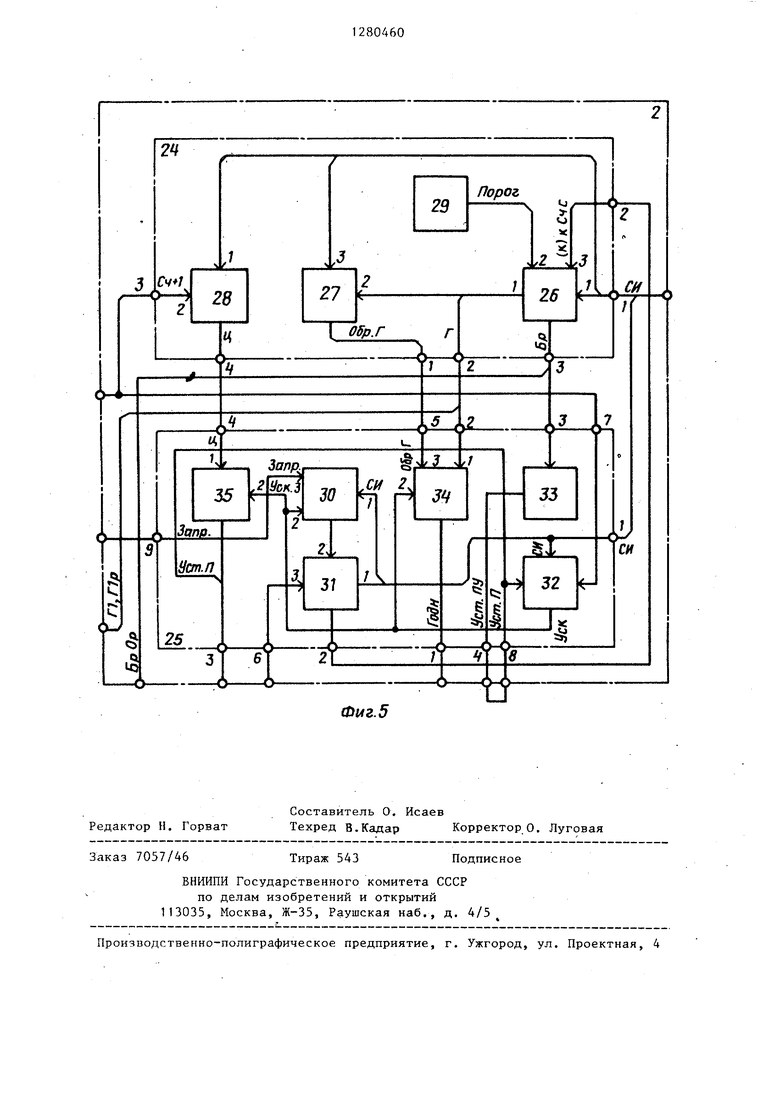

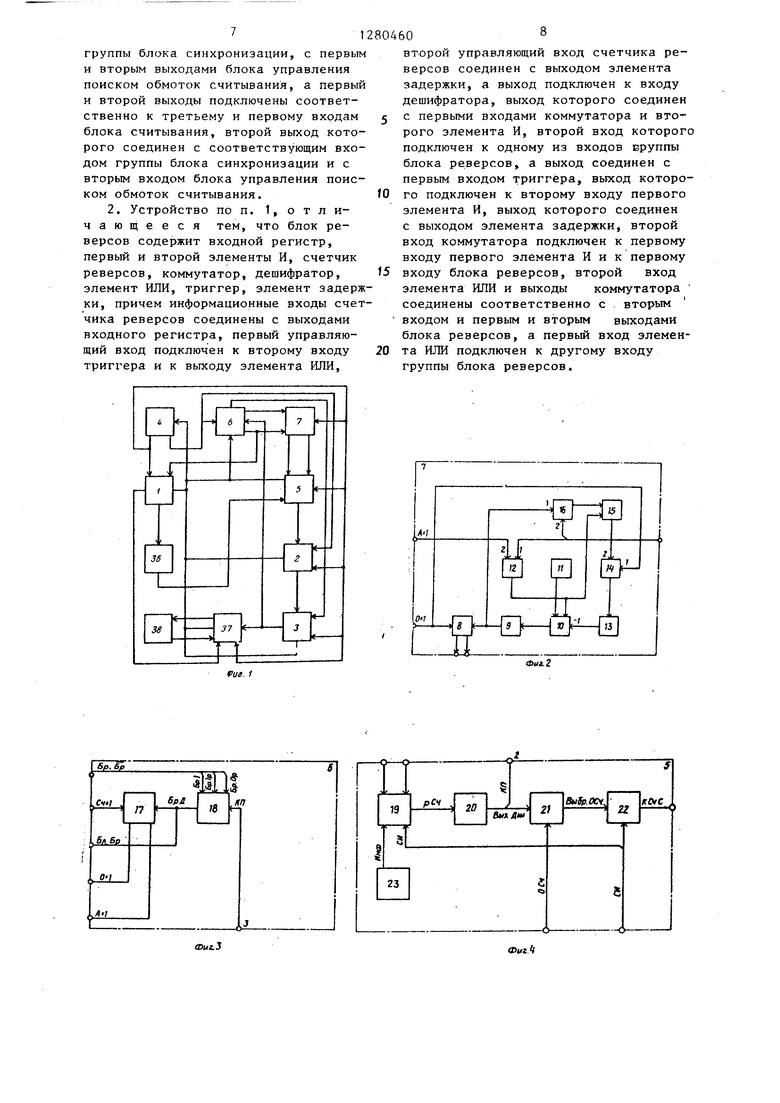

На фиг. 1 представлена схема устройства для контроля параметров ферритовых сердечников запоминающих матриц; на фиг. 2 - схема блока реверсов; на фиг. 3 - схема блока управления поиском обмоток считывания; на фиг. 4 - схема блока считывания; на фиг. 5 - схема блока контроля.

Устройство (фиг. 1) содержит блок выборки 1, блок контроля 2, блок выходных регистров 3, блок синхронизации 4, блок считывания 5, блок управления поиском обмоток считывания 6, блок реверсов 7.

Блок реверсов (фиг. 2) содержит коммутатор 8, дешифратор 9, счетчик реверсов 10, входной регистр 11, элемент ИЛИ 12, элемент задержки 13, первый элемент И 14, триггер 15, второй элемент И 16.

Блок управления поиском обмоток считывания (фиг. 3) содержит коммутатор 17 и элемент И 18.

Блок считывания (фиг. 4) содержит счетчик 19, дешифратор 20, коммутатор 21, усилитель-преобразова- . тель 22, входной тумблерный ре- . гистр 23.

Блок контроля (фиг. 5) содержит узел сравнения обработки результатов 24 и узел управления кратностью контроля 25. Узел 24 включает схему сравнения 26, схему обработки результатов 27, счетчик циклов 28 и входной тумблерный регистр задания порогов контроля 29, а узел управления кратностью контроля 25 содержит формирователь кода коррекции 30, сумматор-вычитатель 31, управляющий триггер 32 с входной логикой ИЛИ 33, коммутатор результатов контроля 34 и коммутатор кратности контроля 35.

Блок выборки 1 имеет в своем составе счетчики адресов по двум координатам, адресные дешифраторы, формирователи и коммутаторы координатных токов испытательной программы, подача которых на выбранные координатные провода проверяемой матрицы 36 и является его назначением.

5

0

5

0

5

0

5

0

5

Блок выходных регистров 3 содержит регистры годности, брака и конца проверки по числу проверяемых параметров и предназначен для приема из блока контроля 2 и выдачи через блок сопряжения 37 на внешнее регистрирующее устройство 38 результатов контроля, а также выдачи в блок синхронизации 4 сигналов окончания проверки сердечника раздельно по каждому проверяемому параметру.

Блок с-инхронизации 4 устройства имеет в своем составе задающий генератор тактовой частоты, схему пуска- останова, временной датчик испытательной программы, схему прерывания программы контроля на время переключения герконных коммутаторов и схему формирования управляющих синхроимпульсов. Он предназначен для организации программы контроля и согласования работы всех узлов устройства.

Блок сопряжения 37 предназначен для согласования работы устройства с внешним регистрирующим устройством 38 по электрическим и временным параметрам.

Б устройстве имеется еще ряд узлов вспомогательного назначения, не показанных на фиг. 1: встроенный цифровой импульсный милливольтметр, счетчик количества брака, схема измерения амплитуды координатных токов, блок питания, панель управления и сигнализации и др.

На схемах (фиг. 1-5) не показаны также цепи начальной установки регистров и триггерных схем.

Устройство осуществляет контроль сердечников матрицы по параметрам; единице (1), единице разрушенной (1р), нулю разрушенному (Ор) в трех раздельных временных каналах путем измерения и сравнения с пороговыми значениями амплитуды считанного сигнала, а также по коэффициенту разрушения единицы (К) в том же канале, что и по (1р), представляющему собой отношение амплитуды сигнала (1р) к амплитуде сигнала (1), измеренной в предьщущем временном канале.

Устройство работает следующим образом.

Перед началом контроля с помощью органов панели управления устройства задается режим проверки, устанавливаются требования к параметрам сердеч- }1иков, задается количество обмоток

считывания в проверяемой матрице - набором на входном тумблерном.регистре 23, задается количество реверсов обмоток считывания, соответствующее классу эквивалентности по этому признаку, к которому принадлежит проверяемая матрица - набором на входном тумблерном регистре реверсов 11., все регистры и триггерные схемы устанавливают в исходное состояние. fO

В исходном состоянии к генераторам токов испытательной программы лока выборки 1 подключены координатные провода первого сердечника проверяемой матрицы 36, В счетчик 19 f5 блока считывания 5 принята из входного регистра 23 комбинация, соответствующая числу обмоток считывания в матрице. При этом сигналом от дешифратора 20 блока считывания 5 ком- 20 мутатор 21 держит подключенной к входу усилителя-преобразователя 22 первую обмотку считывания матрицы 36.

Блок управления поиском обмоток считывания 6 держится в состоянии, 25 разрешающем прохождение сигнала прибавления единицы к адресу от блока синхронизации 4 к блоку выборки 1, так как на входах элемента И 18 отсутствует комбинация сигналов брак 1, 30 да блока реверсов 7 через коммутатор брак 1р, годн. Ор, соответствующая потере обмотки считывания, при наличии разрешающего уровня на третьем входе блока 6, свидетельствующего о невыходе за пределы заданного числа 35 обмоток считывания.

В блоке реверсов 7 в исходном состоянии в счетчик реверсов 10 принята комбинация из входного регистра реверсов 11, соответствующая классу, 40 которому принадлежит матрица по этб- му признаку. Поскольку эта комбинация не является нулевой, сигнал с выхода дешифратора нуля 9 поддерживает коммутатор 8 в состоянии, раз- 45 решающем прохождение сигнала с его информационного входа на второй выход блока 7,. соединенный с входом сложения счетчика 19 блока считывания 5. Исходным состоянием тригге- 50 ра 15 блока реверсов через элемент И1 14 и элемент задержки 13 держится открытой цепь подачи сигнала от третьего входа блока 7 на вход вычитания счётчика реверсов 10. . 55

8 на вход сложения счетчика 19 блока считывания 5, что соответствует обратному ходу в переборе обмоток считывания. Параллельно идет вычитание по единице на каждом шаге поиска из счетчика реверсов 10 до его обнуления через открытую цепь из элементов И1 14 и задержки 13, после чего сигнал прибавления единицы переключается коммутатором В блока 7 со входа сложения счетчика 19 блока 5 на вход вычитания, а вход вычитания счетчика реверсов 10 блокируется запиранием элемента И1 14 сигналом с выхода триггера 15, переброшенного сигналом от дешифратора нуля 9 по стробу от блока синхронизации 4 через элемент И2 16 блока 7, Возобновляется перебор обмоток считывания уже .в прямом поступательном направлении, соответствующем работе счетчика 19 блока 5 на вычитание.

На протяжении всего цикла поиска обмотки считывания продолжается работа схем контроля в блоке конт- роля 2. Однако сигнал с выхода элемента И 18 блока 6 запрещает вьщачу сигнала, запускающего печать брака.

После запуска программы контроля начинается последовательный контроль сердечников матрицы в порядке возрастания их адресов путем измерения амплитуды считанного сигнала и ср ав- нения ее с пороговыми значениями в блоке контроля 2. Циклы измерения и сравнения повторяются по несколько раз, и по их результатам в блоке контроля 2 принимается окончательное решение о годности или негодности сердечника. В последнем случае результат контроля выводится на печать регистрирующим устройством 38.

При потере обмотки считывания в процессе последовательного перебора адресов происходит следующее.

Блок контроля 2 вырабатывает сигнал брака с компонентами по проверяемым параметрам брак 1, брак 1р, годн. Ор. В результате этого блок управления поиском обмоток считывания 6 переключает сигнал прибавления единицы к текущему адресу от блока выборки 1 к блоку реверсов 7 на вход коммутатора 8. При этом перебор адресов сердечников приостанавливается и начинается реверсньгй перебор обмоток считывания на столько щагов обратно, сколько задано входным регистром реверсов 11, так как открыта цепь подачи сигнала от третьего входа блока реверсов 7 через коммутатор

8 на вход сложения счетчика 19 блока считывания 5, что соответствует обратному ходу в переборе обмоток считывания. Параллельно идет вычитание по единице на каждом шаге поиска из счетчика реверсов 10 до его обнуления через открытую цепь из элементов И1 14 и задержки 13, после чего сигнал прибавления единицы переключается коммутатором В блока 7 со входа сложения счетчика 19 блока 5 на вход вычитания, а вход вычитания счетчика реверсов 10 блокируется запиранием элемента И1 14 сигналом с выхода триггера 15, переброшенного сигналом от дешифратора нуля 9 по стробу от блока синхронизации 4 через элемент И2 16 блока 7, Возобновляется перебор обмоток считывания уже .в прямом поступательном направлении, соответствующем работе счетчика 19 блока 5 на вычитание.

На протяжении всего цикла поиска обмотки считывания продолжается работа схем контроля в блоке конт- роля 2. Однако сигнал с выхода элемента И 18 блока 6 запрещает вьщачу сигнала, запускающего печать брака.

10

15

5 izeo ieo6

закрывая цепь, выдающую сборку сигналов брака в блок сопряжения 37 из блока выходных регистров 3. Поэтому возникающие в цикле поиска сигналы с компонентами брак 1, брак 1р, годн. Ор на регистрирующем устройстве 38 (и в счетчике брака) не учитываются и на печать не выводятся-.

Выход на обмотку считывания, соответствующую проверяемому сердечнику, который может произойти либо уже при реверсном ходе поиска, либо после возобновления прямого Хода, вызывает исчезновение сигнала вида брак 1, брак 1р, годн. 6р от блока выходных регистров 3 на входе элемента И 18 блока 6, в результате чего восстанавливается исходное состояние коммутатора 17, переключив сигнал прибав- ления единицы к адресу, вырабатыва- 20 циклом поиска, начинающимся

efibM блоком синхронизации 4 снова на вход второй блока выборки 1. При этом возобновляется работа адресных коммутаторов блока выборки 1 и вместе с ней дальнейший последовательный перебор адресов с контролем сердечников, связанных с найденной обмоткой считывания.

Блокировка печати результатов контроля снимается, а первый же сигнал прибавления единицы к текущему адресу сердечника, поступая на вход второй блока реверсов 7, возвращает

ся в состояние, соответствующее по ледовательному обходу адресов. При этом наличие брака указанного вид будет зафиксировано регистрирующим устройством 38.

В конце цикла поиска, вызванно сколотым сердечником, блок синхро зации 4 вырабатывает сигнал, восс навливающий исходное состояние сче чика, разрешение на выдачу которо дается сигналом от дешифратора 20 соответствующим нулевой комбинации в счетчике 19, которая свидетельс ет о выходе за пределы заданного к личества обмоток считывания.

После выхода из поиска по скол тому сердечнику выход на текущую обмотку считывания осуществляется

первой обмотки считывания.

Формула изобретения

25

30

1. Устройство для контроля фер товых сердечников запоминающих ма риц, содержащее блок синхронизаци выходы группы которого соединены первыми входами блока выборки и б ка выходных регистров и с первыми входами блока считывания и блока контроля, один выход подключен к вому входу блока управления поиск обмоток считывания и к первому вх блока контроля, а соответствующие входы блока синхронизации соедине с первыми выходами блока выходных регистров, блока контроля и блока борки, второй и третий выходы кот

в исходное состояние счетчик реверсов 10, триггер 15 и коммутатор 8, подготавливая их к новому заходу в цикл поиска. Состояние счетчика обмоток считывания 19 блока 5 при выходе из цикла поиска не изменяется. Ис35

1. Устройство для контроля ферри- товых сердечников запоминающих матриц, содержащее блок синхронизации, выходы группы которого соединены с первыми входами блока выборки и блока выходных регистров и с первыми входами блока считывания и блока контроля, один выход подключен к первому входу блока управления поиском обмоток считывания и к первому входу блока контроля, а соответствующие входы блока синхронизации соединены с первыми выходами блока выходных регистров, блока контроля и блока выборки, второй и третий выходы котоиосстанавливается только при новом запуске программы контроля с начального адреса и при выходе из цикла

ходное его состояние, соответствующее 40 являются выходами первой группы числу обмоток считывания в матрице, устройства, а второй вход подключен

к первому выходу блока управления поиском обмотки считывания, выходы группы которого соединены с входами

поиска, заход в который вызван сколом 45 группы блока выходных регистров, а сердечника.входы группы подключены к выходам

группы блока выходных регистров и являются выходами второй группы устройства, второй выход блока контроля соединен с вторым входом блока выходных регистров, а второй вход подключен к первому выходу блока считывания, второй вход которого является входом устройства, отличаю- , щ е е с я тем, что, с целью повыше- комбинации. Выходной сигнал от дешиф- ния быстродействия, в устройство ввеВ случае захода в цикл по сколу сердечника, который дает те же компоненты результатов контроля,- что и потеря обмотки считывания - брак 1 брак 1р, годн. Ор, выход из этого цикла осуществляется после перебора всех оставшихся обмоток считывания и появления в счетчике 19 нулевой

50

ратора 20, соответствующий этому состоянию счетчика 19, заблокирует элемент И 18 и коммутатор 17 вернет

циклом поиска, начинающимся

ся в состояние, соответствующее последовательному обходу адресов. При этом наличие брака указанного вида будет зафиксировано регистрирующим устройством 38.

В конце цикла поиска, вызванного сколотым сердечником, блок синхрони- зации 4 вырабатывает сигнал, восстанавливающий исходное состояние счетчика, разрешение на выдачу которого дается сигналом от дешифратора 20, соответствующим нулевой комбинации в счетчике 19, которая свидетельствует о выходе за пределы заданного количества обмоток считывания.

После выхода из поиска по сколотому сердечнику выход на текущую обмотку считывания осуществляется

циклом поиска, начинающимся

первой обмотки считывания.

Формула изобретения

1. Устройство для контроля ферри- товых сердечников запоминающих матриц, содержащее блок синхронизации, выходы группы которого соединены с первыми входами блока выборки и блока выходных регистров и с первыми входами блока считывания и блока контроля, один выход подключен к первому входу блока управления поиском обмоток считывания и к первому входу блока контроля, а соответствующие входы блока синхронизации соединены с первыми выходами блока выходных регистров, блока контроля и блока выборки, второй и третий выходы кото,

50

ден. блок реверсов, входы первой и второй группы входов которого соединены с соответствующими выходами

группы блока синхронизации, с первым и вторым выходами блока управления поиском обмоток считывания, а первый и второй выходы подключены соответственно к третьему и первому входам блока считывания, второй выход которого соединен с соответствующим входом группы блока синхронизации и с вторым входом блока управления поиском обмоток считывания.

2. Устройство по п. 1, отличающееся тем, что блок реверсов содержит входной регистр, первый и второй элементы И, счетчик реверсов, коммутатор, дешифратор, элемент ИЛИ, триггер, элемент задержки, причем информационные входы счетчика реверсов соединены с выходами входного регистра, первый управляющий вход подключен к второму входу триггера и к выходу элемента ИЛИ,

второй управляющий вход счетчика реверсов соединен с выходом элемента задержки, а выход подключен к входу дешифратора, выход которого соединен с первыми входами коммутатора и второго элемента И, второй вход которог подключен к одному из входов вруппы блока реверсов, а выход соединен с первым входом триггера, выход которого подключен к второму входу первого элемента И, выход которого соединен с выходом элемента задержки, второй вход коммутатора подключен к первому входу первого элемента Инк первому входу блока реверсов, второй вход элемента ИЛИ и выходы коммутатора соединены соответственно с вторым входом и первым и вторым выходами блока реверсов, а первый вход элемента ИЛИ подключен к другому входу группы блока реверсов.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля параметров ферритовых сердечников запоминающей матрицы | 1984 |

|

SU1200346A1 |

| Устройство для контроля параметров ферритовых сердечников запоминающей матрицы | 1981 |

|

SU963110A1 |

| Биотехническое адаптируемое устройство для бесклавишного ввода информации | 1987 |

|

SU1576901A1 |

| Устройство для контроля запоминающих матриц | 1979 |

|

SU875468A1 |

| Устройство для контроля функционирования логических блоков | 1987 |

|

SU1432528A2 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1991 |

|

RU2017241C1 |

| Система для поиска и обработки научно-технической информации | 1981 |

|

SU993273A1 |

| Устройство для поиска информации на ленточном носителе | 1984 |

|

SU1208564A1 |

| Устройство для контроля интегральных блоков памяти | 1980 |

|

SU877622A1 |

| Устройство для контроля блоков памяти | 1986 |

|

SU1444896A1 |

Изобретение относится к вычислительной технике и может быть ис- пользавано для контроля ферритовых запоминающих устройств в процессе их производства. Целью изобретения является повьшение быстродействия устройства. Устройство содержит блок выборки, блок контроля, блок выходных регистров, блок синхронизации, блок считывания, блок управления поиском обмоток считывания и блок реверсов, В устройстве обеспечивается сокращение времени поиска обмоток считывания в процессе их коммутации за счет возврата при заходе в цикл поиска не к начальной обмотке, а лишь на необходимое количество шагов возврата (реверсов), на которое может изменяться номер очередной обмотки считывания в процессе последовательного перебора адресов сердечников. 1 з.п. ф-лы, 5 ил. (Л

Фиг.З

Фиг 4

Фиг.5

Редактор И. Горват

Составитель О. Исаев

Техред В.Кадар Корректоре. Луговая

Заказ 7057/46

Тираж 543

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производствершо-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

Подписное

| Устройство для контроля параметров ферритовых сердечников запоминающей матрицы | 1981 |

|

SU963110A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Устройство для контроля параметров ферритовых сердечников запоминающей матрицы | 1984 |

|

SU1200346A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1986-12-30—Публикация

1984-11-30—Подача