(54) УСТРОЙСТВО ДЛЯ ПРЕРЫВАНИЯ ПРОГРАММ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для прерывания программ | 1985 |

|

SU1256029A1 |

| Устройство для обмена информацией между цифровой вычислительной машиной и внешними устройствами | 1981 |

|

SU1003066A1 |

| Тренажер оператора автоматизированной системы управления | 1981 |

|

SU983738A1 |

| Устройство для реконфигурации многопроцессорной системы | 1991 |

|

SU1798801A1 |

| Устройство для прерывания программ | 1983 |

|

SU1168945A1 |

| Устройство для сопряжения электронной вычислительной машины с алфавитно-цифровыми дисплеями | 1983 |

|

SU1113792A1 |

| Устройство приоритета | 1978 |

|

SU807295A1 |

| Микропрограммное устройство управления с контролем | 1983 |

|

SU1136162A1 |

| Устройство для контроля работы оператора | 1990 |

|

SU1737485A1 |

| Многоканальное устройство для обслуживания запросов | 1978 |

|

SU769542A1 |

Изобретение относится к вычислительной технике и, в частности, к устройствам для прерывания программ.

Известно устройство для прерывания программ, содержащее регистр прерывания, схему сбора сигналов прерываний, соединепнуго с выходом прерывания устройства, шифратор, регистр зандиты, входы которого соединены с первой грунпой входов устройства, а выходы - с первой группой входов схемы выявления разрещенных прерываний.

Известное устройство для нрерывания программ имеет недостаток: при поступлении сигналов с большой длительностью и с дребезгом фронтов необходимо вводить в состав устройства специальные формирователи, что увеличивает затраты оборудования и снижает надежность устройства.

Цель изобретения - повышение надежности устройства.

Поставленная цель достигается тем, что устройство содержит триггеры управления, первую, вторую, третью и четвертую группы схем «И, первую, вторую и третью группы инверторов, инвертор управления, первый и второй элементы задержки, причем вторая группа входов устройства соединена со входами соответствующей первой группы инверторов, третья группа входов устройства соединена с первыми входами соответствующей второй группы

инверторов, вторые входы которых соединены с выходом первого элемента задержки; выходы первой и второй групп инверторов соединены с единичными входами соответствующих триггеров управления, вторая и третья группы входов устройства соединены с первыми входами соответствующей первой группы схем «И, вторые входы которых соединены через инвертор управления с опросным входом устройства, соединенным со входом второго элемента за0держки, выход которого соединен с ответным выходом устройства, со входом второго элемента задержки и с первыми входами второй группы схем «И, вторые входы которых соеди5 йены с соответствующими входами шифратора; выходы второй группы схем «И соединены с пулевыми входами соответствующих триггеров управления и триггеров регистра прерывания, единичные входы триггеров управления

0 соединены с третьими входами соответствующей первой группы схем «И, выходы которых соединены с единичными входами соответстрЛЮщих триггеров регистра прерывания, единичные выходы которых соединены со входами схемы сбора сигналов прерывания п со второй

5 грунпой входов схемы выявления разрещенных прерываний, выходы которой, кроме первого и последнего, соединены с первыми входами соответствующей третьей группы схем «И

0 п через соответствующую третью группу инверторов - с первыми входами соответствующей четвертой группы схем выходы каждой из четвертой группы схем «И соединены со вторыми входами одной из третьей и одной из четвертой групп схем «И, связанных с последующим выходом схемы выявления разрешенных прерываний, первый выход которой соединен с соответствующим входом шифратора и через соответствующнй инвертор третьей группы инверторов - со вторыми входами одной из третьей и одной из четвертой групп схем «И, связанных с последующим выходом схемы выявления разрешенных прерываний, последний выход которой соединен с первым входом соответствующей схемы «И из третьей группы схем «И, второй вход которой соединен с выходом одной из четвертой группы схем «И, связанной с предыдущим выходом схемы выявления разрещенных прерываний; выходы третьей группы схем «И соединены со входами шифратора, выходы которого соединены с выходами устройства.

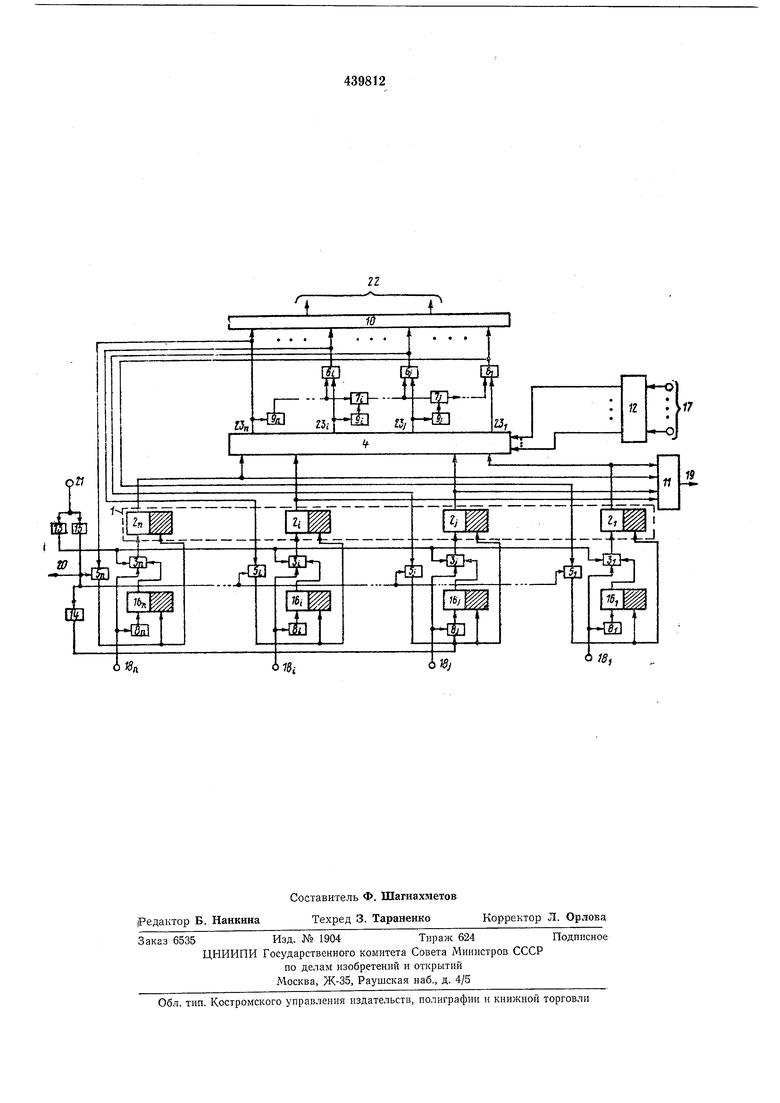

Блок-схема предлагаемого устройства для прерывания программ приведена иа чертелсе.

Устройство содержит регистр прерывания /, триггеры прерывания 2i-Зп , первую группу схем «И 3i--t3,i , схему 4 выявления разрещенных прерываний, вторую группу схем «И , третью группу схем «И , четвертую группу схем «И 7j -7i , первую , вторую 1-Sj и третью группу инверторов 9j-9„, шифратор 10, схему /./ сбора сигналов прерывания, регистр защиты 12, инвертор опроса 75, первый элемент задержки 14, второй элемент задержки :75, триггеры управления

На чертеже обозначены следующие шины: первая группа входных шин ./7, вторая группа входных шин,/5г -18 п , третья группа входных щин , выходная шина прерывания ., шина ответов 20, опросная шина 2/, выходные шины 22 устройства, выходные шины ,25)-23п схемы выявления разрешенных прерываний.

Устройство работает следующим образом.

При отсутствии сигналов прерывания устройство находится в исходном состоянии.

При поступлении старшего по приоритету сигнала прерывания без дребезга, например, по входу/5г триггер 5,- регистра прерывания / через схему устанавливается в состояние «1. Сигнал с триггера 2, поступает на схему 4 выявления разрешенных прерываний. С выхода 23i этой схемы сигнал поступает через инвертор di на схему , а также на схему Сигнал, снимаемый с выхода схемы через схемы -т-f-«H 7j,, блодирует все схемы 6t-i-61. Так как сигнал, снимаемый с выхода 231 является самым старшим по приоритету, то только на выходе схемы 61 появится единичный сигнал. Этот сигнал поступает на вход шифратора 10, на выходах 22 которого формируется

код старшего по приоритету сигнала прерывания.

Сигнал с единичного выхода триггера 2,поступает на схему // сбора сигналов прерываний, с выхода которой .7:9 поступает в вычислительную машину. По этому сигналу вычислительная машина формирует сигнал опроса, по которому производится считывание в вычислительную машину номера старшего по приоритету прерывания. Кроме того, сигнал опроса поступает на опросный вход 21 устройства прерывания и через инвертор опроса ./i5 - на вход схемы , а также через второй элемент задержки 75 - на шину ответов 20 и на вход схемы . Величина задержки элемента J6 равна суммарной задержке прохождения сигнала через схему 4 выявления разрешенных прерываний, схемы , и шифратор JO. При этом с выхода схемы снимается сигнал, который сбрасывает триггер 2i и устанавливает в состояние «О триггер управления . Сигнал, снимаемый с единичного выхода тр-иггера управления 16i, блокирует дальнейшее поступление сигнала прерывания на вход триггера 2 , через схему 3. до тех пор, пока не кончится сигнал на шине М В 1от момент, когда сигнал прерывания на шине/5; прекратится, триггер 7 i через инвертор .8i устанавливается в состояние «1.

Таким образом, предлагаемое устройство при поступлении сигнала прерывания формирует сразу код номера старшего по приоритету прерывания. Формирование этого кода производится на комбинационной схеме, что позволяет, с одной стороны, уменьшить время, необходимое для его получения, а с другой - разгрузить вычислительную машину. Как ясно из описания работы устройства, длительность сигналов прерывания без дребезга фронтов может быть сколь угодно большой. Это обстоятельство позволяет отказаться от дополнительных формирователей, обычно используемых в известных устройствах.

При поступлеиии старшего по приоритету сигнала прерывания с дребезгом фронтов, например, по шине /i5j устройство работает следующим образом.

Триггер управления 16j находится в единичном состоянии, и с инвертора опроса 13 на схему поступает единичлый сигнал. Схема срабатывает, и триггер 2j регистра прерывания 7 переходит в состояние «1.

После того, как данное прерывание будет обслужено, единичный сигнал с выхода схемы 6j поступает на схему , на второй вход которой поступает сигнал опроса через второй элемент задержки 15 с шины 2:1. Выходной сигнал схемы , сбрасывает в нулевое состояние триггер управления 16j и триггер 2j. Нулевой сигнал с вы-хода триггера управления 16j поступает на вход схемы , тем самым блокируя входной сигнал, если он еще не кончился. Сигнал опроса через первый элемент задержки iM (задержка которого заведомо больше длительности входного -сигнала, включая длительность фронтов) и инвертор 8j поступает на единичный вход триггера управления 16/ и устанавливает его в единичное состояние, тем самым подготавлиБИЯ устройство к дальнейшей работе.

Предмет изобретения

Устройство для прерывания программ, содержаш,ее регистр прерывания, схему сбора сигналов прерываний, соединенную с выходом прерывания устройства, шифратор, регистр заш,иты, входы которого соединены с первой группой входов устройства, а выходы - с первой группой входов схемы выявления разрешенных прерываний, отличающееся тем, что, с целью повышения надежности, устройство содержит триггеры управления, схемы «И, инверторы, инвертор управления, элементы задержки, причем вторая группа входов устройства соединена со входами соответствуюш,ей первой группы инверторов, третья группа входов устройства соединена с первыми входами соответствующей второй группы инверторов, вторые входы которых соединены с выходом первого элемента задержки; выходы первой и второй групп инверторов соединены с единичными входами соответствующих триггеров управления, вторая и третья группы входов устройства соединены с первыми входами соответствующей первой группы схем «И, вторые входы которых соединены через инвертор управления с опросным входом устройства, соединенным со входом второго элемента задержки, выход которого соединен с ответным выходом устройства, со входом второго элемента задержки и с первыми входами второй ;труппы схем «И, вторые входы которых соединены с соответствующими входами шифратора; выходы второй группы схем «И соединены с нулевыми входами соответствующих триггеров управления и триггеров регистра прерывания, единичные выходы триггеров управления соединены с третьими входами соответствующей первой группы схем «И, выходы которых соединены с единичными входами соответствующих триггеров регистра прерывания, единичные выходы которых соединены со входами схемы сбора сигналов прерывания и со второй группой входов схемы выявления разрешенных прерываний, выходы которой, кроме первого и последнего, соединены с первыми входами соответствующей третьей группы схем «И и через соответствующую третью группу инверторов - с первыми входами соответствующей четвертой группы схем выходы каждой из четвертой группы схем «И соединены со вторыми входами одной из третьей п одной из четвертой групп схем «И, связанных с последующим выходом схемы выявления разрешенных прерываний, первый выход которой соединен с соответствующим входом шифратора и через соответствующий инвертор третьей группы инверторов - со вторыми входами одной из третьей и одной из четвертой групп схем «И, связанных с последующим выходом схемы выявления разрешенных прерываний, последний выход которой соединен с первым входом соответствующей схемы «И из третьей группы схем «И, второй вход которой соединен с выходом одной из четвертой группы схем «И, связанной с предыдущим выходом схемы выявления разрешенных прерываний; выходы третьей группы схем «И соединены со входами шифратора, выходы которого соединены с выходами устройства.

Авторы

Даты

1974-08-15—Публикация

1972-06-23—Подача