вход (19). вход управления (20), выход управления (21), вход подтверждения прерывания (22), выход прерывания (23), выход отказа (24), коммутационный выход (25),блок прерывания и управления (9), который содержит: 3 элемента И (11, 12,-13), элемент НЕ (10), элемент ИЛИ (14), 2 триггера (15, 16).

Блок 2 синхронизации и кодирования содержит: группу входов отказов, группу входов синхронизации, выход синхронизации. 17-3-5-6-5-4-2-15-11-14-13-21-20-14- 16-23, 17-7-18-17, 19-5-8-R-E. 19-15-5, 4-15, 4-13, 22-30, 22-12-16-23, 26-12,26- 15, 2 з.п. ф-лы, 3 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для распределения заданий процессорам | 1988 |

|

SU1636846A1 |

| Мажоритарно-резервированный интерфейс памяти | 1990 |

|

SU1751766A1 |

| Многопроцессорная система | 1989 |

|

SU1741144A1 |

| Устройство для сопряжения в резервированной многопроцессорной системе | 1987 |

|

SU1501079A1 |

| Устройство для прерывания резервированной вычислительной системы | 1991 |

|

SU1824636A1 |

| Устройство сопряжения процессоров в многопроцессорной вычислительной системе с изменяемой конфигурацией | 1984 |

|

SU1259278A1 |

| Устройство для обработки информации | 1990 |

|

SU1758649A1 |

| Мультипроцессорная система | 1990 |

|

SU1732351A1 |

| Устройство для обмена данными в вычислительной сети | 1988 |

|

SU1599864A1 |

| Устройство для сопряжения процессора с многоблочной памятью | 1986 |

|

SU1319039A1 |

Использование: в резервированных вычислительных структурах. Сущность изобретения: устройство содержит по числу процессоров .каналы (1), блок синхронизации и кодирования (2), 2 резистора (R) источник питания (Е), вход сброса (26), информационный вход - выход (27). Каждый канал содержит: элемент И (7), 2 элемента ИЛИ-НЕ (5, 6), 3 элемента НЕ (3, 4, 8), резистор (Р), источник питания (Е) опросный вход (17), опросный выход (18), сигнальный

Изобретение относится к вычислительной технике и может быть использовано в высоконадёжных многомашинных и многопроцессорных систем и сетях для их реконфигурации при отказах ЭВМ и процессоров.

Целью изобретения является расширение функциональных возможностей устройства за счет обеспечения, прерывания исправного процессора с последующим изменением его инструкции выполнения про- грамм в соответствии с кодом, отказа и возможности использования в резервированной многопроцессорной системе.

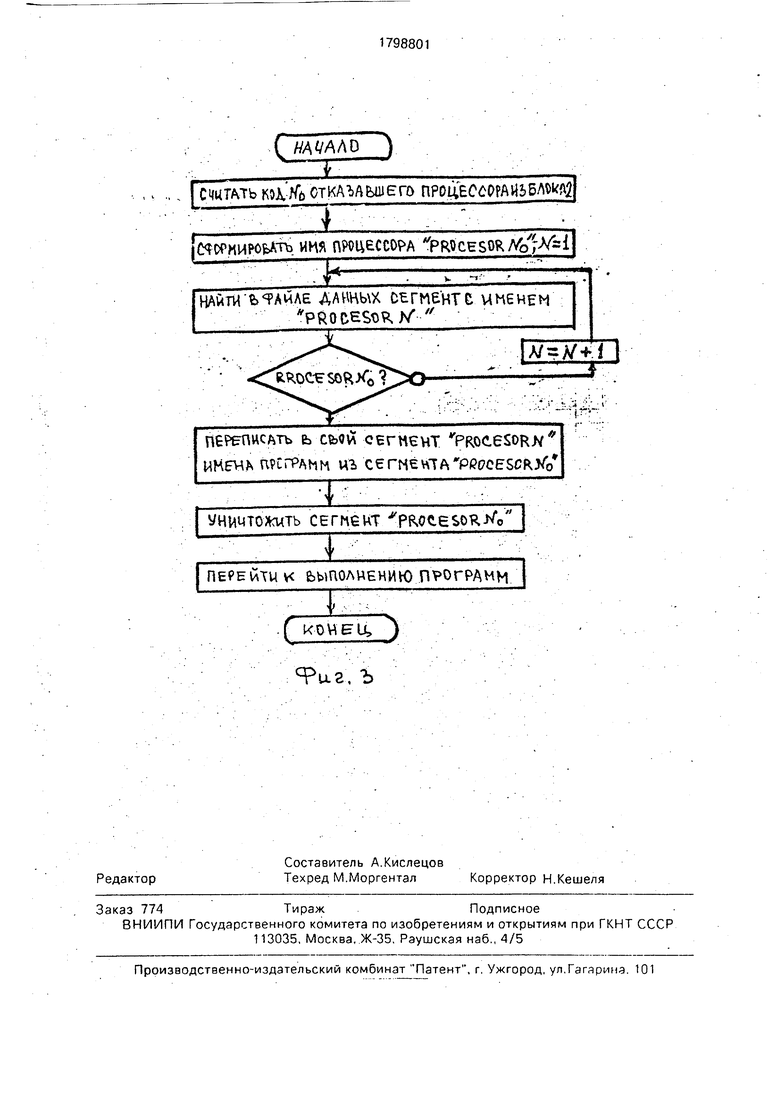

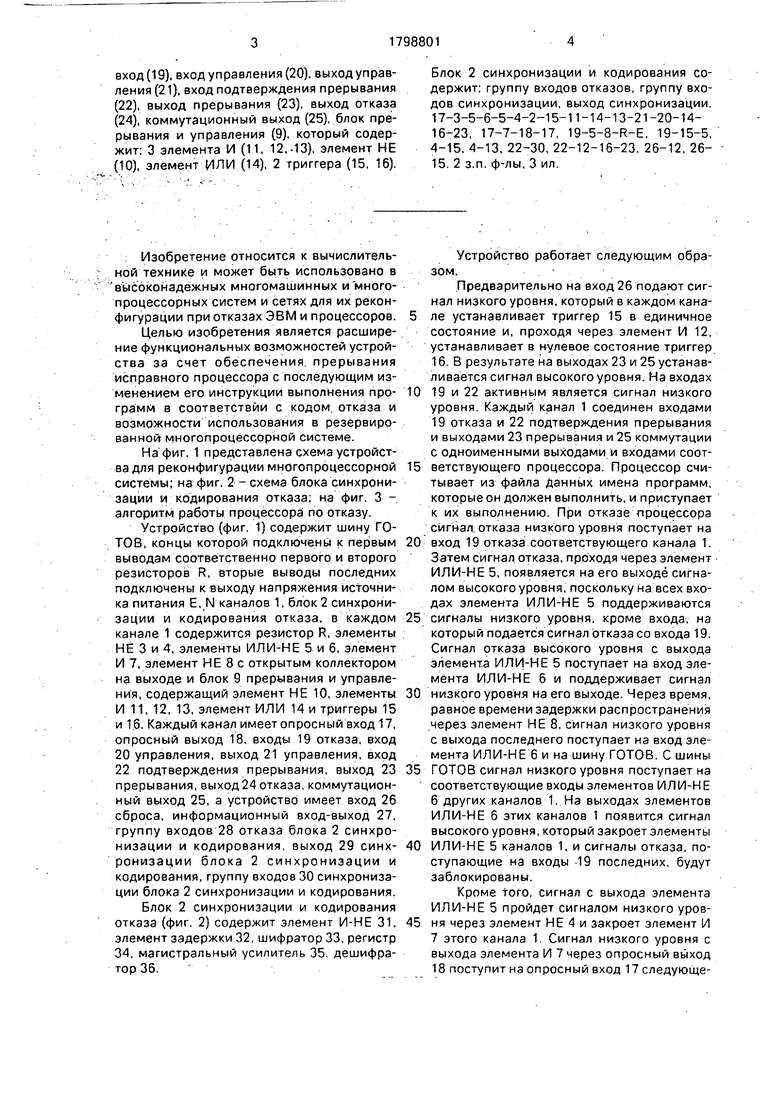

На фиг, 1 представлена схема устройства для реконфигурации многопроцессорной системы; на фиг. 2 - схема блока синхронизации и кодирования отказа; на фиг. 3 - алгоритм работы процессора по отказу.

Устройство (фиг. 1) содержит шину ГОТОВ, концы которой подключены к первым выводам соответственно первого и второго резисторов R, вторые выводы последних подключены к выходу напряжения источник ка питания Е, N каналов 1, блок 2 синхронизации и кодирования отказа, в каждом канале 1 содержится резистор R, элементы НЕ 3 и 4, элементы ИЛИ-НЕ 5 и 6, элемент И 7, элемент НЕ 8 с открытым коллектором на выходе и блок 9 прерывания и управления, содержащий элемент НЕ 10, элементы И 11, 12, 13, элемент ИЛИ 14 и триггеры 15 и 16. Каждый канал имеет опросный вход 17, опросный выход 18, входы 19 отказа, вход 20 управления, выход 21 управления, вход 22 подтверждения прерывания, выход 23 прерывания, выход 24 отказа, коммутационный выход 25, а устройство имеет вход 26 сброса, информационный вход-выход 27. группу входов 28 отказа блока 2 синхронизации и кодирования, выход 29 синх- ронизации блока 2 синхронизации и кодирования, группу входов 30 синхронизации блока 2 синхронизации и кодирования.

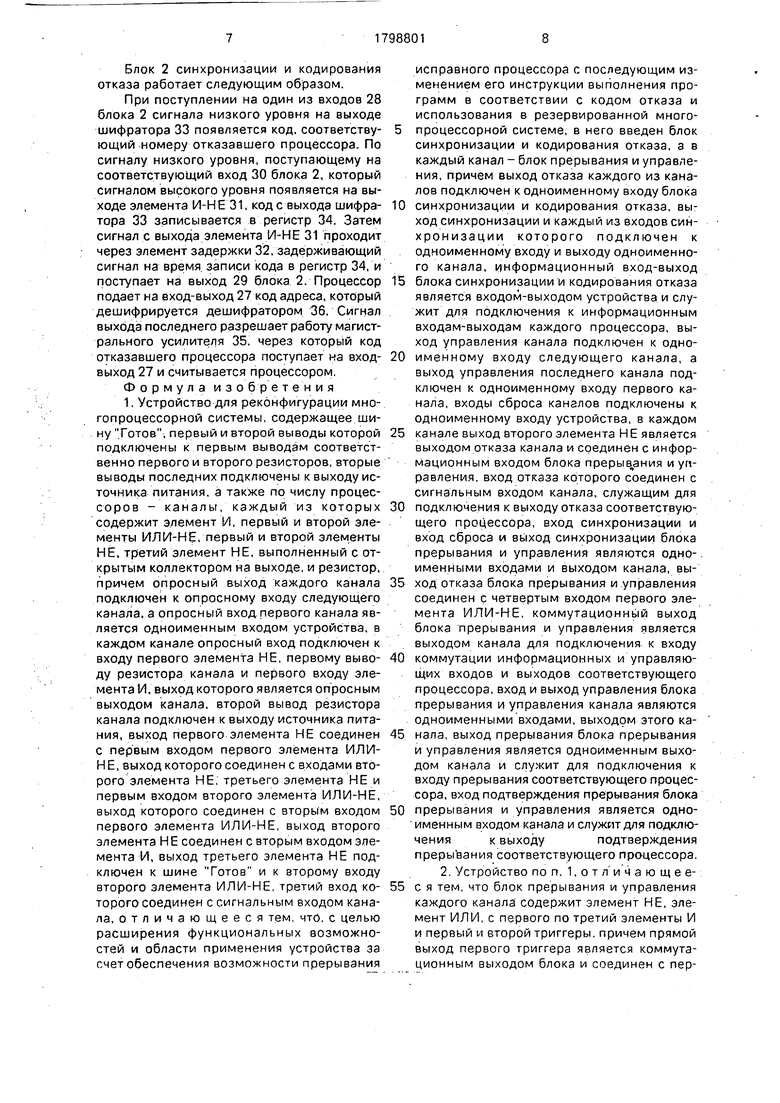

Блок 2 синхронизации и кодирования отказа (фиг. 2) содержит элемент И-НЕ 31, элемент задержки 32, шифратор 33, регистр 34, магистральный усилитель 35. дешифратор 36.

Устройство работает следующим образом.

.Предварительно на вход 26 подают сигнал низкого уровня, который в каждом канале устанавливает триггер 15 в единичное состояние и, проходя через элемент И 12, устанавливает в нулевое состояние триггер 16. В результате на выходах 23 и 25 устанавливается сигнал высокого уровня. На входах 19 и 22 активным является сигнал низкого уровня. Каждый канал 1 соединен входами 19 отказа и 22 подтверждения прерывания и выходами 23 прерывания и 25 коммутации с одноименными выходами и входами соответствующего процессора. Процессор считывает из файла Данных имена программ, которые он должен выполнить, и приступает к их выполнению. При отказе процессора сигнал, отказа низкого уровня поступает на вход 19 отказа соответствующего канала 1. Затем сигнал, отказа, проходя через элемент ИЛИ-НЕ 5, появляется на его выходе сигналом высокого уровня, поскольку на всех входах элемента ИЛИ-НЕ 5 поддерживаются сигналы низкого уровня, кроме входа, на который подается сигнал отказа со входа 19. Сигнал отказа высокого уровня с выхода элемента ИЛИ-НЕ 5 поступает на вход элемента ИЛИ-НЕ б и поддерживает сигнал низкого уровня на его выходе. Через время, равное времени задержки распространения .через элемент НЕ 8, сигнал низкого уровня с выхода последнего поступает на вход элемента ИЛИ-НЕ 6 и на шину ГОТОВ. С шины ГОТОВ сигнал низкого уровня поступает на соответствующие входы элементов ИЛИ-НЕ

6 других каналов 1. На выходах элементов ИЛИ-НЕ 6 этих каналов 1 появится сигнал высокого уровня, который закроет элементы ИЛИ-НЕ 5 каналов 1, и сигналы отказа, поступающие на входы -19 последних, будут заблокированы.

Кроме того, сигнал с выхода элемента ИЛИ-НЕ 5 пройдет сигналом низкого уровня через элемент НЕ 4 и закроет элемент И

7 этого канала 1. Сигнал низкого уровня с выхода элемента И 7 через опросный выход 18 поступит на опросный вход 17 следующего канала 1 и закроет в нем элемент И 7. Сигнал низкого уровня с выхода последнего поступит через опросный выход 18 на опросный вход 17 следующего канала 1 и закроет в нем элемент И 7 и т.д. В каждом следующем канале 1 сигнал низкого уровня с опросного входа 17 пройдет также через элемент НЕ 3 сигналом высокого уровня и заблокирует элемент ИЛИ-НЕ 5 в следующих каналах 1, на входы 19 которых также поступили сигналы отказа одновременно с сигналом отказа предыдущего канала 1.

Сигнал отказа с выхода Элемента НЕ 4 поступит также через выход 24 канала 1 на вход 28 отказа блока 2 синхронизации и кодирования отказа и на информационный вход триггера 15 и вход элемента И 13, закрывая последний. На выходе элемента И 13 возникает перепад напряжения, с высокого уровня на низкий, формируя задний фронт сигнала. Перепад напряжения с высокого уровня на низкий с выхода элемента И 13 через выход 21 управления своего канала 1 поступит на вход 20 управления следующего канала 1. В этом канале 1 задний фронт сигнала пройдет через элемент НЕ 10 и на его выходе сформирует передний фронт сигнала, которым в триггер 16 запишется информация с выхода элемента И 11.

На выходе элемента И 11 будет сигнал высокого уровня, если на входе 19 этого канала 1 отсутствует сигнал отказа низкого уровня, т.е. процессор этого канала 1 исправен. В этом случае в триггер 16 запишется 1, а на его нулевом выходе появится сиг- нал низкого уровня, который на выходе 23 канала V сформирует сигнал.прерывания, элемент ИЛИ 14 будет закрыт сигналом с выхода элемента И 11, поэтому фронт сигнала со входа 20 не будет распространяться в другие каналы 1.

На выходе элемента И 11 будет сигнал низкого уровня, если на входе 19 этого канала 1 присутствует сигнал отказа низкого уровня, т.е. процессор этого канала 1 неис- правей. В этом случае в триггере 16 будет подтверждено нулевое состояние и сигнала прерывания на выходе 2 этого канала 1 не появится.

Сигналом низкого уровня с выхода эле- мента И 11 будет открыт элемент ИЛИ 14 и задний фронт сигнала пройдет через элементы ИЛИ 14, И 13 и появится на выходе 21 канала, поступив на вход 20 управления следующего канала 1. В том канале 1 работа будет происходить описанным образом.

Получив сигнал прерывания с выхода 23 канала 1, процессор перейдет на программу обработки прерывания по отказу и подает на вход 22 своего канала 1 сигнал подтверждения прерывания низкого уровня. Этот сигнал пройдет через элемент И 12 и установит в исходное нулевое состояние триггер 16. Сигнал прерывания с выхода 23 канала 1 будет снят.

Кроме того по сигналу со входа 22 канала 1, который поступит на вход 30 синхронизации блока 2 синхронизации и кодирования отказа в последнем будет сформирован код, соответствующий каналу

I, который с выхода 24 отказа выставил на вход 28 блока 2 свой сигнал отказа. После этого с выхода 29 синхронизации блока 2 сигнал синхронизации запишет в триггер 15 О. Сигналом низкого уровня с единичного выхода триггера 15 будет закрыт элемент И

II. Этот же сигнал поступит на коммутационный выход 25, который отключит входы и выходы отказавшего процессора от системной шины. Сигналом высокого уровня с нулевого выхода триггера 15 закрывается элемент ИЛИ-НЕ 5, отключая сигнал отказа отказавшего процессора от входа 19 канала 1..

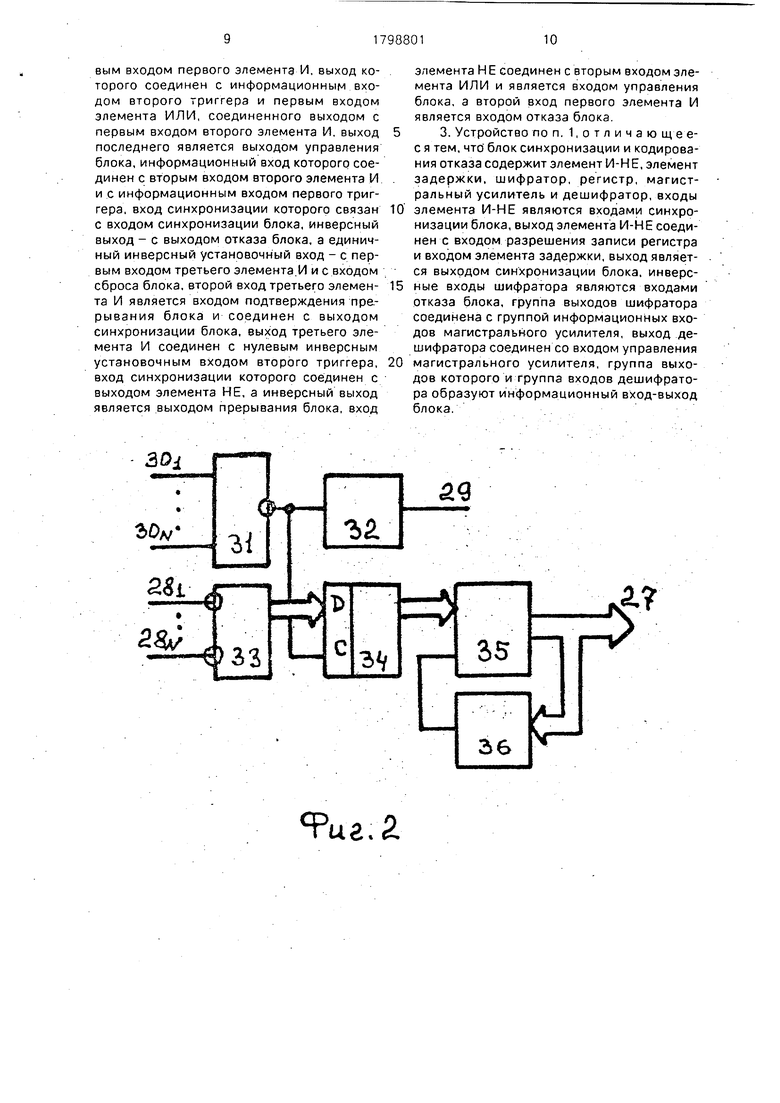

По программе обслуживания (см. фиг. 3) прерывания по отказу процессор считывает с выхода 27 устройства из блока 2 код No отказа, который соответствует номеру отказавшего процессора. После этого процессор формирует имя отказавшего процессора PROCESOR No. ищет в файле данных-сегмент с именем PROCESORNo. После того как этот сегмент найдет, процес- сор переписывает в свой сегмент PROCESOR N имена программ сегмента PROCESOR NO и переходит к выполнению программ. Т.о., после отказа процессора его программы выполняет исправный процессор, выполняя вместе с тем и свои программы.

После отказа всех процессоров, кроме одного, последний будет выполнять все программы, выполняемые системой.

В этот момент, когда триггером 15 канала 1 отказавшего процессора будет заблокирован элемент ИЛИ-НЕ 5, на выходе элемента НЕ 4 будет сформирован сигнал высокого уровня, который пройдет через элементы И 7 всех каналов 1. и в каждом канале 1 на выходах элементов НЕ 3 сформирует сигнал низкого уровня, который откроет элементы ИЛИ-НЕ 5 всех следующих каналов. Кроме того, элемент НЕ 8 сформирует на линии ГОТОВ сигнал высокого уровня, который разрешит работу всех каналов -1, после того как на выходе элемента ИЛИ- НЕ 6 появится сигнал низкого уровня, открывающий элементы ИЛИ-НЕ 5 каналов 1. После этого устройство начинает работать описанным образом.

Блок 2 синхронизации и кодирования отказа работает следующим образом.

При поступлении на один из входов 28 блока 2 сигнала низкого уровня на выходе шифратора 33 появляется код, соответству- ющий номеру отказавшего процессора. По сигналу низкого уровня, поступающему на соответствующий вход 30 блока 2, который сигналом высокого уровня появляется на выходе элемента И-НЕ 31, код с выхода шифра- тора 33 записывается в регистр 34. Затем сигнал с выхода элемента И-НЕ 31 проходит через элемент задержки 32, задерживающий сигнал на время записи кода в регистр 34, и поступает на выход 29 блока 2. Процессор подает на вход-выход 27 код адреса, который дешифрируется дешифратором 36, Сигнал выхода последнего разрешает работу магистрального усилителя 35, через который код отказавшего процессора поступает на вход- выход 27 и считывается процессором.

Формула изобретения

исправного процессора с последующим изменением его инструкции выполнения программ в соответствии с кодом отказа и использования в резервированной многопроцессорной системе, в него введен блок синхронизации и кодирования отказа, а в каждый канал - блок прерывания и управления, причем выход отказа каждого из каналов подключен к одноименному входу блока синхронизации и кодирования отказа, выход синхронизации и каждый из входов син- хронизации которого подключен к одноименному входу и выходу одноименного канала, информационный вход-выход блока синхронизации и кодирования отказа является входом-выходом устройства и служит для подключения к информационным входам-выходам каждого процессора, выход управления канала подключен к одноименному входу следующего канала, а выход управления последнего канала подключен к одноименному входу первого канала, входы сброса каналов подключены к одноименному входу устройства, в каждом канале выход второго элемента НЕ является выходом отказа канала и соединен с информационным входом блока прерывания и управления, вход отказа которого соединен с сигнальным входом канала, служащим для подключения к выходу отказа соответствующего процессора, вход синхронизации и вход сброса и выход синхронизации блока прерывания и управления являются одно-, именными входами и выходом канала, выход отказа блока прерывания и управления соединен с четвертым входом первого элемента ИЛИ-НЕ, коммутационный выход блока прерывания и управления является выходом канала для подключения к входу коммутации информационных и управляющих входов и выходов соответствующего процессора, вход и выход управления блока прерывания и управления канала являются одноименными входами, выходом этого канала, выход прерывания блока прерывания и управления является одноименным выходом канала и служит для подключения к входу прерывания соответствующего процессора, вход подтверждения прерывания блока прерывания и управления является одно- именным входом канала и служит для подключенияк выходу подтверждения прерывания соответствующего процессора. 2. Устройство по п. 1,отличающее-: с я тем, что блок прерывания и управления каждого канала содержит элемент НЕ, элемент ИЛИ, с первого по третий элементы И и первый и второй триггеры, причем прямой выход первого триггера является коммутационным выходом блока и соединен с первым входом первого элемента И, выход которого соединен с информационным входом второго триггера и первым входом элемента ИЛИ, соединенного выходом с первым входом второго элемента И. выход последнего является выходом управления блока, информационный вход которого соединен с вторым входом второго элемента И и с информационным входом первого триггера, вход синхронизации которого связан с входом синхронизации блока, инверсный выход - с выходом отказа блока, а единичный инверсный установочный вход - с первым входом третьего элемента.И и с входом сброса блока, второй вход третьего элемента И является входом подтверждения прерывания блока и соединен с выходом синхронизации блока, выход третьего элемента И соединен с нулевым инверсным установочным входом второго триггера, вход синхронизации которого соединен с выходом элемента НЕ, а инверсный выход является выходом прерывания блока, вход

Фиг. а

элемента Н Е соединен с вторым входом элемента ИЛИ и является входом управления блока, а второй вход первого элемента И является входом отказа блока.

элемента И-НЕ являются входами синхронизации блока, выход элемента И-НЕ соединен с входом разрешения записи регистра и входом элемента задержки, выход является выходом синхронизации блока, инверсные входы шифратора являются входами отказа блока, группа выходов шифратора соединена с группой информационных входов магистрального усилителя, выход дешифратора соединен со входом управления

магистрального усилителя, группа выходов которого и группа входов дешифратора образуют информационный вход-выход блока.

( /МАЛО ). I

| считАть кох /Гб отшльшеп) ПРОЦЕССОРА ЙЬБЛМЭД

i i

JEWMMPOfeATb vma ПИ)ЦЕССОРА PRPCESO

НАйПГЬЯ АНЛЕ ДАННЫХ СЕГМЕНТ t W Мб НЕМ PRODHSO N

перепйСАть ь-сйвй сегмент pRocesoRw

ИК6 ЛКГРАММ ИЪ CgrHgHTA PgpQESCRJ/b

:

УНйчт6-}кмть сегнеит pRotesoR- o

ПЕРБй иу ЬЫПОЛЦЕНИЮ ПРОГРАММ

f kougUL, У ЯРиг, Ъ

| Устройство для сопряжения в резервированной многопроцессорной системе | 1985 |

|

SU1304031A1 |

| Кузнечная нефтяная печь с форсункой | 1917 |

|

SU1987A1 |

| Устройство для сопряжения процессоров в многопроцессорной вычислительной системе | 1984 |

|

SU1211747A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Пневматический водоподъемный аппарат-двигатель | 1917 |

|

SU1986A1 |

| Шевкопляс Б.В | |||

| Микропроцессорные структуры | |||

| М.: Радио и связь | |||

| Пневматический водоподъемный аппарат-двигатель | 1917 |

|

SU1986A1 |

| . | |||

Авторы

Даты

1993-02-28—Публикация

1991-02-25—Подача