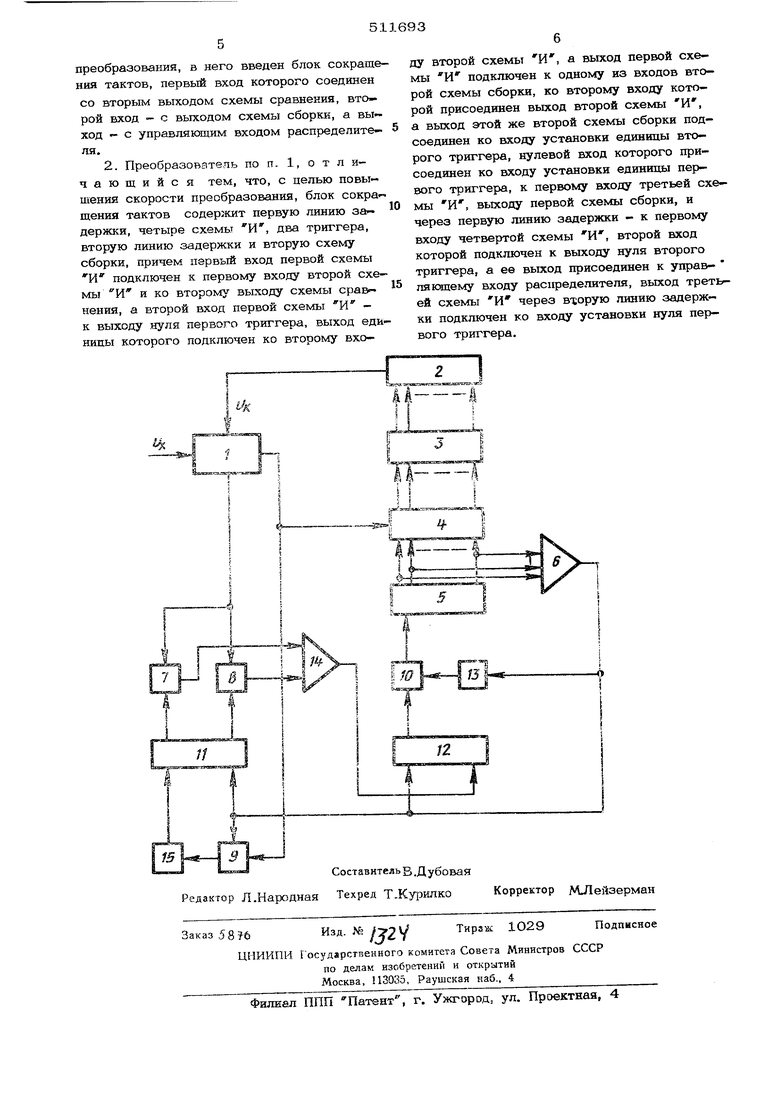

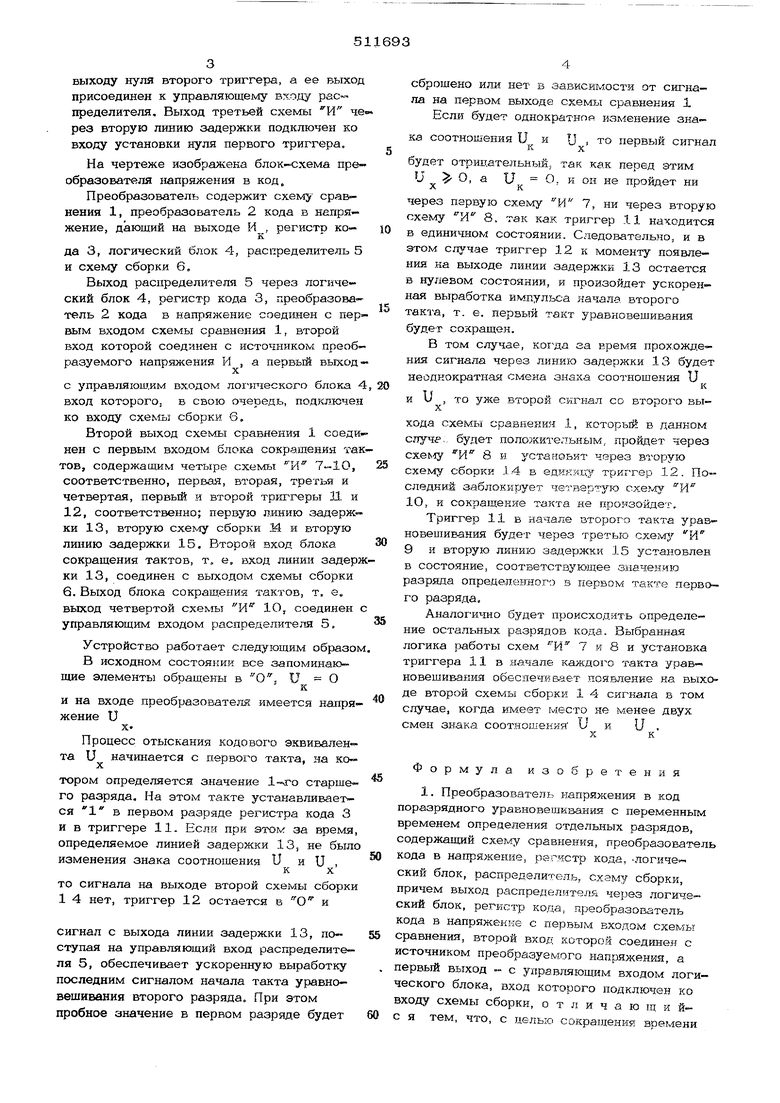

выходу нуля второго триггера, а ее выход присоединен к управляющему Bxojoy распределителя. Выход третьей схемы И че рез вторую линию задержки подключен ко входу установки нуля первого триггера. На чертеже изображена блок-схема пре образователя 1юпряжения в код. Преобразователь содержит сравнения 1, преобразователь 2 кода в напряжение, дающий на выходе И , регистр кода 3, логический блок 4, распределитель 5 и схему сборки 6, Выход распределителя 5 через логический блок 4, регистр кода 3, преобразователь 2 кода в напряжение соединен с пер вым входом схемы сравнения 1, второй вход которой соединен с источником преоб разуемого напр5яжения И , а первый выход с управляющим входом логического блока вход которого, Б свою очередь, подключен ко входу схемы сборки 6. Второй выход схемы сравнения 1 соеди нен с первым входом блока сокращения та тов, содержащим четыре схемы Vl 7-1О, соответственно, первая, вторая, третья и четвертая, первьй и второй триггеры И и 12, соответственно; первую линию задерж ки 13, вторую схему сборки М и вторую линию задержки 15, Второй вход блока сокращения тактов, т. е, вход линии задер ки 13, соединен с выходом схемы сборки 6. Выход блока сокраш.ени.й тактов, т. е. выход четвертой схемы И iO, соединен управляющим входом распределителя 5, Устройство работает следующим образо В исходном состоянии все запоминающие элементы обращены Б, О, U О и на входе преобразователя имеется напряжение и Процесс отыскания кодового эквивалента и начинается с первого такта, на ко- тором определяется значение 1-чго старщего разряда. На этом такте устанавливается 1 в первом разряде регистра кода 3 и в триггере 11. Если при этом за время определяемое линией задержки 13, не было изменения знака соотнощения U и U , кX то сигнала на выходе второй схемы сборки 1 4 нет, триггер 12 остается в О и сигнал с выхода линии задержки 13, поступая на управляющий вход распределителя 5, обеспечивает ускоренную выработку последним сигналом начала такта уравновешивания второго разряда. При этом пробное значение в первом разряде будет сброщено или нет в зависимости от сигнала на первом выходе схемы сравнения 1 Если будет однократной изменение знака соотношения U и TJ , то первый сигнал кX будет отрицательный, так как перед этим и О, а и О. и он не пройдет ни Xк через первую схему И 7, ни через вторую схему И 8. так как триггер 11 находится в едини шом состоянии. Следовательно, и в этом случае триггер 12 к моменту появления на выходе линии задержки 13 остается в нулевом состоянии, и произойдет ускоренная выработка импульса начала второго такта, т. е. первый такт уравновещивания будет сокращен. В том случае, за время прохождения сигнала через линию задержки 13 будет неоднократная смена знака соотнощения U и и , то уже второй сигнал со второго выхода схемы сравнения 1, который в данном сггучг будет положительным, пройдет через схему 8 и устаноьит через вторую схему сборки 14 в едикунгу триггер 12. По следний заблокирует четвертую cxejviy И 1О, и сокращение такта не произойдет. Триггер 11 в начале второго такта уравновещивания будет через третью cxeivi7/ И 9 и вторую линию задержки 15 установлен в состояние, соответствующее значениюразряда определенного в первом такте первого разряда. Аналогично будет происходить определение остальных разрядов кода. Выбранная логика работы схем И 7 м 8 и установка триггера 11 в начале каждого такта урав- новещиваиия обеспечивает появление на выходе второй схемы сборки 1 4 сигнала в том случае, когда имеет место не менее двух смен знака соотношенигг U и Формула изобретения 1. Преобразователь напряжения в код оразрядного уравновешиБания с переменным ременем определения отдельных разрядов, одержащий сравнения, преобразователь ода в напряжение, регистр кода, -логиче--. кий блок, распределитель, схамл сборки, ричем выход распределители через логичекий блок, регистр кода, преобразователь ода в напряженке с первым входом схемы равнения, второй вход которой соединен с сточником преобразуемого напряжения, а ервый выход - с управляющим входом логиеского блока, вход которого подключен ко ходу схемы сборки, отличающийя тем, что, с целью сокращения времени

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналого-цифровой преобразователь поразрядного уравновешивания | 1971 |

|

SU440784A1 |

| Преобразователь напряжения в код поразрядного кодирования | 1973 |

|

SU517999A1 |

| Устройство управления | 1984 |

|

SU1229721A1 |

| Аналого-цифровой преобразователь | 1980 |

|

SU884127A1 |

| Устройство для вычисления показателя экспоненциальной функции | 1985 |

|

SU1270770A1 |

| Аналого-цифровой преобразователь с самоконтролем | 1980 |

|

SU886236A2 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬBr^irr^f^^.ocitJ и а ^ и»^ ^^- \^ f "^.' -^' S i.' . /I'i.';'^-:; •^;-"'-J ; iXJ'4-'^, | 1972 |

|

SU332567A1 |

| УСТРОЙСТВО АНАЛОГО-ЦИФРОВОГО ПРЕОБРАЗОВАНИЯ | 1991 |

|

RU2020751C1 |

| Устройство для вычисления показателя экспоненциальной функции | 1986 |

|

SU1335990A1 |

| Преобразователь напряжения в двоичный код | 1972 |

|

SU482005A1 |

Авторы

Даты

1976-04-25—Публикация

1971-06-14—Подача