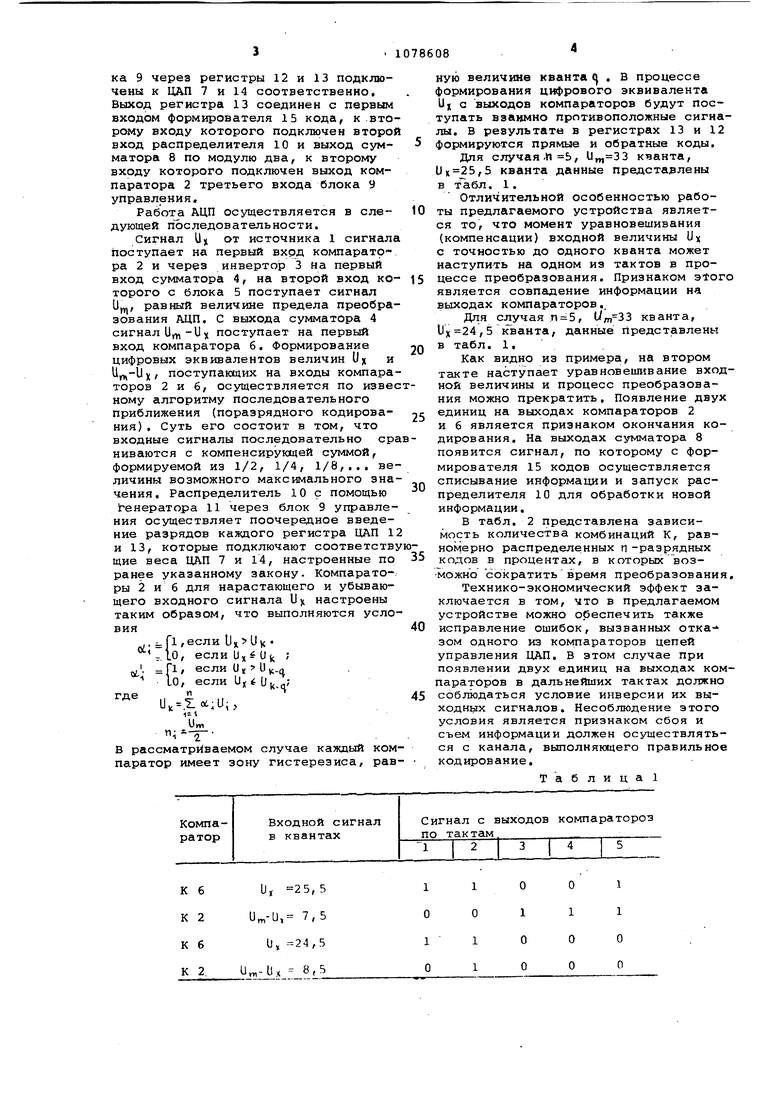

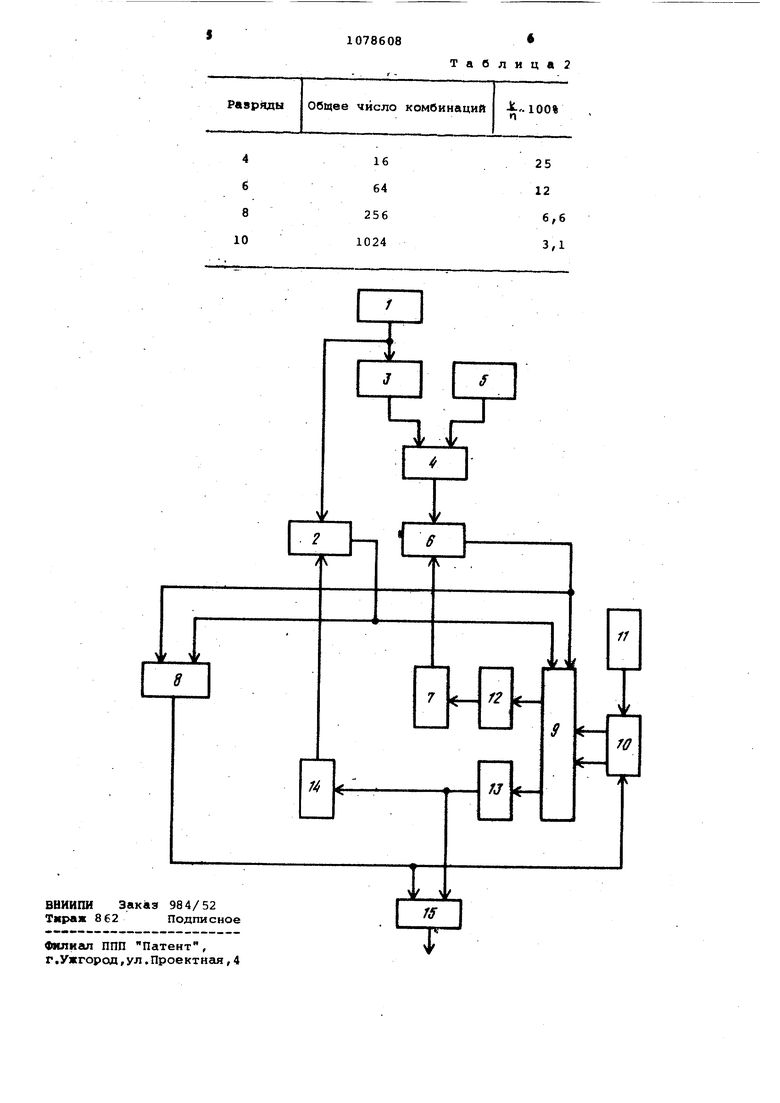

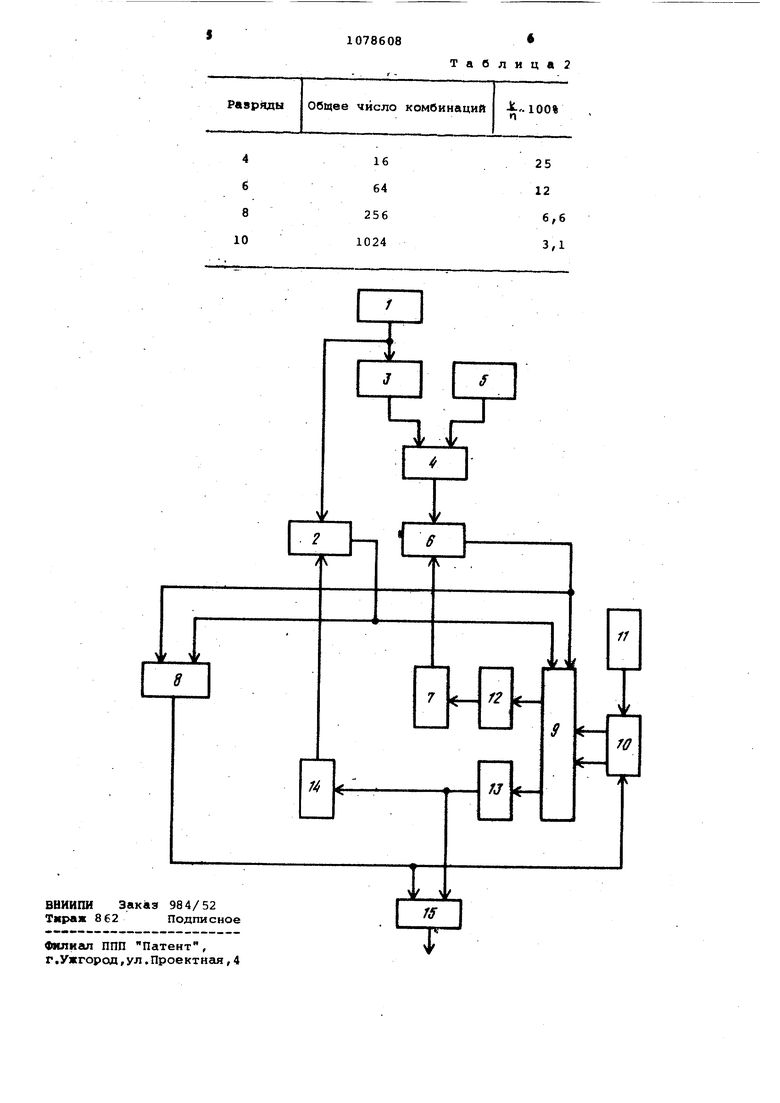

Изобретение относится к информационно-измерительной и вычислительной технике и может быть использован в системах автоматического контроля и управления технологическими процес сг1ми, Известен аналого-цифровой преобра зователь поразрядного кодирования, содержащий генератор, распределитель блок логических схем, регистр, цифро аналоговый преобразователь (ЦАП) обратной связи и компаратор, к первому входу которого подключена шина входного сигнала, к второму входу выход ЦАП обратной связи. Выход компаратора соединен с первым входом блока логических схем, к второму вхо ду которого подключен выход распреде лителя. Выход блока логических схем через регистр соединен с ЦАП обратно связи. Выход генератора подключен к входу распределителя ij , Недостатком этого ЦАП является постоянство времени выдачи результатов преобразования независимо от момента установления цифрового эквивалента измеряемой величины. Известен АЦП последовательного счета с обратной связью, содержащий две схемы сравнения, два преобразова теля кода в напряжение, триггер, генератор импульсов, вентиль, счетчик сборки и схемы считывания кодов. В этом АЦП измеряемое напряжение сра нивается с двумя компенсирующими сиг налами, приближающимися к нему: один от верхнего предела измерения, а дру гой - от нижнего предела. Это позволяет сократить среднее время преобра зования 2j . Недостатком устройства является то, что несмотря на высокие требования к идентичности каналов трактов схема сравнения ЦАП, время преобразо вания остается большим, так как реализуется медленнодействующий алгоритм. Наиболее близким к предлагаемому является двухканальный аналого-цифро вой преобразователь, содержащий генератор, выход которого подключен к первому входу распределителя, первый И второй выходы которого через блок управления соединены с входами первого и второго регистров цифроаналоговых преобразователей соответственно, выходы которых через первый и второй цифроаналоговые преобразователи подключены соответственно к первым входам первого и второго компараторов, выходы которых соединены с третьим и четвертым входами блока управления источник входного сигнала, выход которого подключен к второму вхоДУ пеР вого компаратора з , Недостатками устройства являются то, что используемый в нем асинхронный алгоритм уравновешивания неустойчив к помехам и сбоям, а также имеет большое время преобразования. Цель изобретения,- сокращение среднего времени преобразования массива входной аналоговой информации. Поставленная цель достигается тем, что в аналого-цифровой преобразователь, содержащий генератор, выход которого подключен к первому входу распределителя, первый и второй выходы которого через блок управления соединены с входами первого и второго регистров цифроана/юговых преобразователей соответственно, выходы которых через первый и второй цифроаналоговые преобразователи подключены соответственно к первым входам первого и второго компараторов, выходы которых соединены с третьим и четвертым входами блока управлении, источник входного сигнала, выход которого подключен к второму входу первого компаратора, введены инвертор, сумматор по модулю два, аналоговый сумматор, формирователь кода и блок уставки, выход которого подключен к первому входу аналогового сумматора, второй вход которого через инвертор соединен с выходом источника входного сигнала, а выход подключен к втому входу второго компаратора, выход которого соединен с первым входом сумматора по модулю два, второй вход KOi oporo подключен к выходу первого компаратора, а выход соединен с вторым входом распределителя и первым входом формирователя кодов, второй вход которого соединен с выходом первого регистра цифроаналогового преобразователя. На чертеже представлена функциональная схема адаптивного АЦП, в состав которого входят источник 1 входного сигнала, компараторы 2 и б, инвертор 3, аналоговый сумматор 4, блок 5 уставки, ЦАПы 7 и 14 обратной связи, сумматор 8 по модулю два, блок 9 управления, распределитель 10, генератор 11, регистры 12 и 13 ЦАП, формирователь 15 кода. Выход источника 1 выходного сигнала подключен к первому входу компаратора 2 и через инвертор 3 к первому входу аналогового сумматора 4, Второй вход этого сумматора соединен с выходом блока 5 уставки, а выход с первым входом компаратора 6. К второму входу последнего подключен выход ЦАП 7. Вьлход компаратора б соединен с первым входом сумматора по модулю два 8 и с первым входом блока 9 управления регистрами ЦАП, к второму входу которого подключен распределитель 10, первый вход которого соединен с выходом генератора 11. Первый и второй выходы блока 9 через регистры 12 и 13 подключены к ЦАП 7 и 14 соответственно. Выход регистра 13 соединен с первым входом формирователя 15 кода, к .вто рому входу которого подключен второ вход распределителя 10 и выход сумматора 8 по модулю два, к второму входу которого подключен выход компаратора 2 третьего входа блока 9 управления. Рабога АЦП осуществляется в следующей последовательности. Сигнал Цц от источника 1 сигнал поступает на первый вход компаратора 2 и через инвертор 3 на первый вход сумматора 4, на второй вход ко торого с блока 5 поступает сигнал {, равный величине предела преобра зования АДП. С выхода сумматора 4 сигнал Urt,-Ux поступает на первый вход компаратора б. Формирование цифровых эквивалентов величин U и UPJ-UX, поступающих на входы компара торов 2 и 6, Осуществляется по изве ному алгоритму последовательного приближения (поразрядного кодирования), Суть его состоит в том, что входные сигналы последовательно ср ниваются с компенсирующей суммой, формируемой из 1/2, 1/4, 1/8,... ве личины возможного максимального зна чения . Распределитель 10с помощью генератора 11 через блок 9 управления осуществляет поочередное введение разрядов каждого регистра ЦАП 1 и 13, которые подключают соответству щие веса ЦАП 7 и 14, настроенные по ранее указанному закону. Компараторы 2 и б для нарастающего и убывающего входного сигнала U настроены таким образом, что выполняются условия;. fl ,если -10, если Ux , Г1, если .а 10, если U,i Uu „; п Ut..Le6;Ui, i- В рассматриваемом случае каждый компаратор имеет зону гистерезиса, равную величине кванта « . В процессе формирования цифрового эквивалента UK с выходов компараторов будут поступать взаимно противоположные сигналы, в результате в регистрах 13 и 12 формируются прямые и обратные коды. Для случая. 5, кванта, ,5 кванта данные представлены в табл. 1. Отличительной особенностью работы предлагаемого устройства является то, что момент уравновешивания (компенсации) входной величины УХ с точностью до одного кванта может наступить на одном из тактов в процессе преобразования. Признаком atoro является совпадение информации на выходах компараторов.. Для случая .п 5, t/n,33 кванта. ,5 кванта, данные Представлены в табл. 1. Как видно из примера, на втором такте наступает уравновешивание входной величины и процесс преобразования можно прекратить. Появление двух единиц на выходах компараторов 2 и б является признаком окончания кодирования. На выходах сумматора 8 появится сигнал, по которому с формирователя 15 кодов осуществляется списывание информации и запуск распределителя 10 для обработки новой информации. В табл. 2 представлена зависимость количества комбинаций К, равномерно распределенных п-разрядных кодов в процентах, в которых возможно сократитьвремя преобразования. Технико-экономический эффект заключается в том, что в предлагаемом устройстве можно обеспечить также исправление ошибок, вызванных отка- зом одного из компараторов цепей управления ЦАП. В этом случае при появлении двух единиц на выходах комараторов в дальнейших тактах должно соб податься условие инверсии их выходных сигналов. Несоблюдение этого условия является признаком сбоя и съем информации должен осуществляться с канала, выполняк«цего правильное одирование. Таблица

Таблица2

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналого-цифровой преобразователь | 1982 |

|

SU1091331A1 |

| Устройство для контроля аналого-цифрового преобразователя | 1986 |

|

SU1585897A1 |

| Аналого-цифровой преобразователь в код системы остаточных классов | 1991 |

|

SU1797158A1 |

| Устройство управления | 1984 |

|

SU1229721A1 |

| Биполярный аналого-цифровой преобразователь | 1987 |

|

SU1520658A1 |

| Аналого-цифровой преобразователь | 1979 |

|

SU839046A1 |

| Устройство для измерения времени установления выходного напряжения цифроаналоговых преобразователей | 1986 |

|

SU1332530A1 |

| Аналого-цифровой преобразователь | 1986 |

|

SU1378061A1 |

| Преобразователь угла поворота вала в код | 1987 |

|

SU1425832A1 |

| МНОГОМЕРНЫЙ СТАТИСТИЧЕСКИЙ АНАЛИЗАТОР ВЫБРОСОВ И ПРОВАЛОВ НЕСТАЦИОНАРНОГО НАПРЯЖЕНИЯ | 2000 |

|

RU2189631C2 |

АНАЛОГО-ЦИФРСЖОЙ ПРЕОБРАЗОВАТЕЛЬ, содержащий генератор, выход которого подключен к первому входу распределителя, первый и второй выходы которого Через блок управления соединены с входами Первого и второго, регистров ци №ю-аналоговых преобразователей соответственно, выходы которых через первый и второй цифроаналоговйе пресзбразователи подключены соответственно к первым входам первого и второго компараторов, выходы которых с третьим и четвертым входами блока упргшления, источник входного сигнала, выход которого подключен к второму входу первого компаратора, отличающийся тем, что, с целью сокращения среднего времени преобразования, в негр введены инвертор, сумматор по модулю два, аналоговый сумматор, формирователь кода и блок уставки, т:1ход которого подключен к первому входу аналогового сумматора, второй вход которого через инвертор соединен с выходом источника входного сигнала, a выход подключен к второму входу второго ком паратора, заход, которого соединен с (Л первьм входом сумматора по модулю два, второй вход которого подключен к выходу первого компаратора, a ШХод соединен с вторым входом распределителя и первым входом фо Ашррвателя g кодов второй вход KOTOpoio соединен с ккодом первого регистра цифрюаналогового преобразователя. 00 а о эо

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Гитис Э.И | |||

| Преобразователи информации для электронных цифровых вычислительных устройств | |||

| М., Энергия, 1975, ci 298 | |||

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1984-03-07—Публикация

1982-05-24—Подача