(54) ЭЛЕКТРОННОЕ МОДЕЛИРУЮЩЕЕ УСТРОЙСТВО

| название | год | авторы | номер документа |

|---|---|---|---|

| Квадратор | 1982 |

|

SU1103247A1 |

| Самонастраивающаяся система автоматического управления для объектов с запаздыванием | 1981 |

|

SU1173390A1 |

| Устройство для автоматического управления активной мощностью гидроагрегата | 1984 |

|

SU1192097A1 |

| Устройство автоматического регулирования толщины полосы на непрерывном прокатном стане | 1987 |

|

SU1435347A1 |

| Устройство для регулирования оптической плотности красочных полиграфических знаков к многокрасочным печатным машинам | 1981 |

|

SU1014767A1 |

| Устройство для моделирования звена с распределенными параметрами | 1972 |

|

SU452014A1 |

| Система управления пресс-гранулятором | 1984 |

|

SU1194690A1 |

| Регулятор | 1987 |

|

SU1425599A1 |

| Устройство для определения постоянных времени нестационарных инерционных звеньев | 1974 |

|

SU551613A1 |

| Частотно-регулируемый асинхронный электропривод | 1983 |

|

SU1119155A1 |

1

Изобретение относится к эпектронным 1 устройствам для моделирования различных .технологических процессов.

Известно электронное моделирующее .устройство, содержащее последовательно

включенные инерционные блоки, интеграторы, блоки запаздьшания, резисторы и суммиругошие усилители.

Однако такое устройство не позволяет исследовать смещение красок при печатании

Предложенное устройство позволяет расширить класс задач, решаемых с его помощью,: в частности позволяет моделироват технологические процессы смещения красок на ленте при различных возмущениях в лёнтопроводящих системах рулонных, ротационных, печатных машин.

Это достигается тем, что в предложенном устройстве входы интеграторов подключены к входной клемме и выходам соответствующих инерционных блоков. Выходы интеграторов, кроме последнего, присоединены ко входам соответствующих ,блоI ков запаздывания, каждый из которых под-хлючен через резисторы к входам предыдущего, соответствующего и следующего i суммирующих усилителей. Выход последнего интегратора подключен через резисторы к входам предьздущего и соответствующего ему суммирующих усилителей и к входу суммирующего усилителя, присоединенного через резистор к выходу первого блока запаздывания.

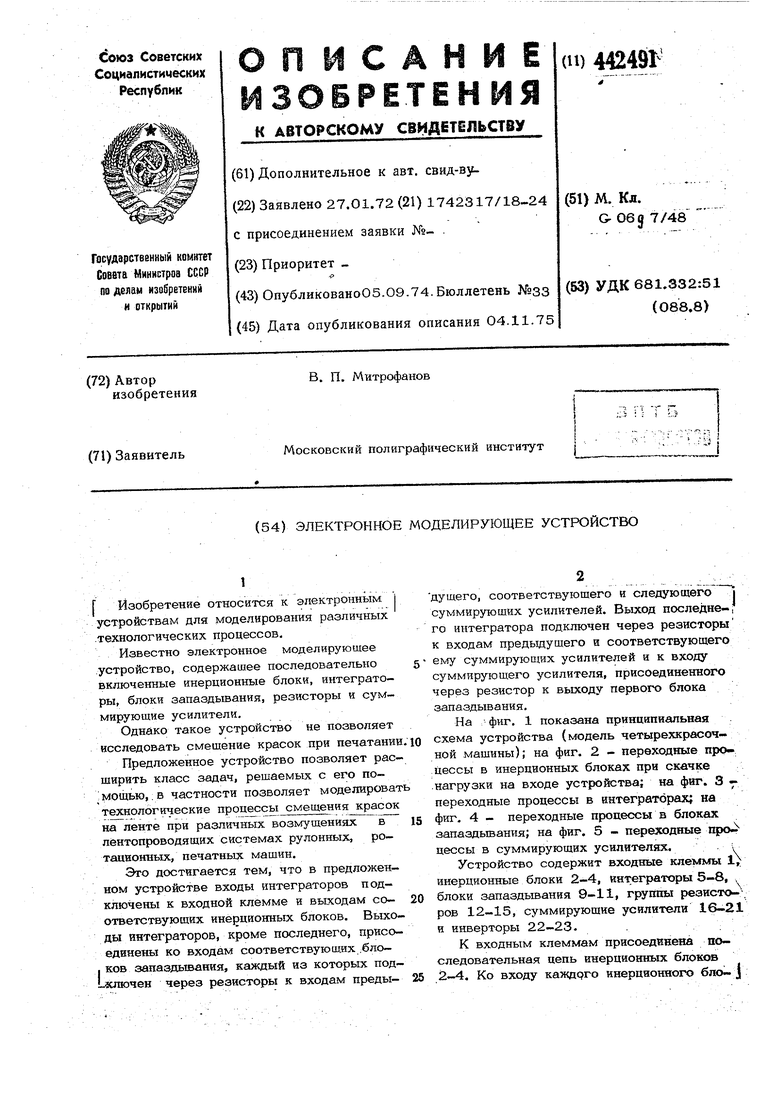

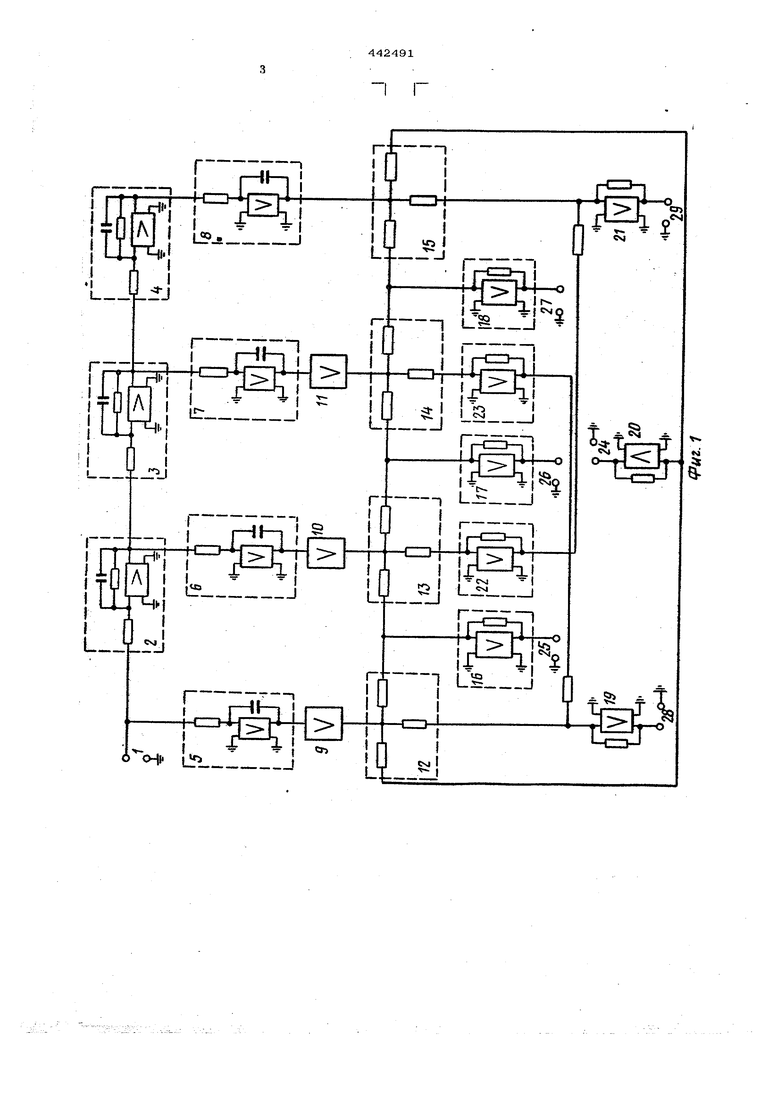

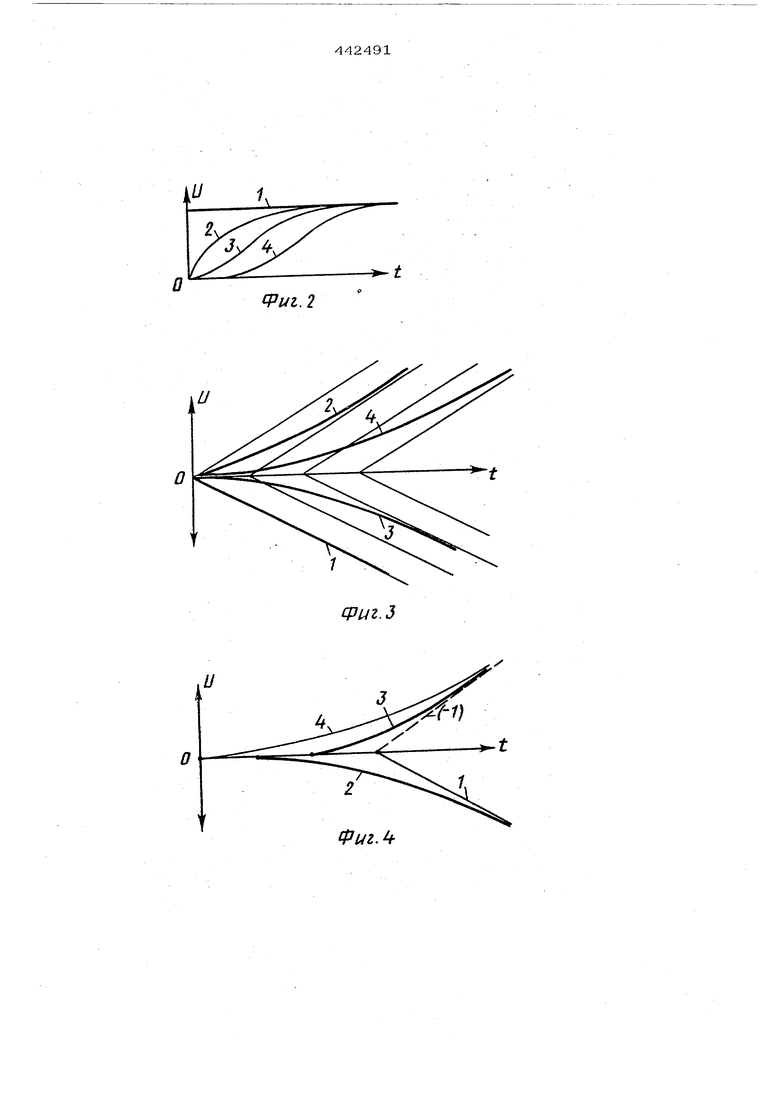

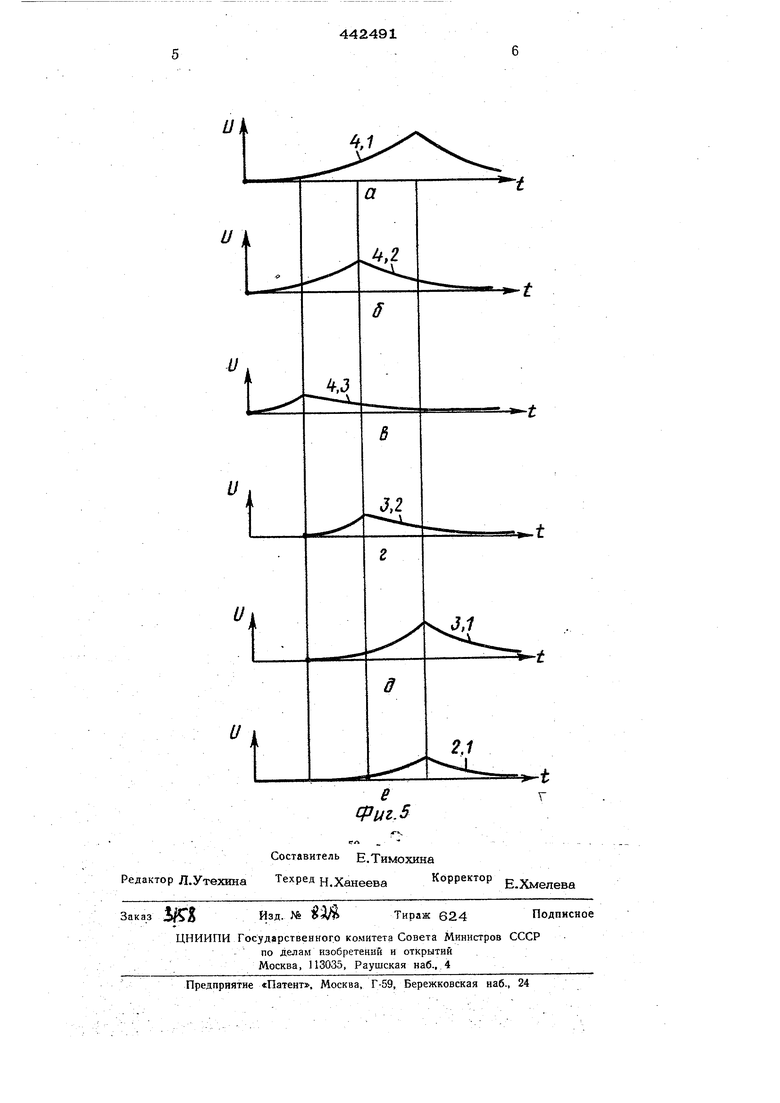

На фиг, 1 показана принципиальная схема устройства (модель четырехкрасочной машины); на фиг. 2 - переходные про Цессы в инерционных блоках при скачке нагрузки на входе устройства; на фиг. 3 - переходные процессы в интеграторах; на фиг. 4 переходные процессы в блоках запаздьтания; на фиг, 5 - переходные npoJ цессы в суммирующих усипителях.. ,

Устройство содержит входные клеммы 1 инерционные блоки 2-4, интеграторы 5-8, блоки запаздывания 9-11, группы резисто-; ров 12-15, суммирующие усилители 16-21 и инверторы 22-23.

К входным клеммам присоединена последовательная цепь инерционных блоков 2-4, Ко входу каждрго инерционного бло-j 1ка и к выходу последнего присоединены интеграторы 5-8, к выходам которых (кроме последнего), подключены блоки чистого запаздывания 9-11. Выходы каждого блока запаздьшания и интегратора 8 через резисторы соединены с соответствующими суммирующими усилителями. Причем пары выходов групп резисторов 12 и 14, 13 и 15 связаны между собой через инверторы 22 23 к присоединены соответственно к суммирующим усилителям 21 и 19. Каждая группа 12-15 содержит три резистора. При модулировании большего числа печатных секций их число на еди I ницу меньше, чем число печатных секций. Работа устройства поясняется графиками на фиг. 2-5 при частном случае возму щения в виде скачка нагрузки на его входе. На выходе инерционных блоков процессы характеризуют изменение относительной деформации ленты между соответствующими печатными секциями (фиг. 2). Причем постоянные времени блоков 2-4 равны или пропорциональны времени перемещения ленты мемаду соответствующими печатными секциями. На выходе интеграторов процессы характеризуются кривыми (фиг. З), имеющими различную полярность вследствие прохождения сигналов через четное (или нечетное число каскадов усиления. В реальной системе эти кривые для рассматриваемого примера одного знака и характе ризуют см.ещеиие красок относительно ранее нанесенных на ленте меток при ее постоянном натяжении. Блоки запаздыват1ия осуществляют чистый сдвиг сигналов (фиг, 4) изображенных на фиг. 3. Причем время Чистого запаздывания блока 11 равно постоянной времени блока 4, время чистого запаздывания блока 1О - сумме постоянных времени блоков 3 и 4, время чистого запаздывания блока 9 - сумме постоянных времени всех инерционных блоков. С блоков запаздывания сигналы поступа- }ют на суммирующие усилители. Причем сиг .нaлы с одинаковыми знаками суммируются через инверторы 22, 23. На клеммах , 24 получают натяжение U пропорциО- . нальное величине несовмещения между четвертой и первой красками (фиг. 5, а), на клеммах 25, 26, 27 - напряжение. пропорциональное величине несовмещения между второй и первой (фиг. 5. е), третьей и второй (фиг. 5, г), четвертой и третьей (фиг. 5, в) красками. На клеммах 28 и 29 напряжение характеризует TeKyaiee несовмещение между третьей . и первой (фиг. 5, д) и четвертой и второй фиг. 5, б) красками. Таким образом, возможно наблюдение за текущими несовмещениями между каждой краской относительно другой. Входные воймущения могут быть различными. Подавая дополнительные врзму- .--., .. /. . щения на пррмежуточные участки между блоками 2-4, например соответствующие возмущениям в реальной системе и вызванные перестановкой регистровых механизмов в машине, биениями цилиндров и другими известными причинами, на этой модели можно исследовать различные комбинации процессов, происходящих в лентопроводящей системе рулонной ротационной печатной машины. Устройство может быть использовано при отладке регуляторов регистра, которые (или их модели) подключаются к описываемой модели. Предмет изобретения Электронное моделирующее устройство, содержащее последовательно включенные инерционные блоки, интеграторы, блоки запаздывания, резисторы и суммирующие усилители, отличающееся тем, что, с целью расширения класса решаемых задач, в нем входы интеграторов подключены к входной клемме и выходам соответствующих инерционных блоков; выходы интеграторов, кроме последнего, присоединены ко входам соответствующих блоков запаздывания, каждый из которых подключен через три резистора ко входам предьщущего, соответствующего и следующего суммиру щ х усилителе й;выxQд п леднeгoинтегратора подключен через резисторы ко входам предыдущего и соответствующего ему суммирующих усилителей и ко входу суммирующего усилителя, присоединенного через резистор к выходу первого блока за-, паздывания.

Vut.2

и

О

Фиг.З

и

Ul

и

Авторы

Даты

1974-09-05—Публикация

1972-01-27—Подача