Изобретение относится к обд сти вычислительной техники и может быть использовано в вычислительыых ыешинах, работающих с каналами связи (в частности, в системах резервирования и прода жи билетов на поезда и самолеты, бронирования мест i гостиницах и т.д.).

Известны устройства для управления обменом информацией между электронной вычислительной машиной (ЭВМ) и каналами связи, содержащие буферный регистр, соединенный с первым и вторым входовыходами устройства, с первым и вторым узлами обмена, счетчик знаков, связанный с узлом а11ализа с первым узлом обмена и с первым выходом устройства, коммутатор каналов связи, соединенный с третьим входо-выходом устройства, со вторым узлом обмена, с узлом опроса каналов связи, две схемы совпадения и две схемы сборки, связанны(5 с триггером занятости.

{триггер заполнения буфера запроса, триггер заполнения буфера ответа, триггер режима запроса, блок выборки режима опроса каналов связи, связанный с узлом опроса каналов связи, блок выборки режима ответа и блок выборки режима запроса, связанные с первым узлом обмена,

Недостатками известных

0 устройств являются сложность, необходимость больших областей памяти для размещения информации от кана лов связи и частные прерывания работы процессора.

5

Целью изобретения является упрощение устройства и повышение его пропускной способности, а именно сокращение оборудования, реализующего совпадение обработки массива информации i-ro запроса с выдачей массива информации no(L-i)Mi) запросу и с приемом массива информации no(i-n}-n запросу, и уменьшение количества |11 ереходов к управляющей программе

после завершения очерадног массива информации

Пос1саЕленыая цель достигаеЕСЯ тем5 что устройство содержио} третью схему совпадения-; первый вход которой связан с Лггп}и ы Бхоа,ом уотрЬйстБЗ.д втором ВХОД соедй1.ен

с единичным выходом шркггера заполнения буфера запроса 1ретий вход соединен с нулевым выходом триггера заполнения буфера ствета ;, а выход соединен со вторым выходом устройства, нулевые выходи триггеров режима запроса, Заполнения запроса, заполнения буфера отввта ооединеМА о соответствующими ь ход а ми бло ка : 1ысорки режима опроса каналов СБИЗИе Входы блока Бнборкж режима отьета сойдиненн п адйиичнш зыходом триггера 8LiipjiJiOT-:vif; буфера ответа и нулсБЫм ;в5.1ходоы тр ггтера режима запросе 5 едииичкий БЫХОД которого свпзан с блоком ъыборки режима ЗЕПроса, нулеьий вход триггера заполнейИШ буйора ойпрогоиотБа -у единичгилм пи о третьим кыхидо ; ТНЙЕХОД KOTOpovn сгг:;;..-: iiH4iiHM; :йхи;-.пмб ;миггй;; я буфера о Флота. На Ojbij: J 1.р.и;:.едэнр :х;„йг.;п-;yoTpoiCTjp.: w.: ;1;Нл ijypR .;4i;-4 -/отро-лхгХи:

за .ВрО;.И31:.-;.Я;:Т ДЧ..;/:. Х .;

НИВ хомаид;; х: у). -

ДЛсч lOjriM;-Xi pSOiJTH ,-: jrUX;

на фиг,, Да jipcxo-i-u р/1оты процессора в i:;

БрвМСНИйЯ ДуШХрЗЫМЙ 0 Xf,iBJi,duHH

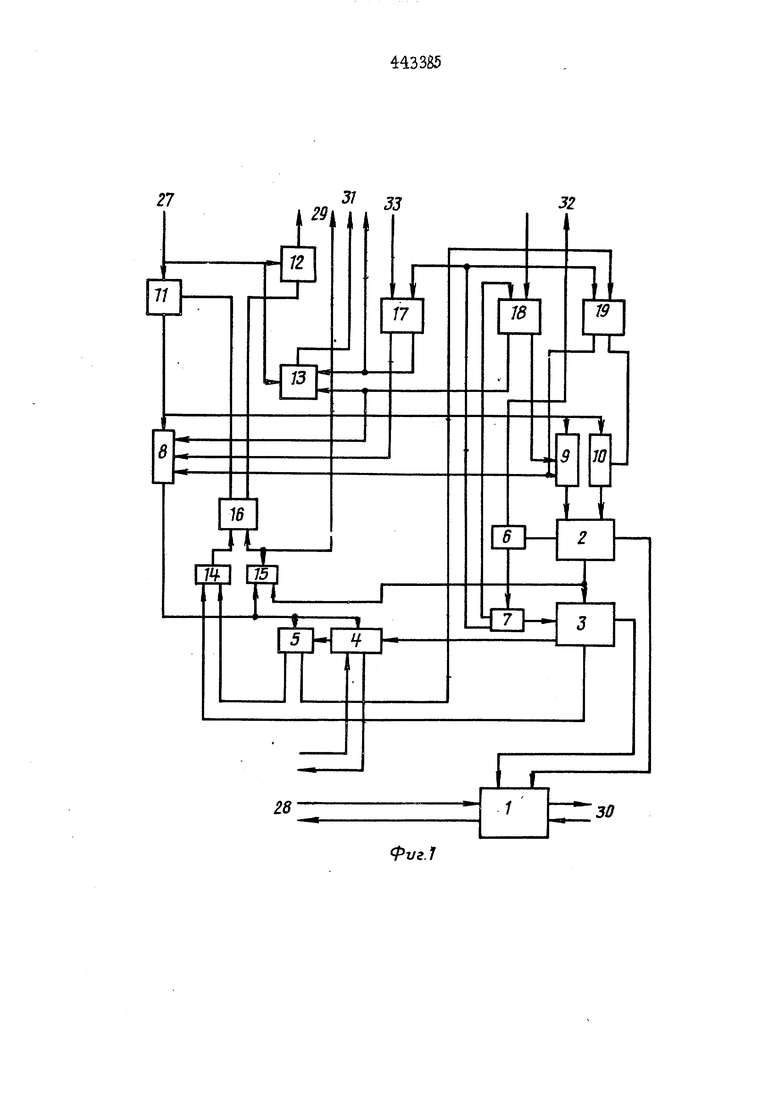

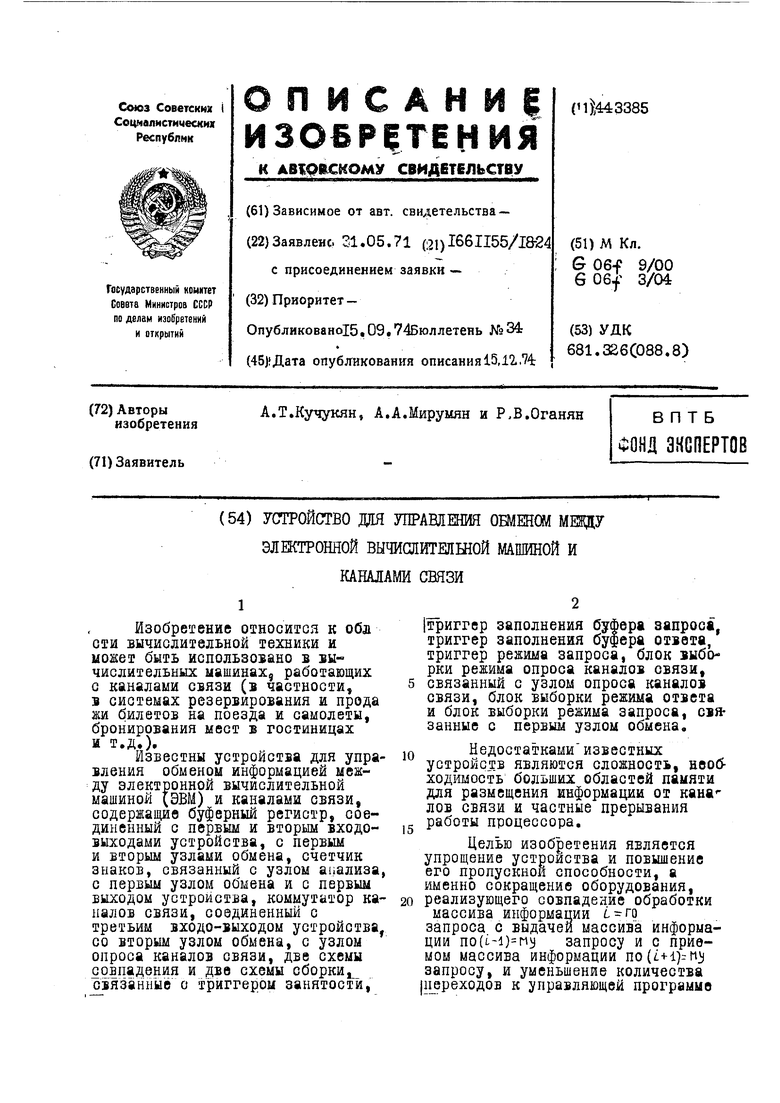

УстроистБО содер хх бушериы регистр 1.. перБьш уЗди г обмена

БТОрОЙ узёл 3 ибУаТЛХ: ЛUJ/iyTaTOp

k калалоБ овяаи,, узел Ь опроса чонелов свяви, охетчкл зианоБ б ysQv, У анализа., блок 8 выборки рбкима опроса „блок / режима ответа 5 блох I. режима saiipoca охоыы дениЯ; схакл 14 и 13

ТрИхТСр л5 ЯУЧЛТУСТИ;

заполнения буихнш очп .Ш заполнения буфера

.( ОЯУ для saiipocixxx лассиза иьл|;0р1у1ации Б формате маи1як1;нх сз буф ел ОЗУ для ЗЕПчосиого ыасси so/ иац;орла дии с разме цеиием по 311акйу,ббуфер 22 ОаУ ./лш ответного массива информации о размещени ио снакаМ| буферные ЗУ 23 каналов :вноИ,, каналъб связи Pl-j арыФмйТй™ .й рогисчгр iir;0i:i6: copi

4

уотройсето 26 ДЛЯ упраБлеыйя об.iMSHOMs

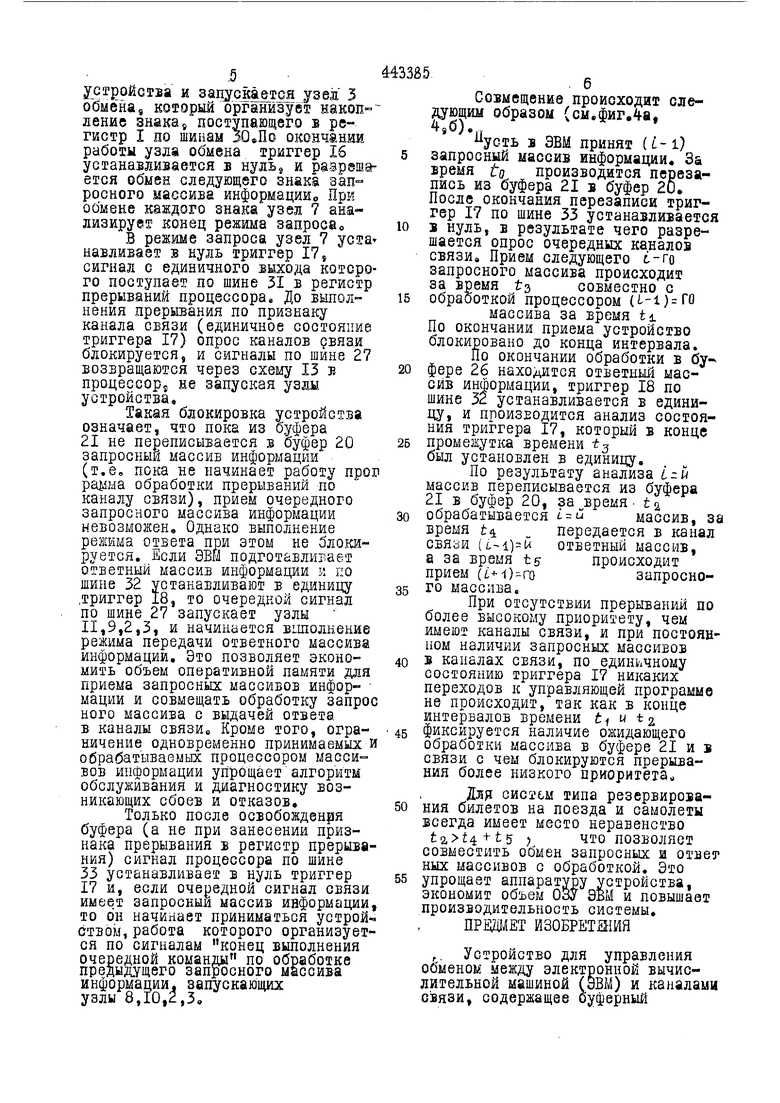

Кроме того на фиг. За, б приведены следующие обозначения :

f{, f ../KXf ) -

Ерейя выполнения команд процессоpej г- -время обмена знака между устройством и процессором, t время обмена знака между устройством и каналом ОБЯЗИ.

Устройство работает следующим; -образом

: Работа устройства организует-оя по сигналу конец выполнения очередной команды, поступающего по шине 27 Этот сигнал запускает устройство, если триггер 16 находится в нулевом состоянии, В зависимости от состояния триггеров 1719 запускается один из трех блоков 8-10в

Если устройство до этого не находилось в режиме обмена (запроса ими ответа) с каналом связи, . т,е« триггера 18 и 19 находятся 3 нулевом состоянии, то сигнал проходит через блок 8 и узел 5 и организует опрос очередного канала связи Но коду коыыутатора Ф выбирается канал связи и проверяется готовность канала связи к передаче запросного массива инфсрмацик по шине 28 в регистр I

Через схему 15 с соответсгвую ,ей задержкой Б блоке 8 устаиаБливается Б единицу триггер 16 (блокируется вход устройства) и по шине 29 выдается сигнал на продолжение работы процессора. Это позволяет избежать потери Бремени процессора, неизбежные в случа13 такой организации работы устройства, когда ожидается результат работы узла 5 о

Если результат опроса канала СБЯЗИ положительный, то первый 1ЫХОД узле 5 устанавливает Б единину триггер 19 (т.е. разрешается выполнение режима запроса) , Второй 13ЫХОД узла 5 при любом исходе опроса устанавливает Б нуль триггер 16, открывая доступ к устройся ву очередного сигнала по шине 27о

При очередном сигнале по шине 2 работает цепь узлов 11,10, 2уЗ. Узел 2 обмена организуен передачу знака (байта, т.е, девятиразрядного кода) из регистра I по шинам 30 Б процессор, а Б счетчике б ведется п одсчет знаков. Сигнал окончания работы узла 2 обмена через схему 15 поступает на шину 29 для выполнения очередной команды. Блокируется вход 5 . устройства и запускается узел 3 обмена J который ор1ганйзу1 5т накопление знака, поступающего в регистр I по шинам окончании работы узла обмена триггер 16 устанавливается в нуль5 и раареша ется обмен следующего знак® запросного массива информациио При оомене каждого знака узел 7 анализирует конец режима запроса, В режиме запроса узел 7 уста навливает в нуль триггер 17, сигнал с единичного выхода которо го поступает по шине 51 в регистр прерываний процессора. До выполнения прерывания по признаку канала СБЯЗИ (единичное состояние триггера 17) опрос каналов двяаи блокируется, и сигналы по шине 27 возвращаются через схему 13 Б процессор, не запуская узлы устройства. Такая блокировка устройства означает, что пока из буфера 21 не переписывается в буфер 20 запросный массив информации (т.а, пока не начинает работу про pajdHa обработки прерыБаний по каналу связи), прием очередного запросного массива информации невозможен. Однако выполнение режима ответа при этом не блокируется. ЕСЛИ ЭБЬ1 подготаБлир.ает ответный массив информации и по шине 32 устанавливают в единицу .триггер 18, то очередной сигнал по шине 27 запускает узлы 11,9,2,3, и начинается вьшолнение режима передачи ответного массива информа ции. Это позволяет экономить объем оперативной памяти для приема запросных массивов информации и совмещать обработку запро ного массива с выдачей ответа в каналы связи Кроме того, ограничение одновременно принимаемых обрабатываемых процессором массивов информации упрощает алгоритм обслуживания и диагностику возникающих сбоев и отказов. Только после освобождения буфера (а не при занесении признака прерывания в регистр прерыва ния) сигнал процессора по шине 33 устанавливает в нуль триггер I, если очередной сигнал связи имеет запросный массив информации то он начинает приниматься устрой ством, работа которого организует ся по сигналам конец выполнения очередной команды по обработке предыдущего запросного массива информации, запускающих узлы 8,10,2,3, Совмещение происходит следующим образом (см,$иг,4а, 496). усть в ЭВМ принят (L-1) запросный массив информации. За время to производится перезапись из буфера 21 Б буфер 20. После окончания перезаписи триггер Г по шине 33 устаназливается S нуль, в результате чего разрешается опрос очередных каналов связи Прием следующего t-ro запросного массива происходит за время tg совместно с обработкой процессором (Li)ro массива за время ti По окончании приема устройство блокировано до конца интервала. По окончании обработки в буфере 26 находится ответный массив информации, триггер 18 по шине 32 устанавливается в единицу, и производится анализ состояния триггера 17, который в конце промежутка времени t был установлен в единицу. По результату анализа i-й массив переписывается из буфера 21 в буфер 20, за время, t i-- массив, за обрабатывается время to, передается в канал связи (L-I)U ответный массив, а за время t5 происходит прием (i-bi) запросного массива. При отсутствии прерываний по более высокому приоритету, чем имеют каналы связи, и при постоянном наличии запросных массивов в каналах связи, по единичному состоянию триггера 17 никаких переходов к управляющей программе не происходит, так как в конце интервалов времени t и ±2. фиксируется наличие ожидающего обработки массива в буфера 21 и s связи с чем блокируются прерывания более низкого приоритета Для систем типа резервирования билетов на поезда и самолеты всегда имеет место неравенство ,t + t5 ч что позволяет совместить обмен запросных и ответ ных массивов с обработкой. Это упрощает аппаратуру устройства, экономит объем ОЗУ ЭМ и повышает производительность системы, ПРЩ1ЛЕТ ИЗОБРЕТаШЯ ,. Устройство для управления обменом между электронной вычислительной машиной (ЭВМ) и каналами , содержащее буферный регистр,соединённый с первым и вторым входо-выходами устройства, с первым и вторым узлами обмена, счетчик знаковS связанный о уз лом анализаJ с первым узлом обмена и с первым выходом устройсг ва; коммутатор каналов связи9 соединенный с третьим входо-выходом устройства, со вторым узлом обмена, с узлом опроса каналов связш, две схемы совпадения и две схемы сборки, связанные с триггером занятости , триггер заполнения бу Фер1 запроса, триггер заполнения буфера ответа, триггер режима запроса, блок выборки режима опроса каналов связи, связанный с узлом опроса каналов связи, блок выборки режима ответа и блок выбор ки режима запроса, связанные с первым узлом обмена, отличающееся тем, что с целью упрощения устройства и повышения его пропускной способ™ ности оно содержит третью схему совпадения, первый вход которой 5 связан с первым входом устройства,; второй вход соединен с единичным выходом триггера заполнения буфе:ра запроса, третий вход соединен с нулевым выходом триггера заполнения буфера ответа, а выход соединен со вторым выходом устройствг нулевые выходы триггеров режима запроса, заполнения буфера запроса, заполнения буфера ответа соединены с соответствующими входа ми олока выборки режима опроса каналов связи, входы блока выборки режима ответа соединены с единич,ным выходом триггера заполнения буфера ответа и нулевым выходом триггера режима запроса, единичный выход которого связан о блоком выборки режима запроса, нулевой вход триггера заполнения буфера запроса соединен, со вторым входом устройства, а единичный выход связан с третьим выходом устройства , третий вход которого соединен с единичным входом триггера заполнения буфера ответа

31

2f

29

32

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для управления вводом-выводом | 1989 |

|

SU1735859A1 |

| Мультиплексное устройство для обмена информацией | 1983 |

|

SU1157546A1 |

| Система ввода-вывода для микропрограммируемой ЭВМ | 1988 |

|

SU1667084A1 |

| Устройство для обмена информацией | 1982 |

|

SU1048468A1 |

| Адаптивная система обработки данных | 1987 |

|

SU1455342A1 |

| Устройство для обмена информацией между цифровой вычислительной машиной и внешними устройствами | 1981 |

|

SU1003066A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЦВМ С КАНАЛОМ СВЯЗИ | 1991 |

|

RU2011217C1 |

| Адаптивное устройство для сопряжения ЭВМ с каналами связи | 1987 |

|

SU1532938A1 |

| Устройство для сопряжения каналов передачи данных с ЭВМ | 1985 |

|

SU1226476A1 |

| Устройство для обмена данными | 1984 |

|

SU1239724A2 |

71

19

18

17

W

LI

Jj28

ля30

ffve.f

1ч ш

U И- И+5 .2

Авторы

Даты

1974-09-15—Публикация

1971-05-31—Подача