1

Изобретение относится к вычислительной технике.

Известно частотно- импулъсное множительно-делителъное устройство, содеркащее первый и второй делители частоты,первый триггер и первую схему совпадения.

Однако в известном устройстве при преобразовании получаются значительные погрешности,вызванные тем,что время пропускания первой схемы совпадения имеет случайную составляющую,обусловленную ее управлением.

Цель изобретения-повысить точность работы устройства.

Это достигается тем.что в устройство введены второй триггер, вторая и третья схемы совпадения; причем выход первого делителя частоты соединен с единичным входом второго триггера,нулевой вход которого соединен с нулевым входом второго делителя частоты,выI ходсш второй схемы совпадения и

нулевым входом первого триггера,

единичный выход второго триггера

соединен с управляющим входом -i

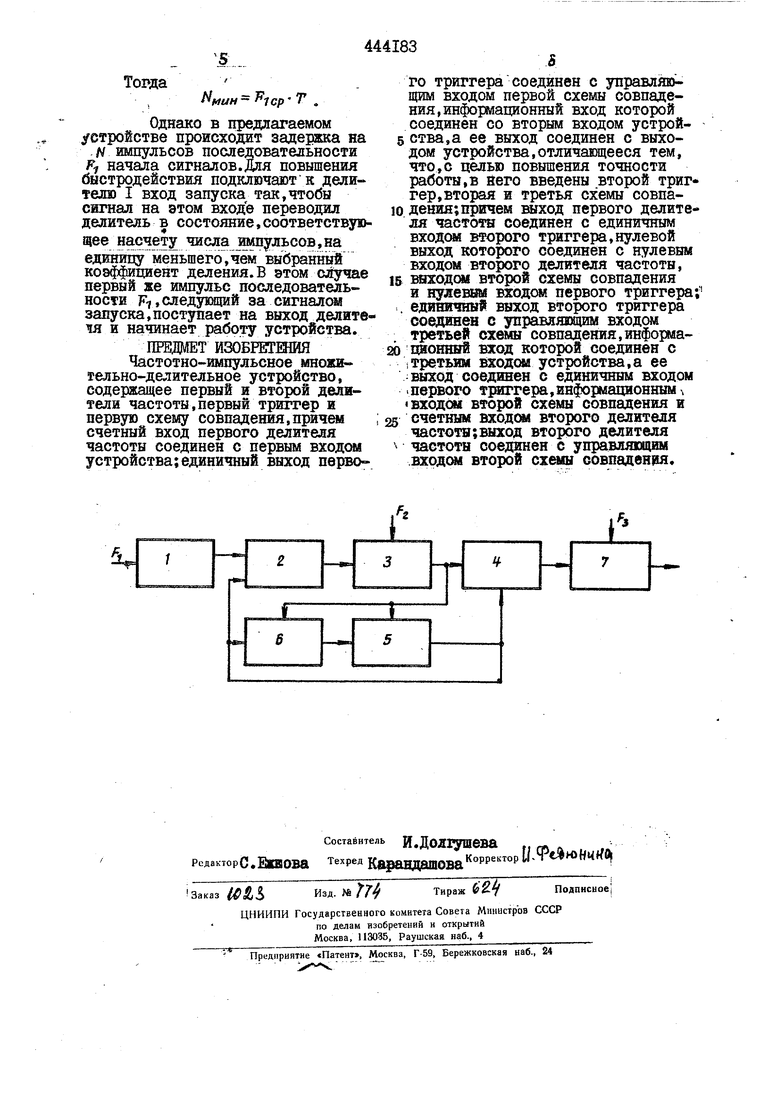

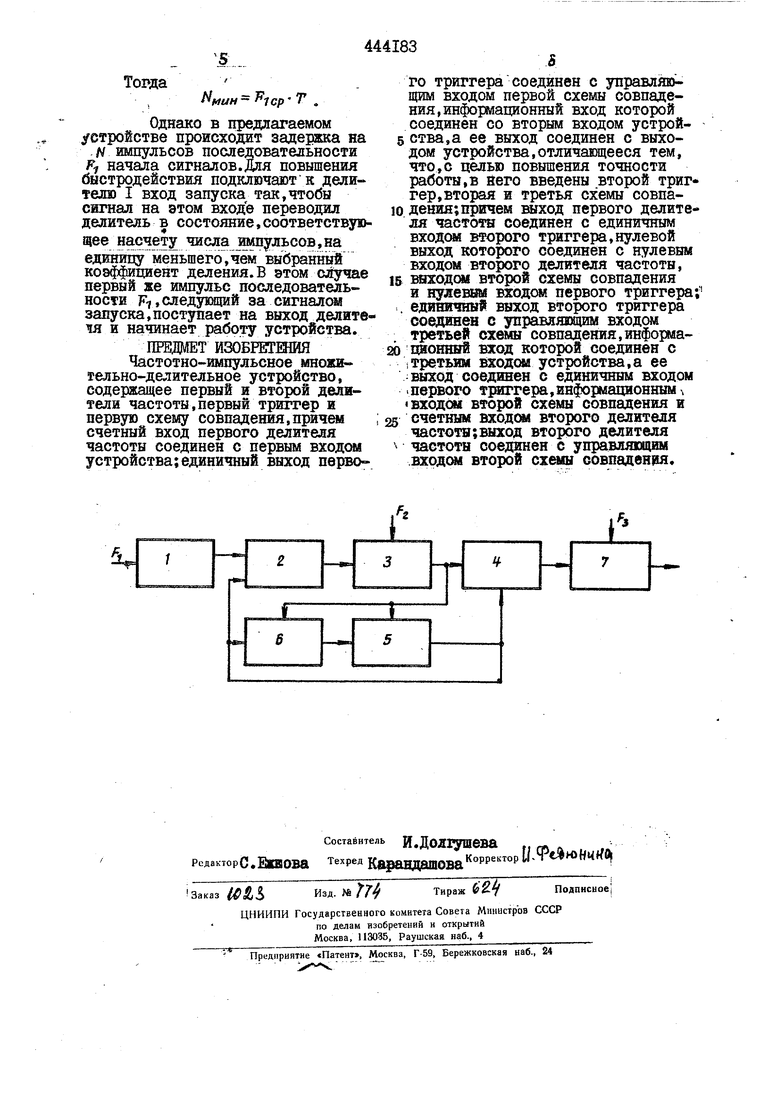

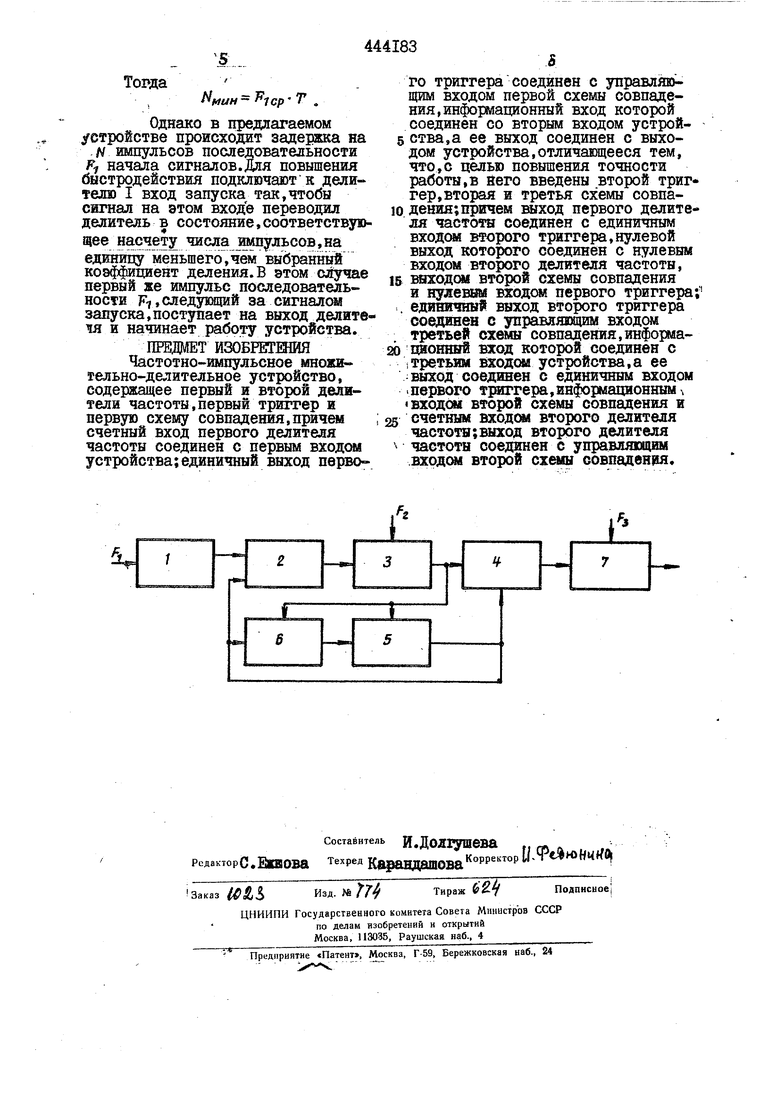

. третьей схемы совпадения информа5 ционный вход которой-соединен с третьим входом всего устройства а ее выход соединен с единичным входом первого триггера,инфоряационным входом второй схемы совпадеш ния и счетным входом второго делителя частоты выход второго делителя частоты соединен с управляюа1им входом второй схемы совпадения. На чертеже дана блок-схема

15 предлагаемого устройства.

Устройство состоит из делителя I частоты следования импульсов, вход которого является входом мно;жителя (сигнала частоты Ft )«а вы20ХОД подключен к единичному входу : триггера 2,единичный выход которого в свою очередь подключен к потенциальному входу схемыр совпадения. На второй вход схемы 3 сов25 радения подключен делителя. (сигнал частоты Рг ),а выход схемы 3 - JK единичному входу триггер 4,к импульсному входу схемы 5 сов падения и через делитель 6 частот следования импульсов к потенциаль HOJ/QT входу схемы 5.Выход схемы 5 совпадения подключен к нулевым вх дам триггеров 2 и 4 и к цепям сбр са делителя частоты 6.Единичный выход триггера 4 подключен к поте циальному входу схемы 7 совпадени на импульсный вход которой прступа ёт сиг нал множимого (сигнал частоты Кз ).а выход является выходом устройства.Оба делителя частоты (I и 6) имеют один и тот же коэффициент деления,равный Ы , но делитель 6,кроме того,имеет цепи сброса,при подаче импульсного сигнала на которые делжтель пе реходит в 11сходное нулевое положение. В исходном состоянии триггеры 2 и 4 находятся в нулевом положении, при котором схемы 3 и 7 совпадения заперты.Оба делителя также находятся в исходном нулевом состоянии,при этом схема 5 совпадения заперта низким потенциалом,снимаемым с последней ячей ки делителя 6, При подаче на все три входа устройства сигналов соответствующих частот Р,,Р2И РЗ,после того, как на вход делителя I поступит Н -ш импульс последовательности F ,на выходе делителя I получается сигнал переполнения,которы поступает на единичный вход триггера 2 и перебрасывает его в единичное состояние,при котором открывается схема 3 совпадения. Первый же сигнал,который прошел через схему 3,поступает на единичный вход триггера 4 и перебрасывает его в единичное состояние, при котором открывается схема 7 совпадения,и импульсы последовательности PS начинают поступать на выход устройства. Импульсы последовательности 2 с выхода схемы 3 совпадения поступают на делитель частоты 6, где подсчитываются,: и при поступ лении р -го импульса последовательности Яг (этот импульс появляется через р-1 периодов последовательности Fj после момента отпирания схемы совпадения 7) на выходе делителя 6 появляется потенциал , открывающий схему совпаде кия 5. Следущий за втим Р+1 импульс последовательности F проходит через схему совпадения 5, действуя на нулевые входы триггеров 2 и 4,и переводит их в нулевое состояние.При STOM схемы 3 и 7 совпадения запираются,сигнал на выходе устройства временно прекра-: щается. Одновременно с поступление на нулевые входы триггеров 2 и 4 сигнал с выхода схемы 5; поступает на цепи сброса делителя 6 и переводит его в исходное нулевое - г состояние,при котором на выходе делителя имеется низкий потенщал, который запирает схему 5 и,все устройство (за исключением делитетеля I) находится в исходном состоянии. После прихода следующего импульса с делителя I процесс повторяется. Таким образом схема 7 совпадения открывается через каждые л/ периодов последовательности /г и остается открытой в течении интервала времени,равного периодам последовательности Рг .в течении которого на выход следуют импульсы последовательности Fj. Среднее значение выходной частоты в устройстве определяется из условия: еы 7 Ty длительность интервала,в течении которого открывается схема 7 совпадения (она равна умноженной в /2 раз длительности периода частоты ,т.е. т-число интервалов единицу вр©У18ни,которое соответствует частоте появления импульсов на выходе делителя I и равно отношению .-&... Отсюда следует,что с- -г JL Л 8ых N Коэффициент деления частоты делителей I и 6 выбирается из следующих условий.Поскольку мгновенная частота последовательности Ff меняется,необходимо чтобы был известен некоторый минимальный интервал времени т ,в течение которого среднее значение частоты Гг должно быть не менее,чем на 2 Гц меньше среднего значения частоты F.

Торда

f MUH- lcpT

Однако в предлагаемом устройстве происходит задержка на ./ импульсов последовательности F, начала сигналов.Для повышения быстродействия подключают к делителю I вход запуска так,чтобы сигнал на этом входе переводил делитель в состояние,соответствующее насчету числа шпульсов,на единицу меньшего,чем выбранный коэффициент деления.В этом случае первый же импульс последовательности ,следу1щий за сигналсш запуска,поступает на выход делитеад и начинает работу устройства.

ПРЕДУШТ ИЗОБРЕТЕНИЯ Частотно-импульсное множигельно-делительное устройство, содержащее первый и второй делители частоты,первый триггер и первую схевяу совпадения,причем счетный вход первого делителя частоты соединен с первым входсяи устройства;единичный выход первого триггера соединен с управляющим входом первой схемы совпадения, информационный вход которой соединен со вторым входом устройства,а ее выход соединен с выходом устройства,отличающееся тем, что,с целью повышения точности работы,в него введены второй триггер, вторая и третья схемы совпа0 дешю; причем И1ход первого делителя частоты соединен с единичным входсяй второго триггера,нулевой выход которого соединен с нулевым входом второго делителя частоты,

5 М1ход(1 второй схемы совпадения

и нулевым входе первого триггера; .. единичный выход второго триггера соединен с управляшщм входом третьей схемы совпадения,инфораа0 ционннй ВХОД, которой соединен с iтретьим входом устройства,а ее :выход соединен с единичным входом Первого триггера,информационным входш второй схемы совпадения и

5 счетным входмя второго делителя частоты;выход второго делителя частоты соедагаен с управляющим .входсш второй совпаденрш.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для коррекции числа импульсов по входному параметру | 1984 |

|

SU1187146A2 |

| Устройство для коррекции числа импульсов по параметру | 1984 |

|

SU1228118A1 |

| Устройство для преобразования разности частотно-импульсных сигналов в код | 1976 |

|

SU750728A1 |

| Устройство для измерения временныхиНТЕРВАлОВ | 1979 |

|

SU828170A1 |

| МНОЖИТЕЛЬНО-ДЕЛИТЁЛЬНОЕ УСТРОЙСТВО | 1968 |

|

SU218531A1 |

| Делитель частоты с переменным коэффициентом деления | 1990 |

|

SU1812636A1 |

| МНОГОКАНАЛЬНЫЙ ИНФРАНИЖОЧАСТОТНЫЙ ЦИФРОВШ КОРРЕЛЯТОР | 1972 |

|

SU433486A1 |

| Устройство для генерации пачек импульсов | 1984 |

|

SU1234953A1 |

| Устройство для регулирования скорости прядильной машины | 1982 |

|

SU1044576A1 |

| Формирователь пачек импульсов | 1983 |

|

SU1150738A1 |

Авторы

Даты

1974-09-25—Публикация

1972-05-22—Подача