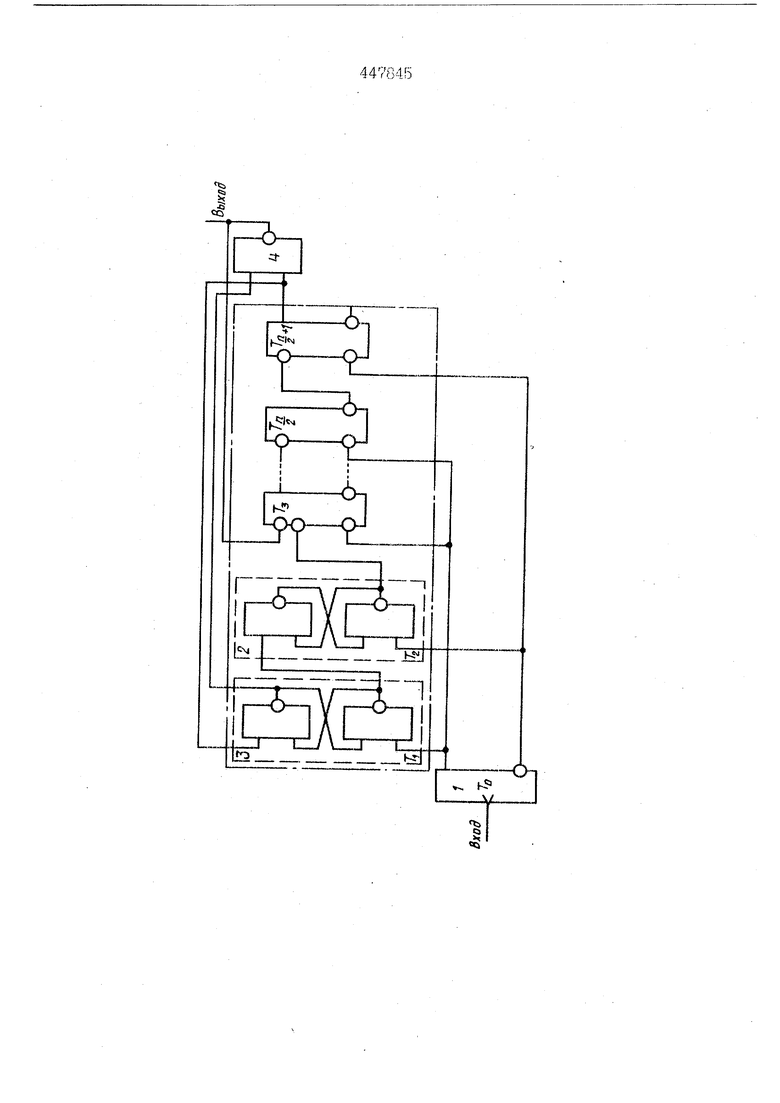

Изобретение относится к импульсной технике и может быть использовано в импульсных логических устройствах рациоаппаратуры различного назначения. Известен распределитель импульсов на потенциальных элементах, который может быть использован в качестве делителя частоты. Цель изобретения - повысить надежность устройства. Для этого единичный выход последнего разрданого триггера соединен с единичным входом первого оазоянного триггера, входы схеиы совпадения и иввержирования подключены к единичным выходам первого и последнего разрядных триггеров, а выход схемы совпадения и инвертирования подвл чей к единичный входам всех нечехных разрядных триггеров, кроме пер вого и последнего нечетного.. На чертеже изображена логическая схема предлагаемого делителя. Он имеет триггер-1 со счетными входом, регистр сдвига 2, состоящий из jix j разрядных триггеров 3 с Установочными входами //j,коэадициент деления делителя частоты, равный 2,6,10.14,18 и т.д./, схему совпадения и инвертирования 4. Триггер I со счетным входом переключается по счетному входу входными импульсами и формирует на своих выходах управляющие инверсные уровни /уровень нуля и уровень единицы. Регистр сдвига 2 состоит из j 4-/разрядных триггеров 3 с установочными входами. Нулевые входы нечетных разрядов регистра подключены к единичному выходу триггера I, аналогичные входы четных разрядов регистра - к нулевому выходу триггера . Передача единицы из разряда в разряд производится с нулевого выхода каящого предыдущего разряда

триггера/ на единичный вход каждого последующего разряда /триггера/ в кнверсном коде.

Схеш совпадения и инвертйро вания 4 цредназначена для формщ)о ванйя выходного сигнала и сигнала установки ед1шичного состояния всех нечетных разрдцных триггеров., крош первого и последнего нечетного. Входы схемы совпадения и ш«вертирования 4 подключены к единить ним выходш разрядных триггеров Т

и соответственно. Бнход иХбмы совпадения и инвертирования предназначен ддл формирования ыь ходного сигнала делителя частоты и одновременно подключается на единичные входы всех нечетных разрядных триггеров, кроме первого Т, и- последнего нечетного Ъ. , для осу1цествления автоматической установки делителя частоты в исходное состояние после включения питания, сходное состояние J устанавливаемое при появлении первого Btt.одного иглпульса, - разрядные триг геры 3 и триггер со счетныт; входом /I установлены в едршичное состоя 1И8 о В этом состоянии с eдиIiичнoгo выхода последнего разрядного триггера Ti.,, регистра на единичный

г7 I

вход трипераТ подается высокий уровень. соответствую ций отсутст- Бик) сигнала. 1 зштеры четных разрадоБ регистра блокхфсвшы нулевым ypcjE.ieMs так как трратер i установлем Б единичное состояние. Ш оба входа схеш-j совпадения и инверти)ования 4 подаются высокие уровниf в результате чего на ее выхсм/.е нормируется нулевой уровенг осущестБляюощй автоматическую устанСБку исходного состояния, если в .Mui-iCHT вклвэченкя питания цроизоц.г,ет уотаноиш разрядных Т|)иг1еров в ненужные нам случайнне состояния.

Первий входной импульс перек.Ш4авт триггер Т из единичного соотоямия в fiyлевое, который меняет у1 равл -1ющие уровни. Теперь нулеьоп урошнь подан на нечетные ргдзрнли регистра, а единич11Ый уровень - на четные. Триггеры четных разря,д(лз регистра после снятия оло а1 и:лки устанавливаются в еди.

ййчное состояние , lia единичном выходе перього разряда регистра устанавливается нулевой уровень. На выходе схемы совпа.деншг и инверти ованйя устанавливается единичным уровень, соответствующий отсутствию выхо.дного сшнаж. Второй входной тшулъс переключает трршгер из нулевого состояния в единичное, в результате чего происходит смена управляющих уровней,, которые блокируют четние и снимают блокщювку с нечетных разрядов триггеров/ регистра.Лервый разряд /третгер/ Т регистра устанавливается в нулевое состояние и формирует на своем нулевом входе единичный уровень, второй подготавливает второй разряд /триггер/

Та к установленшэ в нулевое состояние на следующем такте,

Аналогичное переключение разрядов происходит с каяшым входным импульсом делителя частоты. С единичного выхода последнего разряда /тржтера/f0..4 на единичный выход первого разрядного тржчераТ будет продолжать поступать единичный уровень, соответствующий отсутствию сигнала, что подхотавлквает первый разрядный тржтер Т к установлению нулевых состояний до тех пор, пока не установится нулевое состояние в послед яем разрядном триггере. С установлением нулевого СОСТОЯН.ИЯ последнего разрядного триггера Jn, .

на единичный вход первого разрядного триггера TI подается нулевой уровень, устанавливающий его в единичное состояние „. Нулевой уровень на единичном выходе разрядного триггера д. будет сохраняться до , пока не установится в единичное состояние разрядный триггер Тзг который подfjoTOBHT разрядный триггер т v ,

TL

К приему единицы путем изменения единичного уровня на нулевой уро-. В

ень на его единичном выходе течение этого такта единичные вы ходы первого и последнего разгЯ дов регистра будут (.ормировать единичные уровни. При этом совпа Дании сигналов схема совпадения

и инвертирования 4 сформирует на своем выходе нулевой уровень со ответствующий выходному сигналу. Это произойцет входном импульсе делителя частоты.

Частота, следования отрицательных импульсов выходного сигяаг ла Bfipas ниже частоты следования импульсов входного сигнала, длительность выходного импульса равна периоду повторения импульсов входного сигнала.

ПРШИЕТ ИЗОБРЕТЕНИЯ

Делитель частоты на потенциальных элементах содержащий разрядные триггеры с раздельными вхо-

дами и счетный триггер, единичный и нулевой выходы которого соотве.тотвенно подключены к нулевым входам всех нечетных и четных разрядных триггеров, схему совпадения и инвертирования, отличающийся тем, что, с целью повышения надежности единичный выход последнего разрядного триггера

соединен с единичным входом первого разрядного триггера, входы схемы совпадения и инвертирования .подключены к единичным выходам первого и последнего разрядных триггерров а выход схемы совпадения и инвертирования подключен к единичным входам всех нечетных разрядных триггеров, кроме первого и последнего нечетного.

.

| название | год | авторы | номер документа |

|---|---|---|---|

| РАСПРЕДЕЛИТЕЛЬ ИМПУЛЬСОВ НА ПОТЕНЦИАЛЬНЫХ ЭЛЕД1ЕНТАХ | 1973 |

|

SU364109A1 |

| Делитель частоты следования импульсов | 1985 |

|

SU1277387A2 |

| Делитель частоты с переменным коэффициентом деления | 1988 |

|

SU1547057A2 |

| Асинхронное устройство для определения четности информации | 1978 |

|

SU767765A2 |

| Делитель частоты следования импульсов | 1987 |

|

SU1443169A1 |

| Устройство задержки сигналов | 1982 |

|

SU1015491A1 |

| Симметричный делитель частоты импульсов | 1982 |

|

SU1089763A2 |

| Устройство для управления шаговым двигателем | 1977 |

|

SU663058A1 |

| Делитель частоты следования импульсов | 1982 |

|

SU1045400A1 |

| Делитель частоты следования импульсов | 1983 |

|

SU1128390A1 |

Авторы

Даты

1974-10-25—Публикация

1972-11-27—Подача