1

Изобретение относится к вычислительной технике и может использоваться для обнаружения ошибок нечетной кратности при передаче и кранении цаннык в двоичном коде.

По основному авт. св. № 552609 известно асинхронное устройство для определения четности информации, содержащее регистр, разрядные входы которого являются входами устройства, элемент ИЛИ, .выходом соединенный со счетным входом триггера, выходы которого -соединены :с первыми входами двух элементов И, выходы элементов И являются входами устройства, второй и третий элементы ИЛИ, элементы И,.второй триггер и элемент задержки, причем входы устройства соединены с входами второго элемента ИЛИ, выход которого соединен с входом элемента задержки и с входом установки вединицу второго триггера, выходы второго триггера и элемента за- держ1си соединены с входами третьего элемента И выход которого соединен с

одним из входов второго элемента ИЛИ и с первыми входами четвертого и пятого элементов И, вторые входы которых соединены с выходами первого разряда регистра, выходы питого и последующих нечетных элементов И соединены с первыми входами двух следующих элементов И, вторые входы которых соединены с выходами следующего разряда регистра, выходы четвертого и последующих четных

10 элементов И соединены с входами первого элемента И и с входами установки, в нуль соответствующего разряда регистра, выход последнего элемента И соединен с.вторыми входами.первых двух элемен15тов И, выходы которых соединены с входами третьего элемента ИЛИ, выход третьего элемента ИЛИ соединен с входами установки в нуль первого и второго триггеров.

20

Однако известное устройство имеет низкое быстродействие.

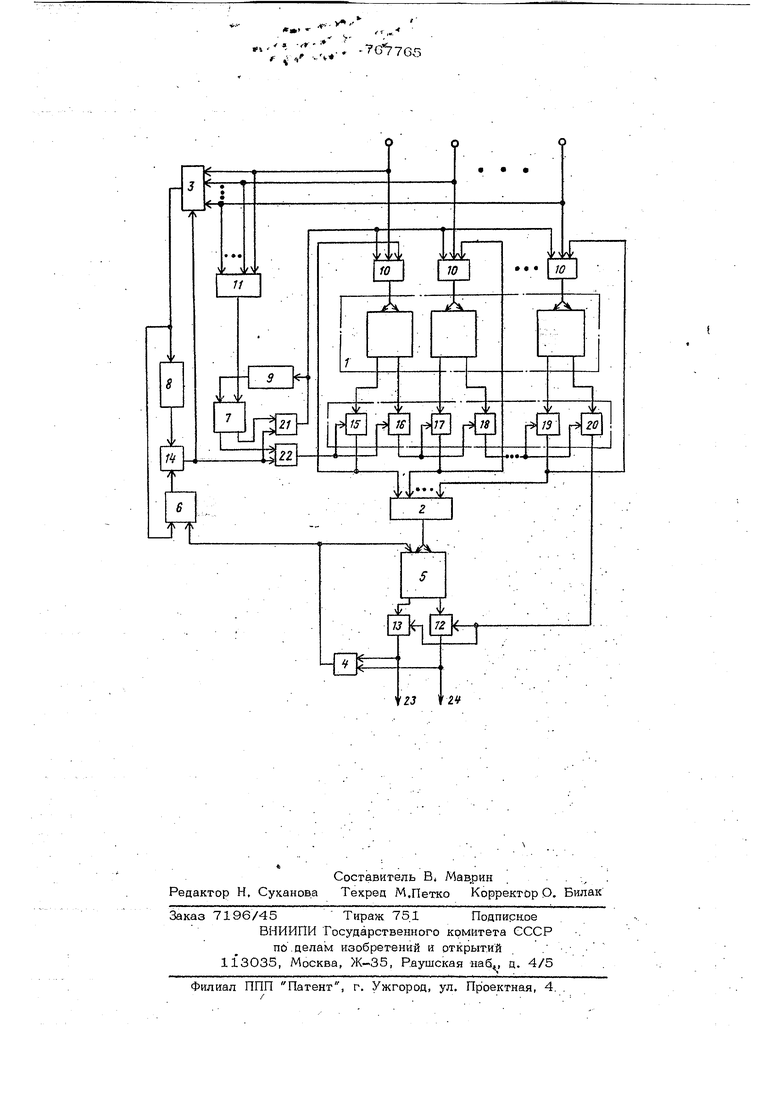

Цель изобретения - повышение быстродействия. 3 7 Для этого в устройство введены объе диненные по первому входу дополнительные элементы ИЛИ и пороговый блок, а также третий триггер, дополнительный элемент задержки и два дополнительных элемента И, к объединенным первым вхо дам которых подключен выход третьего элемента И, а к вторым входам дополнительных элементов И подключены соответственно единичный и нулевой выходы третьего триггера, к входам установки в единицу и в нуль которого подключены соответственно выходы порогового блока и дополнительного элемента задержки, вход которого объединен с выходом первого дополнительного элемента И и вторыми входами дополнительных элементов ИЛИ, третьи и первые входы которых соответственно подключены к входам перво го и второго элементов ИЛИ, а выходы дополнительных э лементов ИЛИ подключе ны к счетным входам соответствующих разрядов регистра, при этом выход второго дополнительного элемента И подклю чен к вторым входам четвертого и пятого элементов И. На чертеже приведена структурная электрическая схема предложенного устройства. Асинхронное устройство для определения четности информации содержит регистр 1, первый 2, второй 3, третий 4 . элементы ИЛИ, первый 5, второй 6 и третий 7 триггеры, элементы задержки 8 и 9, дополнительные элементы ИЛИ 10, пороговый блок 11, элементы И 12 20 и два дополнительных элемента И 21 22. Устройство работает следующим обра зом. В исходном состоянии триггеры 5находятся в нулевом состоянии. Входная .М -разрядная кодовая комбинация поступает в параллельном виде на входы устройства и через элементы ИЛИ 10 записывается в регистр 1. Одновременно все входные импульсы подаются на элемент ИЛИ 3 и пороговый блок 11. С выхода элемента ИЛИ 3 импульс, соответствующий моменту записи, поступает на вход элемента задержки 8 и на единичный вход триггера 6. Последний уста навливается в единичное состояние и открывает элемент И 14. Через время С соответствующее времени эадернски элемента 8, импульс через открытый элемент И 14 поступает на вход элемента ИЛИ 3 и входы элементов И 21 к 22. 5 Пороговый блок 11 реализует функI,если ё q. П. . о, если .S ац « i-1 И - разрядность числа; а - 1-й разряд входной кодовой комбинации. Р 1, то триггер 7 устанавливается в единичное состояние. Следовательно, открыт элемецт И 21, им. пульс с которого поступает на вход элемента задержки 9 и на входы элементов ИЛИ 10. Кодовая комбинация, записанная в регистр 1, инвертируется. Через время 2. .Z. выхода элемента задержки 9 на вход триггера 7 поступает импульс, устанавливающий триггер 7 в нулевое состояние. Второй импульс, поступающий с .элемента И 14, открывает элемент И 22.Элементы И 15, 17, 19 подсоединены к единичным выходам соответствующих раз-ч рядов регистра 1, импульс через них npoi ходит лишь в том случае, когда в разряде записана 1. Наоборот, через элементы И 16, 18, 20 импульс проходит лишь тогда, когда в соответствующем разряде регистра 1 записан О. Если в первом разряде регистра 1 записана 1, то импульс с выхода элемента И 22 поступает через элемент И 15 на вход элемента ИЛИ 2. Одновременно с выхода элемента И 15 импульс через элемент ИЛИ. 10 подается на счетный вход первого разряда регистра 1. Следующий импульс с элемента И 22 вновь подается на входы элементов И 15 и 16, однако теперь уже первый разряд регистра 1 находится в нулевом состоянии и этот импульс проходит через элемент И 16 на вход элементов И 17 и 18. Элементы И 17 и 18 работают аналогично элементам И 15 и 16. Если во втором разряде регистра 1 записана I, то импульс проходит через элемент И 17 на элемент, ИЛИ 2 и через элемент. ИЛИ 10 - на счетный вход второго разряда регистра 1, а следующий импульс - через элемент И 18. Если же во в.торЬм разряде регистра 1- записан О, то импульс сразу поступает на элемент И 18 и т. д. С выхода элемента ИЛИ 2 импульсы, соответствующие символам во входной кодовой комбинации, поступают на 57 счетный вход триггера 5. С выхода последнего элемента И 20 импульс попадает на входы элементов И 12 и 13, Если число единиц в кодовой комбинации четное, то импульс проходит через элемент И 13 на выход 23, а если нечетное, то импульс проходит через элемент И 12 на выход 24. Через элемент ИЛИ 4 любой из этих импульсов поступает на входы установки в нуль триггеров 5-7, это приводит схему в исходное состояние. Если при приеме входной кодовой ком бинации с выхода порогового блока 11 поступает , нулевой сигнал ( F « О), то инвертирования содержимого регистра 1 не производится и первый импульс сразу проходит через элемент И 22. Далее уст ройство работает аналогично рассмотренному случаю. В случае, если И нечетно, необходимо выход порогового блока 11 соединить с дополнительным входом элемента ИЛИ 2. Это позволит скорректировать начальное состояние триггера 5 при инвертировании содержимого регистра 1. Пороговый блок 11 реализует в .этом случае функцию 2,, если Ы 2 а „ ин о,если ,Среднее время декодирования в предлагаемом устройстве меньше, чем в известном, и определяется количеством единиц в разрядах регистра 1, которое всегда будет меньше или равно h|2. В 5 случае, если все кодовые комбинации равновероятны и И четно, ср2(,, tiMK-t-...-V -С |т.С(.)1:.СХ|„. - C{,)...+ Cj tjc; Формула изобретения Асинхронное усгройсгво для определения четности информации по авт. св. № 552609, отличающееся тем, что, с целью повышения быстродействия, в него введены объециненныа по первому входу дополнительные элементы ИЛИ и пороговый блок, а также третий триггер, дополнительный элемент задержки и два дополнительных элемента И, кобъединенным первым входам когорых подключен выход третьего элемента И, а к вторым входам дополнительных элементов И подключены соответственно единичный и нулевой выходы третьего триггера, к входам установки в единицу и в нуль которого подключены соответственно выходы порогового блока и дополнительного элемента задержки, вход которого объединен с выходом первого дополнительного элемента И и вторыми входами дополнительных элементов ИЛИ, третьи и первые входы которых соответственно подключены к входам первого и второго элементов ИЛИ, а выходы дополнительных элементов ИЛИ подключены к счетным входам соответствующих разрядов регистра, при этом выход второго дополнительного элемента И подключен к BTof)biM входам четвертого и пятого элементов И. ..

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для определения четности информации | 1981 |

|

SU1013959A1 |

| Асинхронное устройство для определения четности информации | 1973 |

|

SU552609A1 |

| Устройство для мажоритарного выбора сигналов | 1988 |

|

SU1711167A1 |

| Устройство для мажоритарного выбора сигналов | 1989 |

|

SU1656539A1 |

| Устройство для приема сигналов с избыточностью | 1983 |

|

SU1128281A1 |

| Способ многодорожечной цифровой магнитной записи и устройство для его осуществления | 1988 |

|

SU1606996A1 |

| Устройство для контроля параллельного двоичного кода на четность | 1982 |

|

SU1056199A1 |

| Устройство для контроля двоичного кода на нечетность | 1981 |

|

SU1012261A1 |

| Устройство для контроля параллельного двоичного кода на четность | 1981 |

|

SU999057A1 |

| Устройство для мажоритарного выбора сигналов | 1988 |

|

SU1619278A1 |

Авторы

Даты

1980-09-30—Публикация

1978-07-31—Подача