1

Изобретение относится к области вычислительной техники и может быть использовано при построении цифровых вычислительных машин (ЦВМ) на основе больших интегральных схем.

Известно арифметическое устройство, содержаш,ее блок управления, сумматор, регистры операнд и результата.

Недостатком известных устройств является то, что ДЛЯ вычисления коэффициентов многочлена, равного произведению многочлена

пт

2 YiX на многочлен У VjZ, необходимо не

менее т-п раз выполнить команду сложения и (n-j-l) (m-f-1) раз команду умножения, для чего потребуется m-n(/n+,l) (л+1) раз обратиться к запоминающему устройству, что приводит к значительным затратам времени, необходимого для вычислений.

С целью сокращения времени вычисления, в устройство введены блок сдвига, логические схемы «И, первые входы которых соединены с выходами младших разрядов регистров коэффициентов первого многочлена, а вторые входы - с выходами блока управления и управляющими входами блока сдвига коэффициентов второго многочлена; выходы схем «И подключены к входам логической схемы «ИЛИ, выход которой соединен с входами разрешения выдачи регистров коэффициентов

второго многочлена, выходы которых соединены с разрядными входами блока сдвига коэффициентов второго многочлена, выходы которого подключены ко вторым входам сумматоров.

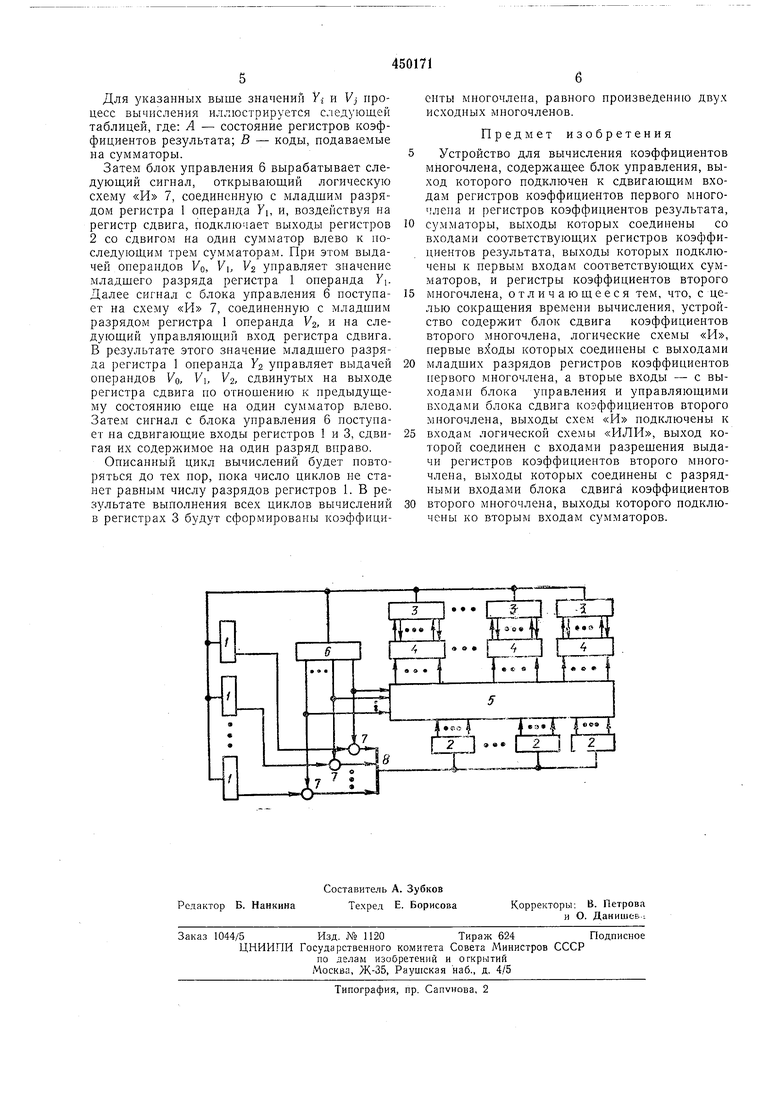

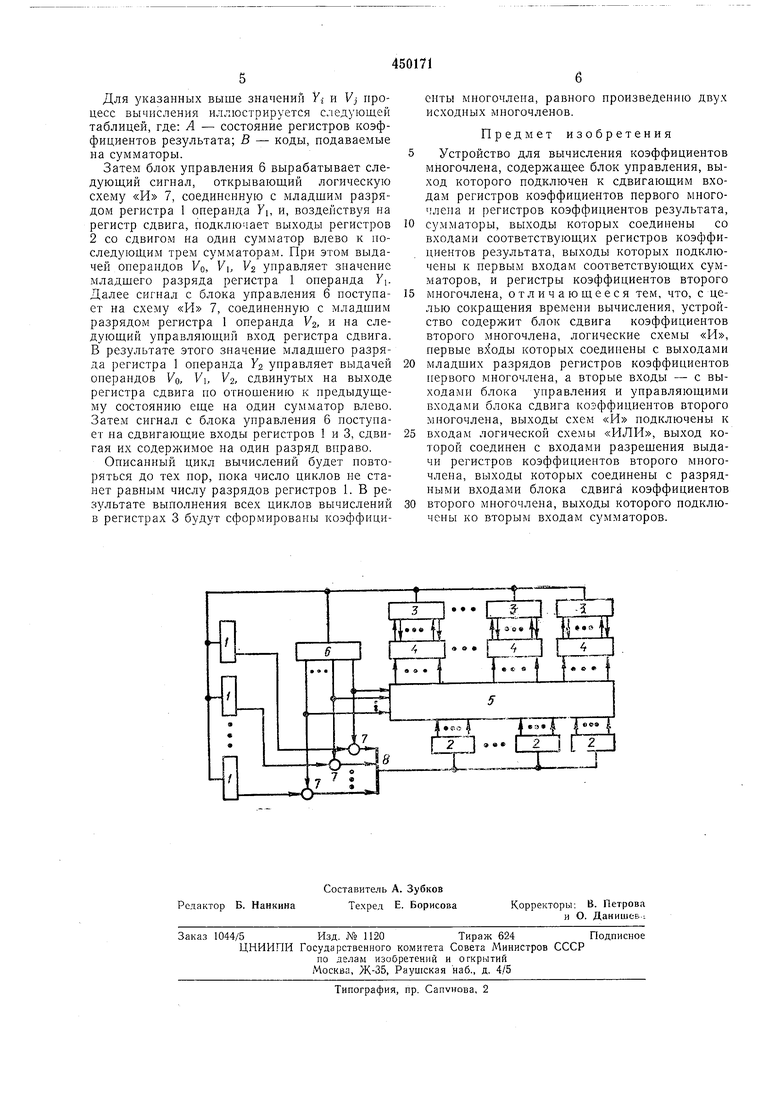

На чертеже представлена блок-схема устройства, где: 1 - регистры коэффициентов первого многочлена; 2 - регистры коэффициентов второго многочлена; 3 - регистры коэффициентов результата; 4 - сумматоры; 5-

регистр сдвига; 6 - блок управления; 7 -

логические схемы 8 - логическая схема

«ИЛИ.

В регистры 1 заносятся коэффициенты первого многочлена Vi, в регистры 2 - коэффициенты второго многочлена. Количество регистров 3 коэффициентов результата и количество сумматоров 4 равно n+m-f-l. Каждый из сумматоров 4 образует с соответствующим

регистром 3 накопительный сумматор.

Работу устройства рассмотрим на следуюш,ем примере.

Пусть необходимо вычислить значение коэффициентов многочлена, равного произведению (Зх - -2х+4) (х +Зх-}-5). Следовательно, Уо 4, У1 2, У2 3, , Vi 3, .

При этом операнды УО, У и У2 перед началом вычислений записываются в регистры 1, операнды УО, Vj и Vz - в регистры 2. Регистры 3, количество которых в данном случае равно 5, устанавливаются в нулевое состояние. С началом работы устройства блок управления 6 вырабатывает сигнал, открывающий логическую схему «И 7, соединенную- с младшим разрядом регистра 1 операнда УО и,5 воздействуя на регистр сдвига, подключает выходы регистров 2 к трем крайним справа сумматорам. При этом значение младшего разряда регистра операнда УО управляет выдачей операндов VQ, Vi, Vz из регистров 2.

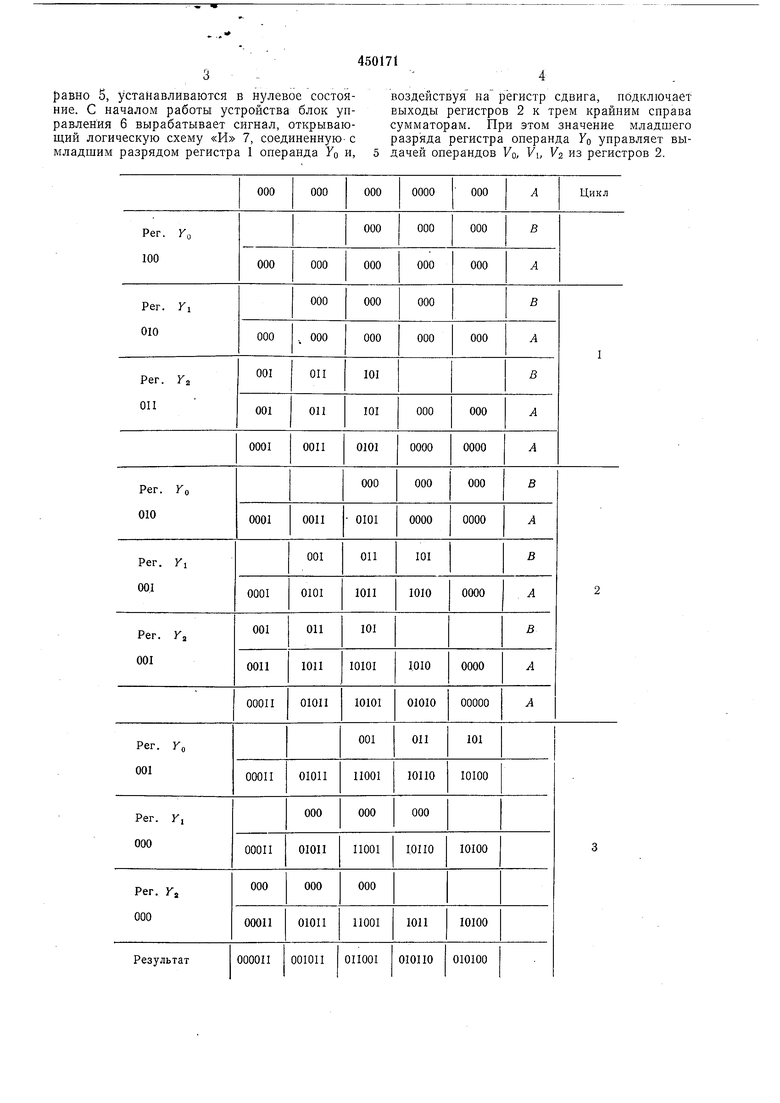

Для указанных выше значений Уг и Vj процесс вычисления иллюстрируется следующей таблицей, где: А - состояние регистров коэффициентов результата; В - коды, подаваемые на сумматоры.

Затем блок уцравления 6 вырабатывает следующий сигнал, открывающий логическую схему «И 7, соединенную с младшим разрядом регистра 1 операнда УЬ и, воздействуя на регистр сдвига, подклю шет выходы регистров 2 со сдвигом на один сумматор влево к последующим трем сумматорам. При этом выдачей операндов Vo, V, Vz управляет значение младщего разряда регистра 1 операнда У. Далее сигнал с блока управления 6 поступает на схему «И 7, соединенную с младшим разрядом регистра 1 операнда V2, и на следуюший управляющий вход регистра сдвига. В результате этого значение младщего разряда регистра 1 операнда УЗ управляет выдачей операндов VQ, V, Уг, сдвинутых на выходе регистра сдвига по отношению к предыдушему состоянию еще на один сумматор влево. Затем сигнал с блока управления 6 поступает на сдвигающие входы регистров 1 и 3, сдвигая их содержимое на один разряд вправо.

Описанный цикл вычислений будет повторяться до тех пор, пока число циклов не станет равным числу разрядов регистров 1. В результате выполнения всех циклов вычислений в регистрах 3 будут сформированы коэффициенты многочлена, равного произведению двух исходных многочленов.

Предмет изобретения

Устройство для вычисления коэффициентов многочлена, содержащее блок управления, выход которого подключен к сдвигающим входам регистров коэффициентов первого многочлена и регистров коэффициентов результата, су.мматоры, выходы которых соединены со входами соответствующих регистров коэффициентов результата, выходы которых подключены к первым входам соответствующих сумматоров, и регистры коэффициентов второго многочлена, отличающееся тем, что, с целью сокращения времени вычисления, устройство содержит блок сдвига коэффициентов второго многочлена, логические схемы «И, первые которых соедипены с выходами младщих разрядов регистров коэффициентов первого многочлена, а вторые входы - с выходами блока управления и управляющими входами блока сдвига коэффициентов второго многочлена, выходы схем «И подключены к входам логической схемы «ИЛИ, выход которой соединен с входами разрещения выдачи регистров коэффициентов второго многочлена, выходы которых соединены с разрядными входами блока сдвига коэффициентов второго многочлена, выходы которого подключены ко вторым входам сумматоров.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления значений полиномов вида | 1972 |

|

SU451088A1 |

| Дифференцирующее устройство | 1974 |

|

SU517894A1 |

| ЦИФРОВОЙ ИНТЕГРАТОР | 1973 |

|

SU369590A1 |

| Устройство для умножения элементов конечных полей | 1983 |

|

SU1124291A1 |

| Устройство для цифровой обработки сигналов | 1985 |

|

SU1336028A1 |

| Устройство для умножения | 1976 |

|

SU651341A1 |

| Многоканальный преобразователь аналог-код | 1981 |

|

SU978339A1 |

| Устройство для умножения многочленов | 1979 |

|

SU783791A1 |

| Вычислительное устройство с микропрограммным управлением | 1970 |

|

SU439816A1 |

| ЛОГИЧЕСКОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1973 |

|

SU386444A1 |

Авторы

Даты

1974-11-15—Публикация

1973-03-09—Подача