Изобретение относится к вычислительной технике и быть применено, например, в цифровых вычислительных машинах (ЦВМ), ностроениых на основе, больших интегральных схем.

Известно вычислительное устройство, предназначенное для вычисления выражени вида

+ Yn-iX- + ...+ 1, +

Оно содержит блок управления, регистр онерандов, регистр результатов и схемы «И.

Вычисления с помощью этого устройства выражений указанного вида сводится к формированию произведений YiX и к последуюш,ему их сложению (f 1, 2,...). Формирование произведений УД производится путем i- 1-кратного умножения операнда X на себя п на операнд Yi.

В специализированных ЦВМ, где не используются принципы программного управления, вычислять выражения вида + УД1 + YoX° с помошью указанного устройства невозможно, так как в таких ЦВМ отсутствуют команды и, следовательно, нельзя свести вычисления к многократному умножению и сложению. В ЦВМ с программным управлением при вычислении выражений УпХ + + + . . . + У + с помощью указанного устройства необходимо не менее п раз выполнить команду умножения и п раз

команду сложения, для чего следует 2п раз обратиться к запоминающему устройству ЦВМ. Это обуславливает как дополнительиые затраты оборудования, необходимого для хранения программы вычислений, так и дополнительные затраты времени на обращение к запоминающему устройству.

Цель изобретения - увеличение скорости вычисления значений полиномов вида

i

i л о

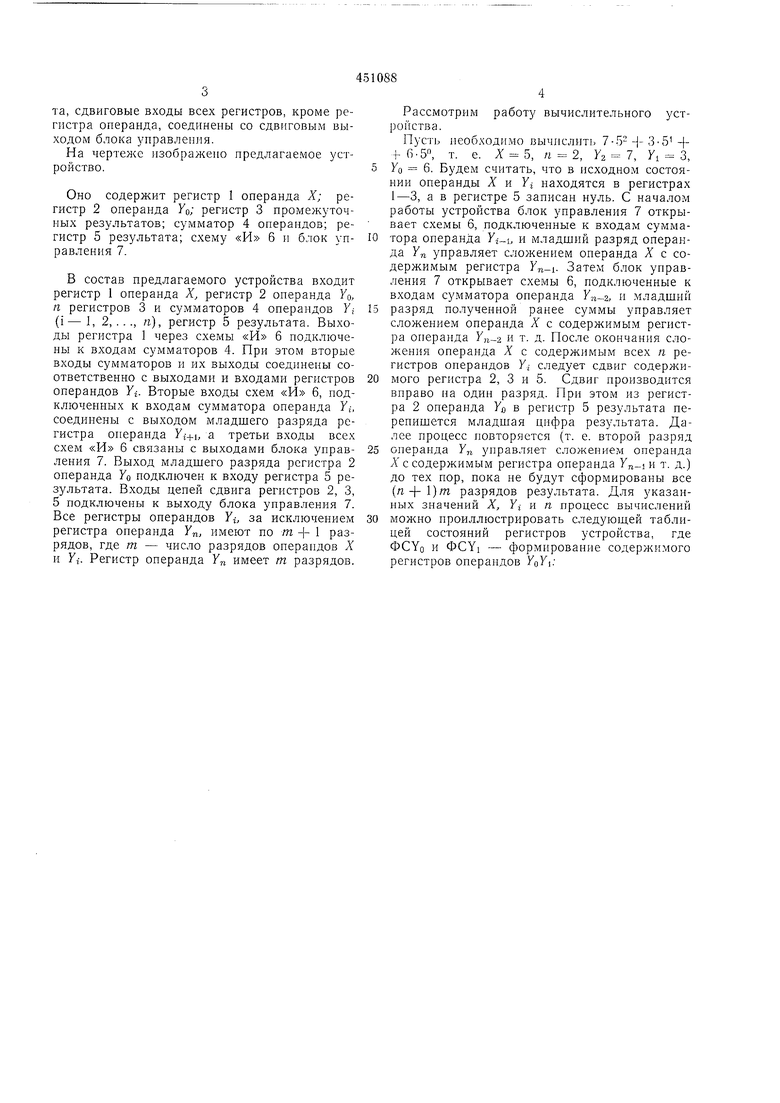

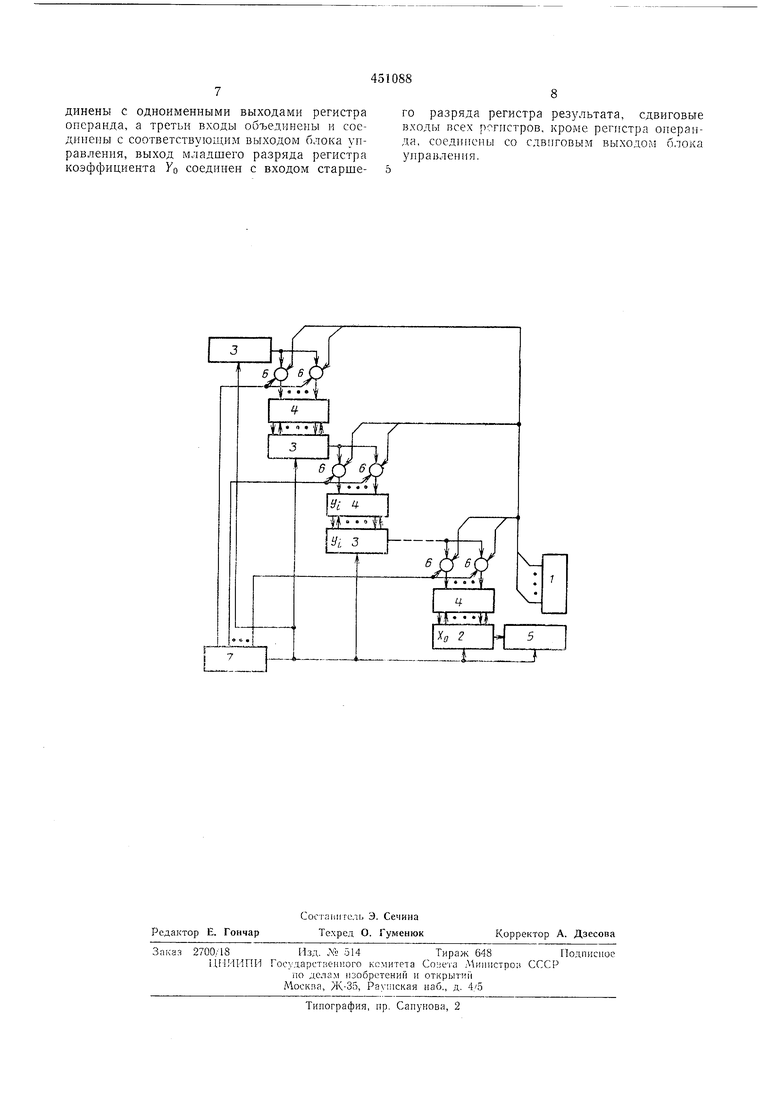

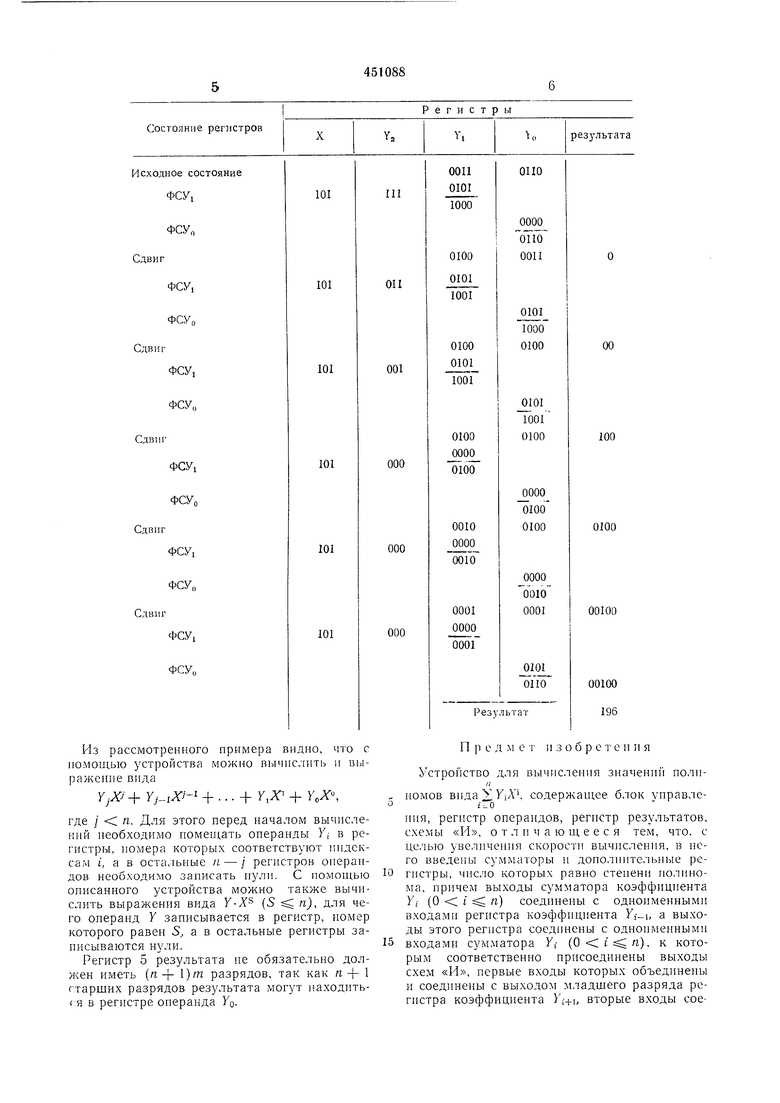

Сущность изобретения заключается в том, что в него введены сумматоры и дополнительные регистры, число которых равно стеиени полинома, причем выходы сумматора коэффициента У, (О t п) соединены с одноименными входами регистра коэффициента а выходы этого регистра соединены с одноименными входами сумматора Уг (О t п), к которым соответственно присоединены выходы схем «И, первые входы которых объединены и соединены с выходом младщего разряда регистра коэффициента Уг+1, вторые входы соединены с одноименными выходами регистра операнда, а третьи входы объединены и соединены с соответствующим выходом блока управления, выход младшего разряда регистра коэффициента УО соединен со входом старшего разряда регистра результата, сдвиговые входы всех регистров, кроме регистра операнда, соединены со сдвиговым выходом блока уиравлеиия. На чертеже изображеио иредлагаемое устройство. Оно содержит регистр 1 операнда X; регистр 2 операнда FO; регистр 3 промежуточных результатов; сумматор 4 операндов; регистр 5 результата; схему «И 6 и блок управления 7. В состав предлагаемого устройства входит регистр 1 операнда X, регистр 2 онеранда УО, я регистров 3 и сумматоров 4 операндов У, (i-1, 2,..., п), регистр 5 результата. Выходы регистра 1 через схемы «И 6 нодключены к входам сумматоров 4. При этом вторые входы сумматоров и их выходы соединены соответственно с выходами и входами регистров операндов Yi. Вторые входы схем «И 6, подключенных к входам сумматора онеранда У;, соединены с выходом младшего разряда регистра операнда Уг+ь а третьи входы всех схем «И 6 связаны с выходами блока управления 7. Выход младшего разряда регистра 2 операнда УО нодключен к входу регистра 5 результата. Входы ценей сдвига регистров 2, 3, 5 подключены к выходу блока управления 7. Все регистры операндов Yi, за исключением регистра операнда У„, имеют по т -|- 1 разрядов, где т - число разрядов операпдов X н Yi. Регистр онеранда УП имеет т разрядов. Рассмотрим работу вычислительного устройства. Пусть необходимо вычнслнть 6-5, т. е. Л 5, п 2, Уг 7, У 3, УО 6. Будем считать, что в исходном состоянии операнды X и Yi находятся в регистрах 1-3, а в регистре 5 записан нуль. С началом работы устройства блок управления 7 открывает схемы 6, подключенные к входам сумматора операнда Уг-ь н младший разряд операнда УЯ унравляет сложением операнда X с содержимым регистра Yn-i- Затем блок унравления 7 открывает схемы 6, подключенные к входам сумматора онеранда Уп-г, и младший разряд полученной ранее суммы управляет сложением операнда X с содержимым регистра онеранда Yn-z и т. д. После окончания сложения операнда X с содержимым всех п регистров операндов У.; следует сдвиг содержимого регистра 2, 3 и 5. Сдвиг производится вправо на один разряд. При этом из регистра 2 операнда Уд в регистр 5 результата неренишется младшая цифра результата. Далее процесс повторяется (т. е. второй разряд онеранда УП управляет сложением операнда /Y с содержимым регистра операнда У„-1 и т. д.) до тех пор, пока не будут сформированы все )т разрядов результата. Для указанных значений X, Y и п процесс вычислений можно проиллюстрировать следуюшей таблицей состояний регистров устройства, где ФСУо и OCYi - формпрованне содержимого регистров операндов УоУь

Регистры

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления коэффициентов многочлена | 1973 |

|

SU450171A1 |

| Устройство для вычисления выражений вида | 1973 |

|

SU444193A1 |

| УСТРОЙСТВО ДЛЯ ВО313ЕДЕНИЯ В СТЕПЕНЬ | 1972 |

|

SU425175A1 |

| Устройство для перемножения многочленов | 1973 |

|

SU495663A1 |

| Устройство для вычисления полиномов второй степени | 1980 |

|

SU920714A1 |

| БИБЛИОТЕКА | | 1971 |

|

SU314204A1 |

| Устройство для вычисления полиномиальной функции от аналогового аргумента | 1990 |

|

SU1737444A1 |

| Устройство для реализации алгоритма Волдера | 1983 |

|

SU1115049A1 |

| Устройство для умножения чисел | 1990 |

|

SU1714595A1 |

| Специализированный процессор для вычисления элементарных функций | 1985 |

|

SU1330627A1 |

Из рассмотренного примера видно, что с номощыо устройства можно вычислить и выражение вида

УД/ + + ... + У,Х + Vo,

где / п. Для этого перед началом вычислений необходимо номещать онеранды У; в регистры, номера которых соответствуют индексам i, а в остальные п - / регистров онерандов необходимо записать нули. С номощыо описанного устройства можно также вычнслнть выражения внда У- (5 п), для чего операнд У записывается в регистр, помер которого равен 5 а в остальные регнстры заиисываются нули.

Регистр 5 результата не обязательно должен иметь (п + )т разрядов, так как п+ 1 старших разрядов результата могут находнть( я в регистре операнда УОПро д м е т и 3 о б р е т е п и я Устройство для вычисления значений ноли/;

номов вида V yiA, содержан1ее блок управле(1-0

ПИЯ, регистр операндов, регистр результатов, схемы «И, отличающееся тем, что, с целью увелнчения скорости вычнслення, в него введены сумматоры н дополнительные регистры, число которых равно степени полинома, причем выходы сумматора коэффицнента У; (О t 5 п) соединены с одноименными входами регистра коэффициента У,--1, а выходы этого регистра соединены с одноименными входами сумматора У,- (О t : га), к которым соответственно присоединены выходы схем «И, первые входы которых объединены и соединены с выходом младщего разряда регистра коэффициента У;+ь вторые входы соединены с одноименными выходами регистра операнда, а третьи входы объединены и соединены с соответствующим выходом блока уиравления, выход младшего разряда регистра коэффициента УО соединен с входом старшего разряда регистра результата, сдвиговые в.ходы Бсех регистров, кроме регистра онеранда, соединены со сдвиговым выходом блока унравлення.

, 3

J

Авторы

Даты

1974-11-25—Публикация

1972-07-03—Подача